一种OPA线性offset校准电路的制作方法

本发明涉及运算器偏移校准领域,尤其涉及一种opa线性offset校准电路。

背景技术:

1、当前针对运算器偏移校准主要有两种方式:一、二进制校准;以及二、译码校准。

2、采用二进制校准具有结构简单,易实现,器件使用少的优点,如图4所示,但同时trim控制位必须负端和正端分开,会导致浪费x-1位寄存器。并且tr im非连续,因为负端和正端分为两段,offset分别是0到负最大和0到正最大,从而影响cp效率。

3、译码校准改进校准把输入寄存器二进制译码,所以需要相应增加逻辑控制。输出位宽为二的输入位宽次方。如图5所示,和二进制校准比较,译码校准tr im控制寄存器减少近一半,并且offset偏移范围从最负和最正线性增加,从而方便cp测试。但同时由于需要增加相应的逻辑控制,如果校准位宽较大,译码需要大量逻辑控制。

技术实现思路

1、为解决上述问题,本发明提供了一种opa线性offset校准电路,其特征在于,包括:

2、比较模块,比较运算放大器正负输入端电压,得到偏移电压;

3、正端校准模块,当所述偏移电压小于零时,采用译码校准模式进行校准;

4、负端校准模块,当所述偏移电压大于零时,采用二进制校准模式进行校准。

5、在本发明一实施例中,所述正端校准模块包括(n+1)/2个译码控制单元,所述译码控制单元并联在一起,构成所述正端校准模块,其中n为大于等于1的正整数,所述译码控制单元的数目向上取整。

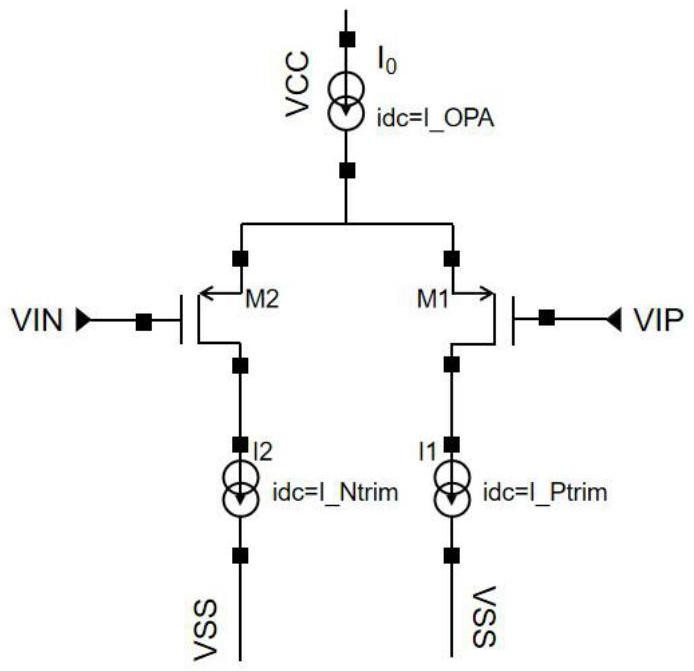

6、在本发明另一实施例中,所述译码控制单元包括:第一mos管m1,第一可控电流源i5;

7、所述第一mos管m1的源极连接所述负端校准模块,第一mos管m1的漏极连接所述第一可控电流源,第一mos管m1的栅极输出电压信号vip。

8、在本发明另一实施例中,所述负端校准模块包括n个二进制控制单元,所述二进制控制单元并联在一起,构成所述负端校准模块,其中n为大于等于1的正整数。

9、在本发明另一实施例中,所述二进制控制单元包括:第二mos管m2,第二可控电流源i 2;

10、所述第二mos管m2的源极连接所述负端校准模块,第二mos管m2的漏极连接所述第二可控电流源,第二mos管m2的栅极输出电压信号vi n。

11、在本发明另一实施例中,所述电路还包括第三可控电流源i 0;

12、所述第三可控电流源连接所述正端校准模块与所述负端校准模块,提供总线电流i_opa。

13、在本发明另一实施例中,所述偏移电压为offset=x=vg1-vg2,其中vg1=vip,vg2=vi n,分别是是m1和m2的栅极电压。

14、在本发明另一实施例中,所述偏移电压offset为正值时,即vgs1>vgs2;

15、通过第二可控电流源i 2加大ids2电流,使得i ds2=i ds1,继而维持vgs2=vgs1,从而消除偏移电压;

16、其中vgs2是m2栅源电压,vgs1是m1栅源电压,i ds2是m2源漏电流,i ds1是m1源漏电流。

17、在本发明另一实施例中,所述偏移电压offset为负值时,即vgs1<vgs2;

18、通过第一可控电流源i1加大ids1电流,使得i ds2=i ds1,继而维持vgs2=vgs1,从而消除偏移电压。

19、在本发明另一实施例中,所述偏移电压offset为零时,vgs2=vgs1;i ds2=i ds1=i_opa/2。

20、本发明相较现有技术具有如下有益效果:

21、(1)相较于二进制校准,本发明针对负向偏移采用了译码校准,针对正向偏移采用了二进制校准,实现了连续线性校准。

22、(2)相较于译码校准,本发明仅针对负向偏移采用了译码校准,少处理1个高位bit,减少了译码校准所需的逻辑控制单元,译码更简洁。

技术特征:

1.一种opa线性offset校准电路,其特征在于,包括:

2.如权利要求1所述的opa线性offset校准电路,其特征在于,所述正端校准模块包括(n+1)/2个译码控制单元,所述译码控制单元并联在一起,构成所述正端校准模块,其中n为大于等于1的正整数,所述译码控制单元的数目向上取整。

3.如权利要求2所述的opa线性offset校准电路,其特征在于,所述译码控制单元包括:第一mos管m1,第一可控电流源i1;

4.如权利要求1所述的opa线性offset校准电路,其特征在于,所述负端校准模块包括n个二进制控制单元,所述二进制控制单元并联在一起,构成所述负端校准模块,其中n为大于等于1的正整数。

5.如权利要求4所述的opa线性offset校准电路,其特征在于,所述二进制控制单元包括:第二mos管m2,第二可控电流源i2;

6.如权利要求4所述的opa线性offset校准电路,其特征在于,所述电路还包括第三可控电流源i0;

7.如权利要求5所述的opa线性offset校准电路,其特征在于,所述偏移电压为offset=x=vg1-vg2,其中vg1=vip,vg2=vi n,分别是是m1和m2的栅极电压。

8.如权利要求7所述的opa线性offset校准电路,其特征在于,所述偏移电压offset为正值时,即vgs1>vgs2;

9.如权利要求8所述的opa线性offset校准电路,其特征在于,所述偏移电压offset为负值时,即vgs1<vgs2;

10.如权利要求8所述的opa线性offset校准电路,其特征在于,所述偏移电压offset为零时,vgs2=vgs1;i ds2=i ds1=i_opa/2。

技术总结

本发明提供了一种OPA线性offset校准电路,其特征在于,包括:比较模块,比较运算放大器正负输入端电压,得到偏移电压;正端校准模块,当所述偏移电压小于零时,采用译码校准模式进行校准;负端校准模块,当所述偏移电压大于零时,采用二进制校准模式进行校准。本发明针对负向偏移采用了译码校准,针对正向偏移采用了二进制校准,实现了连续线性校准,且本发明仅针对负向偏移采用了译码校准,少处理1个高位b it,减少了译码校准所需的逻辑控制单元,译码更简洁。

技术研发人员:张涛,崔玥

受保护的技术使用者:华大半导体(成都)有限公司

技术研发日:

技术公布日:2025/3/24

- 还没有人留言评论。精彩留言会获得点赞!