一种基于流水线结构的并行放大量化ADC

本发明属于数字模拟混合集成电路领域,具体涉及一种基于流水线结构的并行放大量化adc。

背景技术:

1、流水线adc是一种常用的adc结构,可以同时兼顾高速度和高精度的要求。这种结构将多位的长时间的高精度量化拆分成流水线形式的多级低精度短时间量化,并用级间放大器连接各级,逐级放大低精度短时间量化后的量化残差。

2、当前的流水线结构adc已经发展出了多种混合架构,不仅限于基本的流水线-flashadc,还有流水线-逐次逼近adc等结构。由于flashadc硬件开销大的特点,传统的流水线adc的单级量化位数都比较少,级间放大倍数也不会很大,这也就意味着量化和放大时间都比较短。但是在混合架构adc中,比如逐次逼近adc,其硬件开销和功耗都很小,每级的量化位数便不再局限于1.5位或2、3位,可以是更多位、更长时间的量化。级间放大倍数也因此提高,级间放大时间也会增加。

3、在流水线adc中,级间放大时后级处于采样过程,也就是说在放大过程中,后级子adc(次级)不能执行量化操作。对于较长的放大时间,这部分速度损失是十分浪费的。

技术实现思路

1、针对上述存在的问题或不足,为解决现有流水线adc在放大过程中次级不能执行量化导致速度损失的问题,本发明提供了一种基于流水线结构的并行放大量化adc,对级间放大后再进行量化的时序进行了优化,并行放大量化时序,缩短了次级adc的总工作时长。

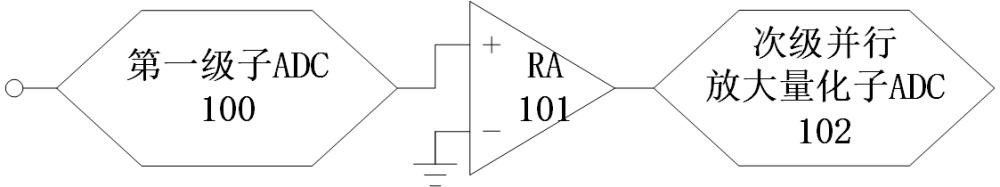

2、一种基于流水线结构的并行放大量化adc,包括依次级联的第一级子adc、级间放大器和次级并行放大量化子adc。

3、所述第一级子adc为任意结构的adc。

4、所述级间放大器使用闭环级间放大器,且满足放大精度随着放大时间变长而变高,使得该级子adc可以随着放大精度变高,连续进行从低位到高位不断提升精度的量化。

5、所述次级并行放大量化子adc为并行放大量化的子adc,该形式的子adc由一个连续时间量化ctadc和一个离散时间量化dtadc组成,其次级量化时序采用ctadc执行放大时的量化任务和dtadc执行放大结束后的量化任务。其中,连续时间量化是指在第二级采样时对连续变化的电压量化;离散时间量化是指在第二级采样完成后对得到的不变的离散电压量化。

6、进一步的,所述次级并行放大量化子adc由ctadc和dtadc组成,ctadc和dtadc中各包含一个电容阵列dac,两者相较而言,ctadc的电容阵列dac容值较小、精度较低,因此速度更快、功耗更低。ctadc在级间放大器放大过程中对连续变化的输入信号完成次级子adc的低位量化部分任务,dtadc在级间放大器结束放大后对离散稳定的输入信号完成次级子adc剩余高位量化任务;整个次级子adc量化过程的前m位为低位,共k位,第k-m位为高位,其中k>m≥1。

7、dtadc的采样和量化过程建立在一个不受ctadc量化影响的高精度大电容阵列dac上,而ctadc的量化过程建立在一个低精度小电容阵列上。其中,由于电容失配和kt/c噪声对adc精度限制条件约束了两个电容阵列dac的单位电容的大小,高精度大电容阵列dac需满足次级全部k位量化精度;低精度小电容阵列dac仅需满足次级并行放大量化子adc中k位量化的前m位ctadc量化需要的精度。

8、在第一级子adc量化完成后,级间放大器放大第一级子adc的量化残差电压至次级并行放大量化子adc,dtadc开始采样;级间放大器经过ct精度建立时间后,ctadc开始ct量化。级间放大器结束放大后,ctadc将量化结果加载到dtadc上,dtadc开始进行dt量化。

9、为了同时保证高精度和低功耗的要求,如果所述次级并行放大量化子adc由ctadc执行全部的量化任务,由于两个adc之间存在失配,则会恶化次级并行放大量化子adc的精度;同时由于要ctadc执行全部量化,则ctadc需要使用满足次级全部k位量化的高精度电容阵列dac,无法降低功耗;另外,级间放大器一直处于放大状态会增加功耗,所以ctadc只执行低位量化任务,而级间放大器放大到次级子adc所需精度后就可以进入复位状态以不增加功耗;次级并行量化子adc在级间放大器结束放大后便可以进行精度更高的dt量化了。

10、进一步的,所述dtadc和ctadc的结合形式为隔离电容连接。

11、进一步的,所述dtadc和ctadc的结合形式为先后关断的采样开关。

12、进一步的,所述dtadc和ctadc的结合形式为四输入比较器的共享。

13、进一步的,所述次级并行放大量化子adc后,还依次级联f级的级间放大器和次级并行放大量化子adc,构成f+2级的流水线结构的并行放大量化adc。

14、综上所述,本发明采用闭环级间放大器作为级间放大器,级间放大器相应的次级量化子adc采用并行放大量化子adc;而并行放大量化子adc以ctadc执行低功耗、低精度的量化任务,高精度的量化任务由dtadc完成;进而构成整个流水线adc的架构。本发明中次级量化时序改变了通常在级间放大器完全建立后的离散时间量化,增加一部分的连续时间量化,让放大和量化并行进行,大大提高了速度,兼顾功耗和精度;并且本发明还可以级联f级的级间放大器和次级并行放大量化子adc,构成f+2级的流水线结构,以达成更高的性能诉求。

技术特征:

1.一种基于流水线结构的并行放大量化adc,其特征在于:包括依次级联的第一级子adc、级间放大器和次级并行放大量化子adc;

2.如权利要求1所述基于流水线结构的并行放大量化adc,其特征在于:所述次级并行放大量化子adc由ctadc和dtadc组成,ctadc和dtadc中各包含一个电容阵列dac,两者相较而言,ctadc的电容阵列dac容值较小、精度较低;ctadc在级间放大器放大过程中对连续变化的输入信号完成次级子adc的低位量化部分任务,dtadc在级间放大器结束放大后对离散稳定的输入信号完成次级子adc剩余高位量化任务;整个次级子adc量化过程的前m位为低位,共k位,第k-m位为高位,k>m≥1;

3.如权利要求1所述基于流水线结构的并行放大量化adc,其特征在于:所述其次级量化时序由ct精度建立时间、ct量化时间和dt量化时间三部分构成;

4.如权利要求2所述基于流水线结构的并行放大量化adc,其特征在于:所述dtadc和ctadc的结合形式为隔离电容连接。

5.如权利要求2所述基于流水线结构的并行放大量化adc,其特征在于:所述dtadc和ctadc的结合形式为先后关断的采样开关。

6.如权利要求2所述基于流水线结构的并行放大量化adc,其特征在于:所述dtadc和ctadc的结合形式为四输入比较器的共享。

7.如权利要求1所述基于流水线结构的并行放大量化adc,其特征在于:所述次级并行放大量化子adc后,还依次级联f级的级间放大器和次级并行放大量化子adc,f≥1,构成f+2级流水线结构的并行放大量化adc。

技术总结

本发明属于数字模拟混合集成电路领域,具体涉及一种基于流水线结构的并行放大量化ADC。本发明采用闭环级间放大器作为级间放大器,级间放大器相应的次级量化子ADC采用并行放大量化子ADC,构成整个流水线ADC的架构,其次级量化时序以并行放大量化子ADC中的CTADC执行低功耗、低精度的量化任务,而高精度的量化任务由DTADC完成。本发明中次级量化时序改变了通常在级间放大器完全建立后的离散时间量化,增加一部分的连续时间量化,让放大和量化并行进行,大大提高了速度,兼顾功耗和精度;并且本发明还可以级联f级的级间放大器和次级并行放大量化子ADC,构成f+2级的流水线结构,以达成更高的性能诉求。

技术研发人员:李东旭,张天赐,刘瀚泽,吴克军,张中,宁宁,于奇,李靖

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2025/1/13

- 还没有人留言评论。精彩留言会获得点赞!