只读存储器阵列、集成电路器件及其制造方法与流程

本申请的实施例涉及只读存储器阵列、集成电路器件及其制造方法。

背景技术:

1、集成电路(ic)小型化的持续趋势导致器件逐渐变小,功耗更低,但比早期技术以更高的速度提供更多的功能。这种小型化是通过与越来越严格的规格相关的设计和制造创新实现的。各种电子设计自动化(eda)工具用于生成、修改和验证半导体器件的设计,同时确保满足ic结构设计和制造规范。

技术实现思路

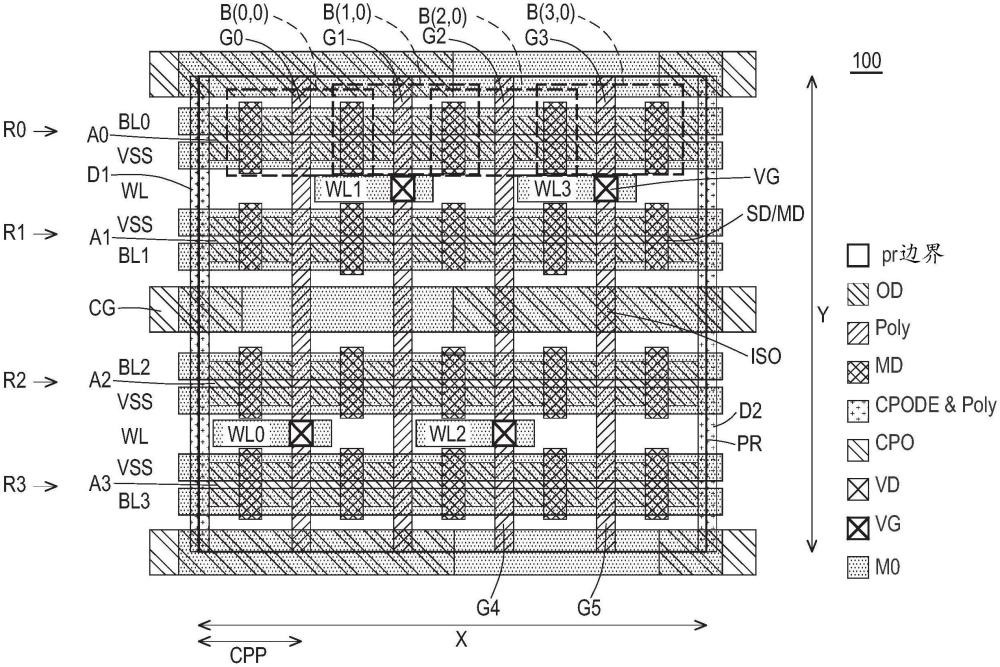

1、根据本申请实施例的一个方面,提供了一种只读存储器(rom)阵列,包括:rom位的第一行至第四行,包括对应邻近的第一有源区至第四有源区,其中,rom位的第一行至第四行中的每行包括沿着第一有源区至第四有源区中的相应一个定位的总共四个相邻的rom位,每个rom位的总共四个rom位中的每个rom位在相应的有源区中包括两个源极/漏极(s/d)区,以及rom位的每行的三个s/d区由四个rom位共享。

2、根据本申请实施例的另一个方面,提供了一种集成电路(ic)器件,包括:在第一伪栅极结构和第二伪栅极结构之间延伸的相邻的第一有源区至第四有源区;第一栅电极,延伸穿过第一有源区至第四有源区中的每个,并与第一伪栅极结构偏移栅极节距;第二栅电极,延伸穿过第一有源区至第四有源区中的每个,并且与第一栅电极偏移栅极节距;第三栅电极,延伸穿过第一有源区和第二有源区中的每个,并且与第二栅电极偏移栅极节距;第四栅电极,延伸穿过第一有源区和第二有源区中的每个,并且与第三栅电极和第二伪栅极结构中的每个偏移栅极节距;第五栅电极,延伸穿过第三有源区和第四有源区中的每个,与第二栅电极偏移栅极节距,并通过第一隔离结构与第三栅电极隔开;和第六栅电极,延伸穿过第三有源区和第四有源区中的每个,与第五栅电极和第二伪栅极结构中的每个偏移栅极节距,并通过第二隔离结构与第四栅电极隔开。

3、根据本申请实施例的又一个方面,提供了一种制造集成电路(ic)器件的方法,方法包括:在半导体衬底中形成相邻的第一有源区至第四有源区;和构建多个栅极结构,构建多个栅极结构包括:在第一有源区至第四有源区中的每个的端点上方构建第一伪栅极结构和第二伪栅极结构;构建与第一伪栅极结构偏移栅极节距的第一栅极结构,构建第一栅极结构包括形成在第一有源区至第四有源区上方延伸的第一栅电极;构建与第一栅极结构偏移栅极节距的第二栅极结构,构建第二栅极结构包括形成在第一有源区至第四有源区上方延伸的第二栅电极;构建与第二栅电极偏移栅极节距的第三栅极结构,构建第三栅极结构包括:形成在第一有源区和第二有源区上方延伸的第三栅电极;形成在第三有源区和第四有源区上方延伸的第四栅电极;和在第三栅电极和第四栅电极之间形成第一隔离结构;和构建与第三栅极结构和第二伪栅极结构中的每个偏移栅极节距的第四栅极结构,构建第四栅极结构包括:形成在第一有源区和第二有源区上方延伸的第五栅电极;形成在第三有源区和第四有源区上方延伸的第六栅电极;和在第五栅电极和第六栅电极之间形成第二隔离结构。

技术特征:

1.一种只读存储器阵列,包括:

2.根据权利要求1所述的只读存储器阵列,还包括:

3.根据权利要求2所述的只读存储器阵列,其中,

4.根据权利要求2所述的只读存储器阵列,其中,

5.根据权利要求2所述的只读存储器阵列,还包括:

6.根据权利要求2所述的只读存储器阵列,还包括:

7.一种集成电路器件,包括:

8.根据权利要求7所述的集成电路器件,还包括:

9.根据权利要求8所述的集成电路器件,还包括:

10.一种制造集成电路器件的方法,所述方法包括:

技术总结

只读存储器(ROM)阵列包括ROM位的第一行至第四行,其包括相应邻近的第一有源区至第四有源区。ROM位的第一行至第四行中的每行包括沿着第一至第四有源区中的相应一个定位的总共四个相邻ROM位,ROM位的每行的总共四个中的每个ROM位都包括相应有源区的两个源极/漏极(S/D)区,ROM位的每行的三个S/D区由四个ROM位共享。本申请的实施例还公开了集成电路器件及其制造方法。

技术研发人员:鲁伊斯·小普雷西利亚诺,陈建盈,林谷峰

受保护的技术使用者:台湾积体电路制造股份有限公司

技术研发日:

技术公布日:2025/4/10

- 还没有人留言评论。精彩留言会获得点赞!