共漏极双MOSFET器件的制备工艺及共漏极双MOSFET器件的制作方法

本申请各实施例属半导体,尤其涉及共漏极双mosfet器件的制备工艺及共漏极双mosfet器件。

背景技术:

1、在半导体领域,mosfet(金属-氧化物半导体场效应晶体管)晶圆作为电子器件的基础元件,其性能和制造工艺对电子设备的发展起着关键作用。共漏极双mosfet晶圆在电路中具有独特的应用,常用于输入输出保护等场景。然而,目前尚未有一种专门针对共漏极双mosfet晶圆的完善且高效的工艺流程。

2、现有的晶圆制造工艺通常是通用型的,对于共漏极双mosfet晶圆的特殊需求并不能很好地满足。例如,在传统工艺流程中,对于晶圆正面和背面的mosfet制作,缺乏针对性的步骤和优化,导致生产出的晶圆在性能、面积和可封装性等方面存在不足。而且,传统工艺在材料选择、设备使用和参数控制等方面,也没有充分考虑共漏极双mosfet晶圆的特点,使得最终产品无法达到理想的效果。

3、这些情况表明,迫切需要创建一种新的、专门针对共漏极双mosfet晶圆的工艺流程,以提高其性能和生产效率,满足日益增长的市场需求。

技术实现思路

1、为了克服现有共漏极双mosfet晶圆工艺流程的不足,本申请实施例提供共漏极双mosfet器件的制备工艺及共漏极双mosfet器件。

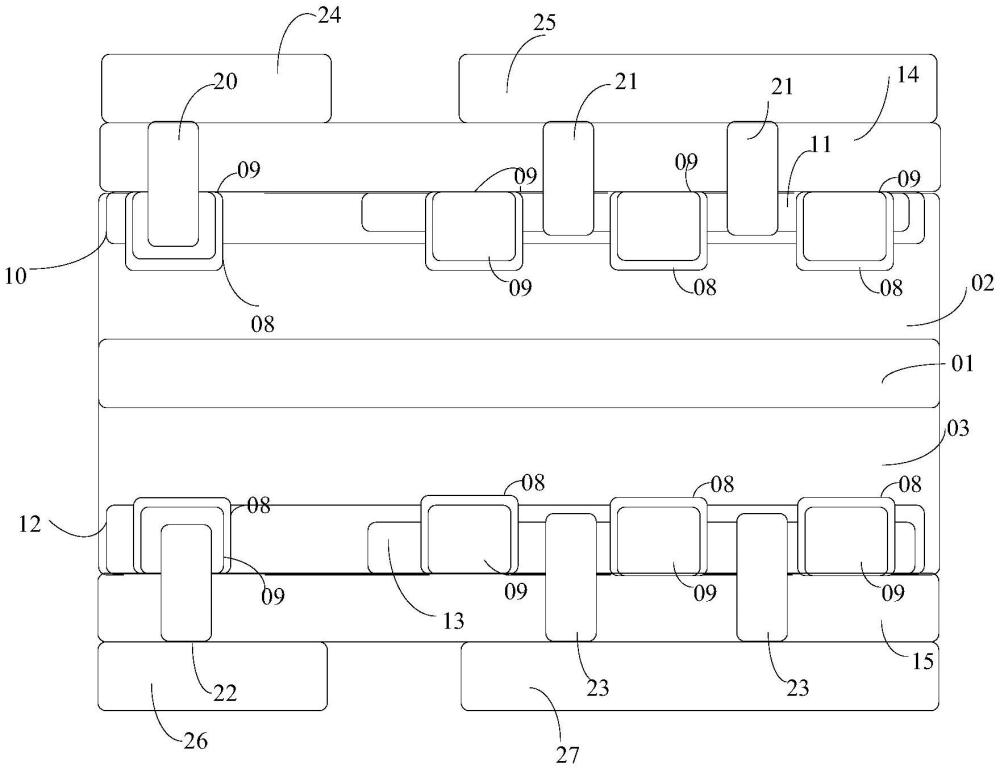

2、第一方面,本申请实施例提供了一种共漏极双mosfet器件的制备工艺,包括:

3、在晶圆正面进行光刻,得到多个设置在所述晶圆正面的第一沟槽;

4、在晶圆背面进行光刻,得到多个设置在所述晶圆背面的第二沟槽,且所述第二沟通与第一沟槽一一对应设置;

5、在所述晶圆正面和背面生长牺牲氧化层,随后刻蚀去除所述牺牲氧化层;

6、在所述第一沟槽和第二沟槽中生长栅氧化层;

7、在所述第一沟槽和第二沟槽中沉积栅极多晶硅;

8、在所述晶圆正面和背面分别形成阱区和注入区,所述晶圆正面的注入区设置在所述晶圆正面的阱区中,部分所述第一沟槽只贯穿在所述晶圆正面的阱区,另一部分所述第一沟槽依次贯穿所述晶圆正面的注入区和所述晶圆正面的阱区;所述晶圆背面的注入区设置在所述晶圆背面的阱区中,部分所述第二沟槽只贯穿所述晶圆背面的阱区,另一部分所述第二沟槽依次贯穿所述晶圆背面的注入区和所述晶圆背面的阱区;且所述晶圆正面的阱区和所述晶圆背面的阱区位置对应设置,所述晶圆正面的注入区和所述晶圆背面的注入区位置对应设置;

9、在所述晶圆正面和背面沉积介质层;

10、在所述晶圆正面的部分第一沟槽中和所述晶圆背面的部分第二沟槽中均分别设置第一接触孔和第二接触孔,在另一部分所述第一沟槽之间设置第三接触孔,所述第三接触孔贯穿所述晶圆正面的介质层和注入区延伸至述晶圆正面的阱区中,在另一部分所述第二沟槽之间设置第四接触孔,所述第四接触孔贯穿所述晶圆背面的介质层和注入区延伸至述晶圆背面的阱区中;

11、在所述第一接触孔、第二接触孔、第三接触孔和第四接触孔中均填充导电金属;

12、在所述第一接触孔、第二接触孔、第三接触孔和第四接触孔上表面分别沉积第一金属层、第二金属层、第三金属层和第四金属层,所述第一金属层和第三金属层间隔设置,所述第二金属层和第四金属层间隔设置。

13、作为本申请一优选实施例,所述晶圆包括衬底和设置在衬底正面的第一外延层和设置在衬底背面的第二外延层。

14、作为本申请一优选实施例,所述衬底、第一外延层和第二外延层的掺杂类型相同,且均为第一掺杂类型。

15、作为本申请一优选实施例,所述晶圆正面的阱区和晶圆背面的阱区均为第二掺杂类型,所述晶圆正面的注入区和晶圆背面的注入区均为第一掺杂类型。

16、第二方面,本申请实施例还提供了一种共漏极双mosfet器件,其特征在于,通过第一方面任一项所述的工艺制备。

17、与现有技术相比,本申请实施例提供共漏极双mosfet器件的制备工艺及共漏极双mosfet器件,解决了现有工艺存在的问题,生产出性能卓越、面积更小、可封装性更强的共漏极双mosfet晶圆。

技术特征:

1.一种共漏极双mosfet器件的制备工艺,其特征在于,包括:

2.如权利要求1所述的一种共漏极双mosfet器件的制备工艺,其特征在于,所述晶圆包括衬底和设置在衬底正面的第一外延层和设置在衬底背面的第二外延层。

3.如权利要求2所述的一种共漏极双mosfet器件的制备工艺,其特征在于,所述衬底、第一外延层和第二外延层的掺杂类型相同,且均为第一掺杂类型。

4.如权利要求1所述的一种共漏极双mosfet器件的制备工艺,其特征在于,所述晶圆正面的阱区和晶圆背面的阱区均为第二掺杂类型,所述晶圆正面的注入区和晶圆背面的注入区均为第一掺杂类型。

5.一种共漏极双mosfet器件,其特征在于,通过如权利要求1至4任一项所述的工艺制备。

技术总结

本申请提供共漏极双MOSFET器件的制备工艺及共漏极双MOSFET器件,通过在晶圆正面和背面形成完成对称的结构,解决了现有工艺存在的问题,生产出性能卓越、面积更小、可封装性更强的共漏极双MOSFET晶圆。

技术研发人员:诸舜杰,董建新

受保护的技术使用者:上海韦尔半导体股份有限公司

技术研发日:

技术公布日:2025/4/10

- 还没有人留言评论。精彩留言会获得点赞!