一种瞬态电压抑制器件的制作方法

本公开一般地涉及电路保护器件领域,并且特别地,涉及具有低钳位电压的双向瞬态电压抑制器器件。

背景技术:

1、现代电子器件依赖于半导体器件二极管来实现各种功能,包括例如在瞬态过电压事件期间的电路保护。这种器件使用通过结接合在一起的n型和p型半导体材料来制造。这种结被称为p-n结。p-n结是在半导体器件的具有第一导电类型(p或n)的区域和具有与第一导电类型相反的第二导电类型(n或p)的第二区域之间形成的接口。

2、诸如瞬态电压抑制器(transient voltage suppressor,tvs)器件的半导体器件可以被制造为单向器件或双向器件。在许多应用中,tvs二极管可以被用于保护敏感电路节点免受一次性和受时间限制的过电压故障的影响。这种tvs二极管也被用于现代大功率igbt电路中,以防止集电极电路中的过载。对这种tvs二极管的要求可以包括具有低偏差和低温度系数的高击穿电压,以及具有低钳位电压的高浪涌电流能力。此外,在许多应用中,tvs器件可以被设计成防止重复性浪涌事件,使得tvs器件在重复性浪涌事件之后容易损坏。然而,现有的瞬态电压抑制器件在保持低钳位电压和双向能力方面是不足的。

技术实现思路

1、提供本

技术实现要素:

是为了以简化形式介绍将在下文的详细描述中进一步描述的精选概念。本实用新型内容不旨在标识所要求保护的主题的关键特征或基本特征,也不旨在协助确定所要求保护的主题的范围。

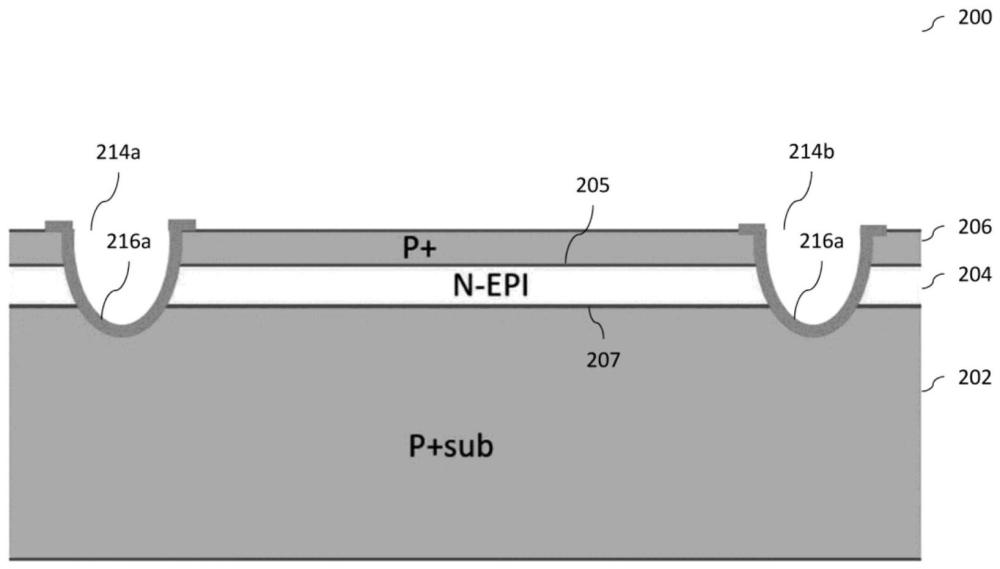

2、在一些实施方式中,当前主题涉及瞬态电压抑制器件。该器件可以包括衬底、基底层和内层。内层可以形成于衬底和基底层之间。第一结可以形成于基底层和内层之间,并且第二结可以形成于内层和衬底之间。

3、在一些实施方式中,当前主题可以包括以下可选特征中的一个或多个。衬底可以是p+型衬底。第一基底层可以是p+型基底层并且内层可以是n型层。

4、在一些实施方式中,第一结和第二结可以是p-n结。

5、在一些实施方式中,基底层和内层中的至少一个可以使用被沉积和/或注入到衬底中的一种或多种第一掺杂剂来形成。一种或多种第一掺杂剂可以使用外延沉积来沉积和/或注入。一种或多种第一掺杂剂可以是n型掺杂剂。一种或多种第一掺杂剂可以包括以下至少一种:磷、硼、砷、镓及其任意组合。内层可以具有预定厚度。该预定厚度可以基于一种或多种第一掺杂剂的沉积和/或注入来确定。瞬态电压抑制器件的特征在于钳位电压。瞬态电压抑制器件的钳位电压可以被确定为以下至少一项的函数:内层中的一种或多种第一掺杂剂的预定浓度、内层的预定厚度、及其任意组合。

6、在一些实施方式中,基底层可以使用被沉积和/或注入到内层中的一种或多种第二掺杂剂来形成。一种或多种第二掺杂剂可以是p+型掺杂剂。

7、在一些实施方式中,该器件可以包括一个或多个隔离区。一个或多个隔离区可以包括一个或多个隔离沟槽。可以形成穿过基底层、内层和衬底的至少一部分的一个或多个隔离区。一个或多个隔离区可以包括覆盖一个或多个隔离区的一个或多个钝化层。

8、在一些实施方式中,衬底、基底层和内层中的至少一项包括以下至少一项:硅、碳化硅、硅锗及其任意组合。

9、在一些实施方式中,瞬态电压抑制器件可以是双向瞬态电压抑制器件。

10、在一些实施方式中,当前主题涉及用于制造瞬态电压抑制器器件的方法。该方法可以包括提供具有第一极性的衬底,在衬底中形成第二极性的内层,在内层的顶部上形成第一极性的基底层,以及形成至少穿过基底层、内层和衬底的至少一部分的至少一个隔离区。第一结可以形成于基底层和内层之间,并且第二结可以形成于内层和衬底之间。基底层和内层中的至少一个可以使用被沉积和/或注入到衬底中的一种或多种第一掺杂剂来形成。

11、本文描述的主题的一个或多个变型的细节在附图和下面的描述中进行阐述。本文所述主题的其它特征和优点将从描述和附图以及从权利要求中是显而易见的。

技术特征:

1.一种瞬态电压抑制器件,其特征在于,包括:

2.根据权利要求1所述的瞬态电压抑制器件,其特征在于,所述衬底为p+型衬底。

3.根据权利要求2所述的瞬态电压抑制器件,其特征在于,第一基底层为p+型基底层,并且所述内层为n型层。

4.根据权利要求1所述的瞬态电压抑制器件,其特征在于,所述第一结和所述第二结是p-n结。

5.根据权利要求1所述的瞬态电压抑制器件,其特征在于,还包括一个或多个隔离区。

6.根据权利要求5所述的瞬态电压抑制器件,其特征在于,所述一个或多个隔离区包括一个或多个隔离沟槽。

7.根据权利要求5所述的瞬态电压抑制器件,其特征在于,所述一个或多个隔离区被形成穿过所述基底层、所述内层和所述衬底的至少一部分。

8.根据权利要求5所述的瞬态电压抑制器件,其特征在于,所述一个或多个隔离区包括覆盖所述一个或多个隔离区的一个或多个钝化层。

9.根据权利要求1所述的瞬态电压抑制器件,其特征在于,所述瞬态电压抑制器件为双向瞬态电压抑制器件。

技术总结

本技术公开了一种瞬态电压抑制器件。该器件包括衬底、基底层和内层。内层被形成在衬底和基底层之间。第一结被形成在基底层与内层之间,并且第二层被形成在内层与衬底之间。

技术研发人员:张环,周继峰

受保护的技术使用者:力特半导体(无锡)有限公司

技术研发日:20240322

技术公布日:2025/3/18

- 还没有人留言评论。精彩留言会获得点赞!