用于减小ESD实验影响的电路板装置的制作方法

本技术涉及印刷电路,具体而言,涉及一种用于减小esd实验影响的电路板装置。

背景技术:

1、国产化芯片进行esd实验时,发现放静电能力相较进口芯片有所不足,为提升国产化芯片其防静电的能力,在电子产品设计过程中,大部分产品都需要依靠螺丝将pcba(贴有元器件的pcb板)与结构组装固定在一起,目前的方案都是直接在pcb板上开一个与螺丝尺寸一致的孔,用于定位组装,现有的方案可以实现产品的定位组装功能,但在产品设计过程中会进行一项esd试验,静电枪会通过直接接触螺丝的方式将高电压打到螺丝上,静电会通过螺丝进入产品内部,此时若是产品内部的pcba静电防护能力不足,部分器件就会失效,导致产品功能全部或部分失效,此时就需要额外增加专门扛esd的器件来保护其他器件不会被打坏,增加成本;当产品进行组装时,在运输环节,生产的各工位进行安装时难免也会接触到静电,当静电也会通过螺丝进入产品内部,若是产品内部的pcba静电防护能力不足,部分器件就会失效,导致产品功能全部或部分失效,影响车辆的正常行驶。

技术实现思路

1、本实用新型的主要目的在于提供一种用于减小esd实验影响的电路板装置,以解决现有技术中电路板的静电防护能力不足的问题。

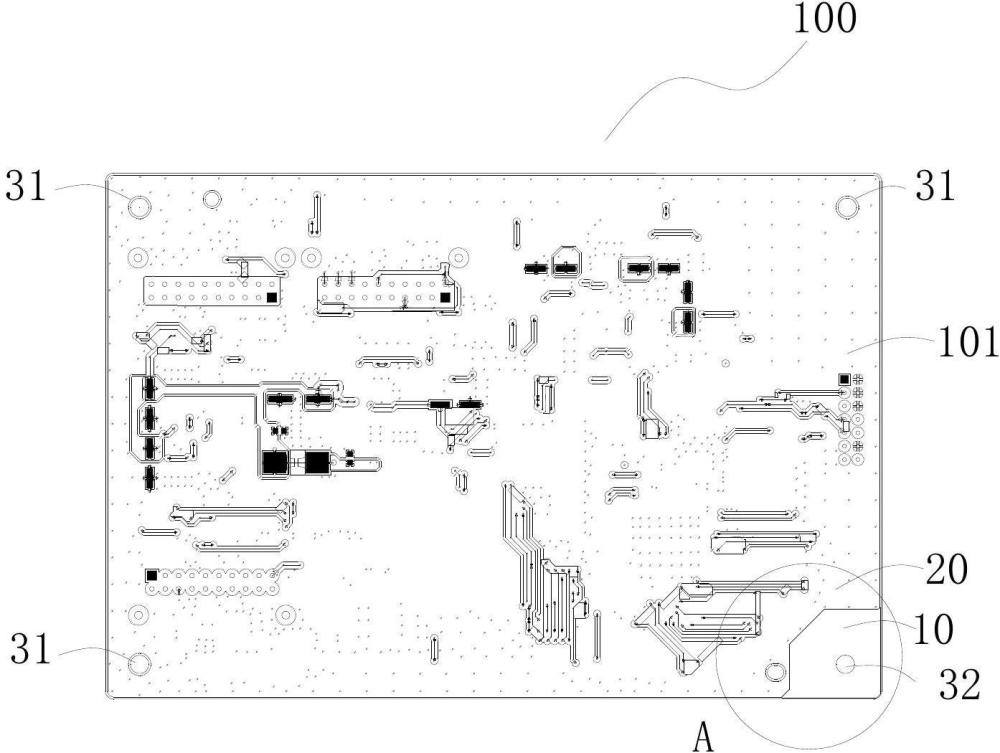

2、为了实现上述目的,提供了一种用于减小esd实验影响的电路板装置。用于减小esd实验影响的电路板装置包括电路板本体,电路板本体上设置有多个测试点位,多个测试点位包括满足实验要求的第一类测试点位和不满足实验要求的第二类测试点位,第二类测试点位的外周设置有禁止覆铜区域,禁止覆铜区域的外径与第二类测试点位的几何中心之间具有预设距离,其中,测试点位用于连接待进行esd实验的螺丝,禁止覆铜区域用于增加电气间隙。

3、进一步地,预设距离设为h,其中h≥10mm。

4、进一步地,第一类测试点位的直径、第二类测试点位的直径与螺丝的直径相等地设置。

5、进一步地,电路板本体上还设置有覆铜区域,覆铜区域与禁止覆铜区域相邻地设置,覆铜区域上设有多个电子元器件,禁止覆铜区域与多个电子元器件有距离地设置。

6、进一步地,测试点位为四个,四个测试点位分别设置于电路板装置的四个折角处。

7、进一步地,电路板本体至少两层地设置。

8、进一步地,电路板本体包括顶层和底层,顶层和底层上都设有覆铜区域和禁止覆铜区域,顶层上的覆铜区域与底层上的覆铜区域重合地设置,顶层上的禁止覆铜区域与底层上的禁止覆铜区域重合地设置。

9、进一步地,禁止覆铜区域的形状为多边形地设置。

10、应用本实用新型的技术方案,通过在不满足esd试验标准的第二类测试点位的外周设置禁止覆铜区域,测试点位用于连接待进行esd实验的螺丝,禁止覆铜区域用于增加电气间隙,使得当静电打到螺丝上时,能量能够在电气间隙中弥散,减少电路板本体收到静电损害的风险,提高了该电路板装置的静电防护能力。

技术特征:

1.一种用于减小esd实验影响的电路板装置,其特征在于,包括:

2.根据权利要求1所述的用于减小esd实验影响的电路板装置,其特征在于,所述预设距离设为h,其中h≥10mm。

3.根据权利要求1所述的用于减小esd实验影响的电路板装置,其特征在于,所述第一类测试点位(31)的直径、所述第二类测试点位(32)的直径与螺丝的直径相等地设置。

4.根据权利要求1所述的用于减小esd实验影响的电路板装置,其特征在于,所述电路板本体(100)上还设置有覆铜区域(20),所述覆铜区域(20)与所述禁止覆铜区域(10)相邻地设置,所述覆铜区域(20)上设有多个电子元器件,所述禁止覆铜区域(10)与多个电子元器件有距离地设置。

5.根据权利要求1所述的用于减小esd实验影响的电路板装置,其特征在于,所述测试点位为四个,四个所述测试点位分别设置于所述电路板本体(100)的四个折角处。

6.根据权利要求4所述的用于减小esd实验影响的电路板装置,其特征在于,所述电路板本体(100)至少两层地设置。

7.根据权利要求6所述的用于减小esd实验影响的电路板装置,其特征在于,所述电路板本体(100)包括顶层(101)和底层(102),所述顶层(101)和所述底层(102)上都设有所述覆铜区域(20)和所述禁止覆铜区域(10),所述顶层(101)上的所述覆铜区域(20)与所述底层(102)上的所述覆铜区域(20)重合地设置,所述顶层(101)上的所述禁止覆铜区域(10)与所述底层(102)上的所述禁止覆铜区域(10)重合地设置。

8.根据权利要求1所述的用于减小esd实验影响的电路板装置,其特征在于,所述禁止覆铜区域(10)的形状为多边形地设置。

技术总结

本技术提供了一种用于减小ESD实验影响的电路板装置,涉及印刷电路技术领域。用于减小ESD实验影响的电路板装置包括电路板本体,电路板本体上设置有多个测试点位,多个测试点位包括满足实验要求的第一类测试点位和不满足实验要求的第二类测试点位,第二类测试点位的外周设置有禁止覆铜区域,禁止覆铜区域的外径与第二类测试点位的几何中心之间具有预设距离,其中,测试点位用于连接待进行ESD实验的螺丝,禁止覆铜区域用于增加电气间隙。这样设置使得当静电打到螺丝上时,能量能够在电气间隙中弥散,减少电路板本体收到静电损害的风险,提高了该电路板装置的静电防护能力。

技术研发人员:王德平,刘元治,李明霞,彭小亮,张鑫

受保护的技术使用者:中国第一汽车股份有限公司

技术研发日:20240718

技术公布日:2024/9/17

- 还没有人留言评论。精彩留言会获得点赞!