一种基于全非晶氧化物晶体管的CMOS电路及制备方法

本发明涉及无线电电子学,尤其涉及一种基于全非晶氧化物晶体管的cmos电路及制备方法。

背景技术:

1、互补金属氧化物半导体技术(cmos)是当前电子芯片领域的主流技术。随着人工智能、物联网和人机交互等新兴信息技术的快速发展,柔性和可穿戴电子芯片的需求日益增加。然而,传统的硅基cmos技术由于其刚性制备工艺,已无法满足这些需求。非晶氧化物薄膜晶体管(tft)是一种基于非晶态氧化物半导体材料的电子器件,相比于传统的非晶硅基tft,非晶氧化物tft具有更高的载流子迁移率、更好的透明性和更低的制造温度,使其在柔性电子和低功耗器件方面具有显著优势。

2、目前,基于非晶n型半导体铟镓锌氧化物(igzo)的tft技术已在显示领域实现商业化。然而,由于缺乏高性能的非晶p型氧化物,基于氧化物tft的cmos技术发展受限。因此,开发高迁移率、低成本的非晶态p型tft和cmos电路,成为推动新一代信息显示技术和柔性集成电路发展的关键方向,实现全非晶p型氧化物与n型氧化物的大规模cmos电路的片上集成,已成为亟待解决的核心问题。

技术实现思路

1、为了解决上述问题,本发明提供了一种基于全非晶氧化物晶体管的cmos电路及制备方法,在n型晶体管和p型晶体管均采用非晶氧化物,从而实现全非晶氧化物晶体管的cmos电路。

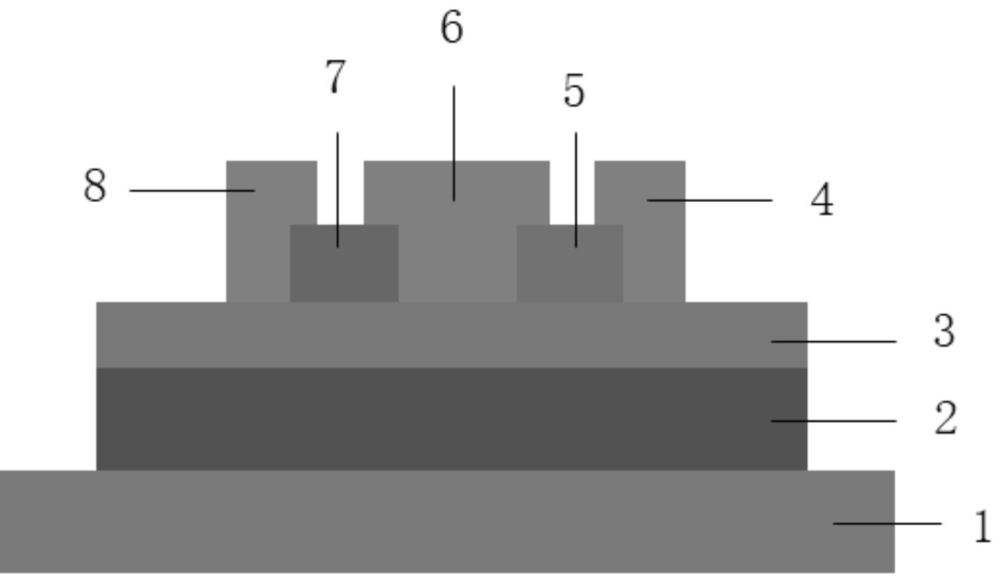

2、一方面,本发明提供一种基于全非晶氧化物晶体管的cmos电路,所述cmos电路包括:衬底、底栅电极及互联层、栅极介质层、n型沟道层、p型沟道层和源漏电极及互联层,所述n型沟道层为非晶氧化物半导体层,所述p型沟道层为非晶掺杂碲氧化物,底栅电极及互联层和源漏电极及互联层均采用金属。

3、进一步地,所述衬底为硅片、聚酰亚胺、聚二甲基硅氧烷、聚萘二甲酸乙二醇酯中的一种。

4、进一步地,所述栅极介质层为氧化铝、氧化铪、氧化锆、氧化硅、氮化硅中的一种或几种。

5、进一步地,n型沟道层的非晶氧化物为铟、镓、锌、锡、钛氧化物中的一种或几种。

6、进一步地,非晶掺杂碲氧化物中的掺杂元素为硒、锑、磷、硫、氯、碘、铋中的一种或几种。

7、进一步地,底栅电极及互联层和源漏电极及互联层采用的金属为钛、金、铝、镍、铂、钯、铬、钼、钨、铜、铟、银中的一种或几种。

8、另一方面,本发明提供一种上述基于全非晶氧化物晶体管的cmos电路的制备方法,所述方法包括以下步骤:

9、步骤s1:使用清洁干净的带有热氧化sio2层的硅片或玻璃片或聚酰亚胺或聚二甲基硅氧烷或聚萘二甲酸乙二醇酯作为衬底;

10、步骤s2:在所述衬底上沉积一层金属并进行图案化用作底栅电极及互联层,底栅电极及互联层的厚度为5nm-500nm,沉积方式包括热蒸发、磁控溅射、电子束蒸发;

11、步骤s3:在步骤s2做完栅图案化的衬底上沉积栅极介质层并进行图案化,所述栅极介质层为氧化铝、氧化铪、氧化锆、氧化硅、氮化硅中的一种或几种,厚度为3nm-500 nm,沉积方式包括原子层沉积、电子束蒸发、热蒸发以及化学气相沉积;

12、步骤s4:在步骤s3完成栅极介质层图案化的样品上沉积n型非晶氧化物半导体层并进行图案化,所述n型非晶氧化物为铟、镓、锌、锡、钛氧化物中的一种或几种,n型非晶氧化物半导体层厚度为1 nm-100nm,沉积方式包括磁控溅射、原子层沉积;

13、步骤s5:在步骤s4完成的样品上沉积p型非晶氧化物半导体层并进行图案化,所述p型非晶氧化物半导体层为元素掺杂碲氧化物,掺杂元素为硒、锑、磷、硫、氯、碘、铋中的一种或几种,p型非晶氧化物半导体层厚度为1nm-100nm沉积方式包括热蒸发;

14、步骤s6:在步骤s5完成的样品上进行退火处理,退火氛围为空气、氮气、或氩气,退火温度为25℃-400℃,退火时间0.5小时-24小时;

15、步骤s7:在步骤s6完成退火处理的样品上沉积源漏电极及互联层,源漏电极及互联层采用金属,厚度为5nm-500nm,沉积方式包括热蒸发、磁控溅射、电子束蒸发。

16、进一步地,所述步骤s2和步骤s7中的金属为钛、金、铝、镍、铂、钯、铬、钼、钨、铜、铟、银中的一种或几种。

17、本发明具有如下有益技术效果:

18、本发明提供的全非晶氧化物晶体管cmos电路的n型晶体管和p型晶体管均采用非晶氧化物,通过采用兼容低温工艺的p型和n型非晶氧化物,实现了在低温下制备柔性基底集成电路的可能,也显著提升了器件可制造性,能够满足大规模柔性电子产品的需求,此外,所使用的非晶氧化物半导体技术与现有生产工艺高度兼容,有助于实现大规模工业化应用,并降低生产成本,同时,非晶氧化物材料的使用符合绿色制造的要求,具有环境友好性和优异的环境稳定性。

技术特征:

1.一种基于全非晶氧化物晶体管的cmos电路,其特征在于,所述cmos电路包括:衬底、底栅电极及互联层、栅极介质层、n型沟道层、p型沟道层和源漏电极及互联层,所述n型沟道层为非晶氧化物半导体层,所述p型沟道层为非晶掺杂碲氧化物,底栅电极及互联层和源漏电极及互联层均采用金属。

2.根据权利要求1所述的基于全非晶氧化物晶体管的cmos电路,其特征在于,所述衬底为硅片、聚酰亚胺、聚二甲基硅氧烷、聚萘二甲酸乙二醇酯中的一种。

3.根据权利要求1所述的基于全非晶氧化物晶体管的cmos电路,其特征在于,所述栅极介质层为氧化铝、氧化铪、氧化锆、氧化硅、氮化硅中的一种或几种。

4.根据权利要求1所述的基于全非晶氧化物晶体管的cmos电路,其特征在于,n型沟道层的非晶氧化物为铟、镓、锌、锡、钛氧化物中的一种或几种。

5.根据权利要求1所述的基于全非晶氧化物晶体管的cmos电路,其特征在于,非晶掺杂碲氧化物中的掺杂元素为硒、锑、磷、硫、氯、碘、铋中的一种或几种。

6.根据权利要求1所述的基于全非晶氧化物晶体管的cmos电路,其特征在于,底栅电极及互联层和源漏电极及互联层采用的金属为钛、金、铝、镍、铂、钯、铬、钼、钨、铜、铟、银中的一种或几种。

7.一种如权利要求1-6任一项所述的基于全非晶氧化物晶体管的cmos电路的制备方法,其特征在于,所述方法包括以下步骤:

8.根据权利要求7所述的制备方法,其特征在于,步骤s2和步骤s7中的金属为钛、金、铝、镍、铂、钯、铬、钼、钨、铜、铟、银中的一种或几种。

技术总结

本发明提供了一种基于全非晶氧化物晶体管的CMOS电路及制备方法,属于无线电电子学技术领域,所述CMOS电路包括:衬底;底栅电极及互联层;栅极介质层;N型沟道层,所述N型沟道层为非晶氧化物半导体层;P型沟道层,所述P型沟道层为非晶掺杂碲氧化物;源漏电极及互联层;其中,底栅电极及互联层和源漏电极及互联层均采用金属。本发明N型晶体管和P型晶体管均采用非晶氧化物,通过采用全非晶氧化物材料能够实现大面积均一性,低成本以及柔性的优点。

技术研发人员:刘奥,王名扬,朱慧慧

受保护的技术使用者:电子科技大学

技术研发日:

技术公布日:2025/2/17

- 还没有人留言评论。精彩留言会获得点赞!