半导体器件版图结构的制作方法

本发明涉及半导体,尤其涉及一种半导体器件版图结构。

背景技术:

1、在半导体器件制造工艺中,一般会同步制备形成标准mos器件和esd器件(esd器件为用于esd防护的mos器件),通过调整esd器件的轻掺杂区的注入能量、注入剂量和注入角度等,可以实现改善esd器件的静电保护能力。

2、图1为现有技术中一种esd器件版图结构的示意图。请参考图1,图1中示意了esd器件的部分结构,半导体衬底10上形成有栅极图形20,半导体衬底10中形成有两个轻掺杂区30和有源区40,两个轻掺杂区30分别位于栅极图形20两侧且延伸至栅极图形20的边缘下方,图1中的esd器件版图结构与标准mos器件版图结构相同。

3、目前,为了区别标准mos器件和esd器件,通常需要利用不同的掩模版,来形成标准mos器件和esd器件中不同的轻掺杂区,利用不同的掩模版即增加一个esd器件的掩模版,导致器件制备成本高;且利用不同的掩模版分步形成标准mos器件和esd器件的轻掺杂区,导致器件制备效率低。

技术实现思路

1、本发明的目的在于提供一种半导体器件版图结构,达到改善半导体器件的静电保护能力的目的,并且能够节约制备成本和提高制备效率。

2、为了达到上述目的,本发明提供了一种半导体器件版图结构,包括:

3、半导体衬底;

4、栅极图形,位于所述半导体衬底上;

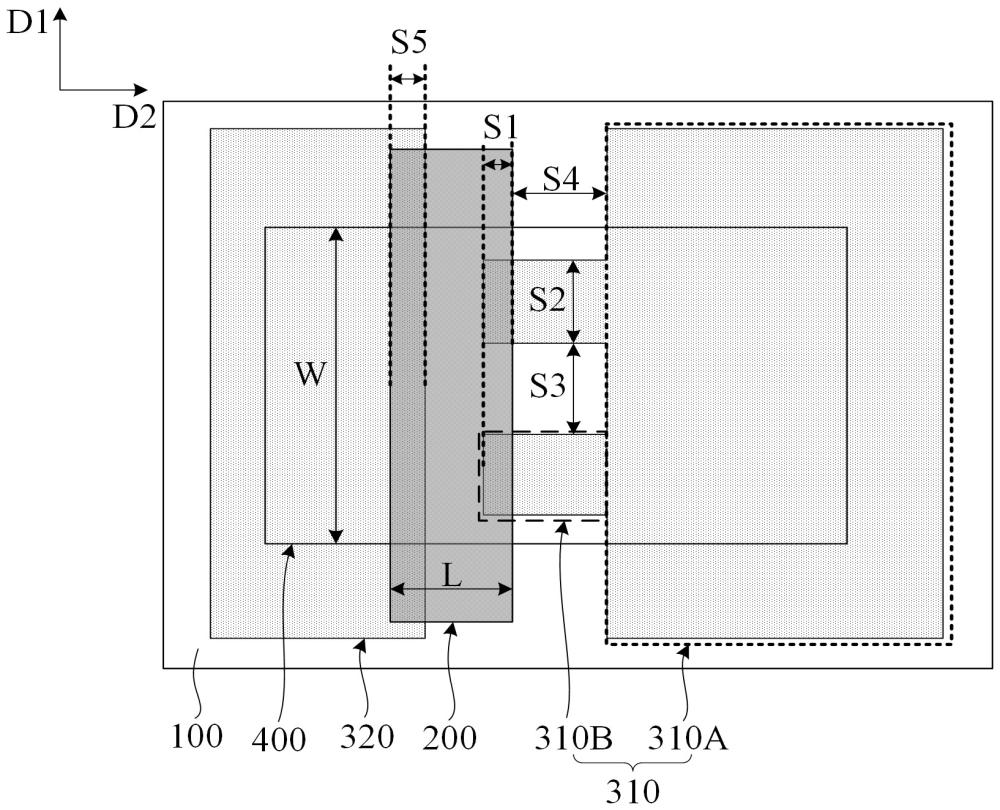

5、漏端轻掺杂区和源端轻掺杂区,分别位于所述栅极图形两侧的半导体衬底中,其中所述漏端轻掺杂区包括第一漏端轻掺杂区和若干第二漏端轻掺杂区,所述第一漏端轻掺杂区与所述栅极图形之间具有间隙,沿第一方向若干所述第二漏端轻掺杂区间隔排列,且若干所述第二漏端轻掺杂区与所述第一漏端轻掺杂区靠近所述栅极图形的一侧连接,所述第二漏端轻掺区延伸至所述栅极图形的边缘下方。

6、可选的,每个所述第二漏端轻掺杂区的面积相同,相邻两个所述第二漏端轻掺杂区的间隙相同,沿第二方向,每个所述第二漏端轻掺杂区延伸至所述栅极图形的边缘下方的尺寸相同,所述第一方向和所述第二方向垂直相交。

7、可选的,所述第二漏端轻掺杂区的形状包括矩形、圆弧形和三角形。

8、可选的,所述第一漏端轻掺杂区和所述第二漏端轻掺杂区的掺杂类型相同。

9、可选的,还包括有源区,所有所述第二漏端轻掺杂区均位于所述有源区中。

10、可选的,沿所述第二方向,所述栅极图形的尺寸为l,所述第二漏端轻掺区延伸至所述栅极图形的边缘下方的最大尺寸为s1,其中s1为至。

11、可选的,沿所述第一方向,所述第二漏端轻掺杂区的最大尺寸为s2,相邻两个所述第二漏端轻掺杂区的最小间隙为s3,其中s2等于s3。

12、可选的,s2和s3均为至。

13、可选的,沿所述第二方向,所述第一漏端轻掺杂区与所述栅极图形的间隙为s4,其中s4为至。

14、可选的,所述源端轻掺杂区延伸至所述栅极图形的边缘下方,所述源端轻掺杂区和所述第二漏端轻掺杂区之间具有间隙;沿所述第二方向,所述源端轻掺杂区延伸至所述栅极图形的边缘下方的尺寸为s5,其中s5为。

15、在本发明提供的半导体器件版图结构中,通过改变漏端轻掺杂区的形貌,使得漏端轻掺杂区包括第一漏端轻掺杂区和若干第二漏端轻掺杂区,第一漏端轻掺杂区与栅极图形之间具有间隙,沿第一方向若干第二漏端轻掺杂区间隔排列,且若干第二漏端轻掺杂区与第一漏端轻掺杂区靠近栅极图形的一侧连接,第二漏端轻掺区延伸至栅极图形的边缘下方;在满足半导体器件的电性能的情况下,通过减小第二漏端轻掺杂区的面积,实现减小漏端轻掺杂区的面积,能够减小漏端轻掺杂区的总掺杂剂量,达到改善半导体器件的静电保护能力的目的,并且不需要额外的掩模版,能够节约制备成本和提高制备效率。

技术特征:

1.一种半导体器件版图结构,其特征在于,包括:

2.如权利要求1所述的半导体器件版图结构,其特征在于,每个所述第二漏端轻掺杂区的面积相同,相邻两个所述第二漏端轻掺杂区的间隙相同,沿第二方向,每个所述第二漏端轻掺杂区延伸至所述栅极图形的边缘下方的尺寸相同,所述第一方向和所述第二方向垂直相交。

3.如权利要求2所述的半导体器件版图结构,其特征在于,所述第二漏端轻掺杂区的形状包括矩形、圆弧形和三角形。

4.如权利要求1所述的半导体器件版图结构,其特征在于,所述第一漏端轻掺杂区和所述第二漏端轻掺杂区的掺杂类型相同。

5.如权利要求1所述的半导体器件版图结构,其特征在于,还包括有源区,所有所述第二漏端轻掺杂区均位于所述有源区中。

6.如权利要求2所述的半导体器件版图结构,其特征在于,沿所述第二方向,所述栅极图形的尺寸为l,所述第二漏端轻掺区延伸至所述栅极图形的边缘下方的最大尺寸为s1,其中s1为至。

7.如权利要求6所述的半导体器件版图结构,其特征在于,沿所述第一方向,所述第二漏端轻掺杂区的最大尺寸为s2,相邻两个所述第二漏端轻掺杂区的最小间隙为s3,其中s2等于s3。

8.如权利要求7所述的半导体器件版图结构,其特征在于,s2和s3均为至。

9.如权利要求6所述的半导体器件版图结构,其特征在于,沿所述第二方向,所述第一漏端轻掺杂区与所述栅极图形的间隙为s4,其中s4为至。

10.如权利要求6所述的半导体器件版图结构,其特征在于,所述源端轻掺杂区延伸至所述栅极图形的边缘下方,所述源端轻掺杂区和所述第二漏端轻掺杂区之间具有间隙;沿所述第二方向,所述源端轻掺杂区延伸至所述栅极图形的边缘下方的尺寸为s5,其中s5为。

技术总结

本发明提供了一种半导体器件版图结构,包括:半导体衬底、栅极图形、漏端轻掺杂区和源端轻掺杂区,其中栅极图形位于半导体衬底上,漏端轻掺杂区和源端轻掺杂区分别位于栅极图形两侧的半导体衬底中,其中漏端轻掺杂区包括第一漏端轻掺杂区和若干第二漏端轻掺杂区,第一漏端轻掺杂区与栅极图形之间具有间隙,沿第一方向若干第二漏端轻掺杂区间隔排列,且若干第二漏端轻掺杂区与第一漏端轻掺杂区靠近栅极图形的一侧连接,第二漏端轻掺区延伸至栅极图形的边缘下方。本发明能够达到改善半导体器件的静电保护能力的目的,并且能够节约制备成本和提高制备效率。

技术研发人员:鲍贤贤,邓少鹏

受保护的技术使用者:合肥晶合集成电路股份有限公司

技术研发日:

技术公布日:2025/3/10

- 还没有人留言评论。精彩留言会获得点赞!