半导体结构及其制备方法与流程

本公开实施例涉及半导体,尤其涉及一种半导体结构及其制备方法。

背景技术:

1、动态存储器(dram)的发展追求高速度、高集成密度、低功耗等性能指标,随着半导体器件结构尺寸的微缩,现有结构所遇到的技术壁垒越来越明显。因此,在现有结构的基础上,开发出更多新颖的结构,是打破现有技术壁垒的有利手段。

2、三维动态随机存储器(3d dram)的出现,尤其是包括多层水平存储单元(multilayer horizontal cell,mhc)的3d dram,通常包括在衬底上堆叠设置的多个晶体管,满足了上述需求。

3、然而,由于晶体管悬置在衬底上,水平字线的制造工艺难度较高,容易出现字线断路或相邻字线短路的情况,影响半导体结构的性能。

技术实现思路

1、根据本公开实施例的第一方面,提供一种半导体结构的制备方法,包括:形成位于衬底上的叠层结构,叠层结构包括沿竖直方向交替叠设的第一半导体层和第二半导体层;在叠层结构中形成第一隔离结构、牺牲结构和填充层,并图形化第一半导体层以形成阵列排布的初始有源图案,第一隔离结构沿第一方向和第二方向阵列排布,第一隔离结构包括位于初始有源图案所在层的第一隔离部和位于第二半导体层所在层的第二隔离部,第一隔离部沿第二方向的尺寸大于第二隔离部沿第二方向的尺寸且沿第二方向相邻的第一隔离部相接触,牺牲结构位于沿第二方向相邻的第一隔离结构之间,填充层位于第二半导体层所在层;去除部分填充层,并形成初始字线层;去除牺牲结构和至少部分填充层以分别形成位线槽和电容槽,并图形化初始有源图案为有源结构,图形化初始字线层为沿第一方向延伸的字线结构;在位线槽和电容槽中分别形成位线结构和电容结构,位线结构和电容结构在第一方向上交替排布且在第二方向上交替排布。

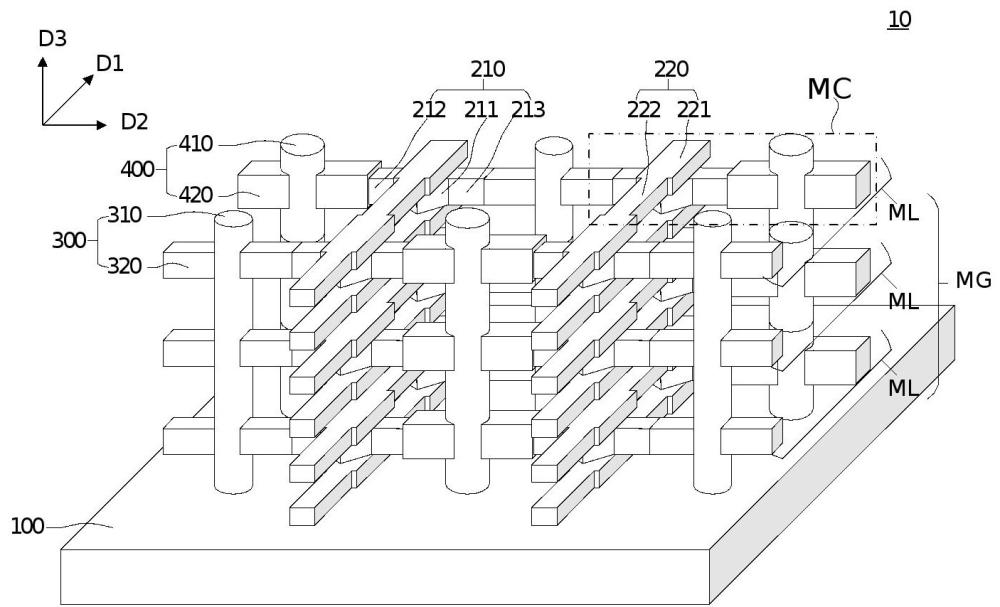

2、在一些实施例中,在叠层结构中形成第一隔离结构、牺牲结构和填充层,并图形化第一半导体层以形成阵列排布的初始有源图案包括:刻蚀叠层结构,以形成多个矩形槽,矩形槽暴露出衬底部分表面,多个矩形槽沿第一方向和第二方向阵列排布,沿第一方向的相邻矩形槽之间的间距大于沿第二方向的相邻矩形槽之间的间距;沿着矩形槽去除部分第一半导体层以形成阵列排布的初始有源图案和隔离槽;形成填充隔离槽的第一隔离结构。

3、在一些实施例中,形成多个矩形槽之后还包括:在矩形槽中填充初始隔离结构;刻蚀叠层结构,以形成多个柱形槽,柱形槽暴露出衬底部分表面,柱形槽位于沿第二方向相邻的初始隔离结构之间;沿着柱形槽去除第二半导体层,以形成第一半导体层之间的层间间隙;在柱形槽和层间间隙中填充第一介质层、第二介质层和第三介质层,以形成位于柱形槽中的牺牲结构以及位于层间间隙中的填充层;沿着矩形槽去除部分第一半导体层以形成阵列排布的初始有源图案和隔离槽,包括:去除至少部分初始隔离结构以暴露矩形槽;沿着矩形槽去除暴露的部分第一半导体层,以形成隔离槽,隔离槽包含位于第一半导体层所在层的第一隔离槽部,第一隔离槽部在第二方向上相接并将初始有源图案在第一方向上断开。

4、在一些实施例中,第一介质层覆盖初始有源图案表面,第二介质层覆盖第二介质层表面且填充于层间间隙,去除部分填充层,并形成初始字线层,包括:去除部分第一介质层,以形成初始字线槽;在初始字线槽中形成初始字线层。

5、在一些实施例中,初始字线层包括栅氧材料层和导电材料层;在初始字线槽中形成初始字线层,包括:在初始字线槽中形成覆盖初始有源图案表面的栅氧材料层;形成覆盖栅氧材料层表面且填充初始字线槽的导电材料层。

6、在一些实施例中,牺牲结构包括第一牺牲结构和第二牺牲结构,第一牺牲结构和第二牺牲结构在第一方向上交替排布且在第二方向上交替排布;去除牺牲结构和至少部分填充层以分别形成位线槽和电容槽,并图形化初始有源图案为有源结构,图形化初始字线层为沿第一方向延伸的字线结构,包括:去除第一牺牲结构以暴露电容竖直槽,沿着电容竖直槽去除部分初始有源图案,以形成电容水平槽,电容竖直槽和电容水平槽构成电容槽;在电容槽中填入第三牺牲结构;去除第二牺牲结构以暴露位线竖直槽,沿着位线竖直槽去除部分初始有源图案,以形成位线水平槽,位线竖直槽和位线水平槽构成位线槽,剩余的初始有源图案作为有源结构。

7、在一些实施例中,去除第二牺牲结构以暴露位线竖直槽之后且沿着电容竖直槽去除部分初始有源图案之前,还包括:沿着位线竖直槽去除部分初始字线层,剩余的初始字线层作为字线结构;形成第二隔离结构,第二隔离结构夹设于字线结构和位线竖直槽之间。

8、根据本公开实施例的第二方面,提供一种半导体结构,包括:位于衬底上的堆叠结构,堆叠结构包括沿竖直方向叠设的多个存储层,每层存储层包括沿第一方向和第二方向阵列排布的多个有源结构以及沿第一方向延伸的字线结构;位于每个有源结构沿第二方向两侧的位线结构和电容结构,位线结构和电容结构在第一方向上交替排布且在第二方向上交替排布;贯穿堆叠结构的第一隔离结构,第一隔离结构沿第一方向和第二方向阵列排布,第一隔离结构包括位于有源结构所在层的第一隔离部和位于字线结构所在层的第二隔离部,第一隔离部沿第二方向的尺寸大于第二隔离部沿第二方向的尺寸且沿第二方向相邻的第一隔离部相接触,位线结构和电容结构位于沿第二方向相邻的第一隔离结构之间。

9、在一些实施例中,位线结构包括位线竖直部和位线水平部,位线竖直部沿竖直方向贯穿堆叠结构,位线水平部位于位线竖直部沿第二方向的两侧且在竖直方向上间隔排布,位线水平部与有源结构接触。

10、在一些实施例中,电容结构包括电容竖直部和电容水平部,电容竖直部沿竖直方向贯穿堆叠结构,电容水平部位于电容竖直部沿第二方向的两侧且在竖直方向上间隔排布,电容水平部包括第一电极部、电容介质层和第二电极部,电容介质层夹设于第一电极部和第二电极部之间,第一电极部与有源结构接触,第二电极部与电容竖直部接触。

11、在一些实施例中,字线结构包括沿第一方向交替连接的第一字线部和第二字线部,第一字线部至少覆盖有源结构,第二字线部位于沿第二方向相邻的第一隔离结构之间,第一字线部沿第二方向的尺寸大于第二字线部沿第二方向的尺寸。

12、在一些实施例中,还包括:第二隔离结构,第二隔离结构夹设于第一字线部和位线结构之间;第三隔离结构,第三隔离结构夹设于第一字线部和电容结构之间。

13、在一些实施例中,第一字线部具有沿第二方向彼此相对的弧形侧壁。

14、在一些实施例中,有源结构在第一方向上的尺寸不均匀,且有源结构具有朝向相邻第一隔离结构之间接触面的凸出部。

15、本公开实施例中,在叠层结构中形成隔离结构和牺牲结构,能够提前定义并划分各器件结构设置区域,提高各器件结构之间的集成度并有效提高器件结构之间的隔离效果,且通过形成填充层进行占位,再将填充层去除后形成初始字线层,简化了水平字线的制造工艺难度,能够确保初始字线层在竖直方向上间隔排布,避免出现字线结构在短路或断路的情况发生。

技术特征:

1.一种半导体结构的制备方法,其特征在于,包括:

2.根据权利要求1所述的制备方法,其特征在于,所述在所述叠层结构中形成第一隔离结构、牺牲结构和填充层,并图形化所述第一半导体层以形成阵列排布的初始有源图案包括:

3.根据权利要求2所述的制备方法,其特征在于,形成多个矩形槽之后还包括:

4.根据权利要求3所述的制备方法,其特征在于,所述第一介质层覆盖所述初始有源图案表面,所述第二介质层覆盖所述第二介质层表面且填充于所述层间间隙,去除部分所述填充层,并形成初始字线层,包括:

5.根据权利要求4所述的制备方法,其特征在于,初始字线层包括栅氧材料层和导电材料层;在所述初始字线槽中形成初始字线层,包括:

6.根据权利要求1所述的制备方法,其特征在于,所述牺牲结构包括第一牺牲结构和第二牺牲结构,所述第一牺牲结构和所述第二牺牲结构在所述第一方向上交替排布且在所述第二方向上交替排布;去除所述牺牲结构和至少部分填充层以分别形成位线槽和电容槽,并图形化所述初始有源图案为有源结构,图形化所述初始字线层为沿第一方向延伸的字线结构,包括:

7.根据权利要求6所述的制备方法,其特征在于,去除所述第二牺牲结构以暴露位线竖直槽之后且沿着电容竖直槽去除部分初始有源图案之前,还包括:

8.一种半导体结构,其特征在于,包括:

9.根据权利要求8所述的半导体结构,其特征在于,所述位线结构包括位线竖直部和位线水平部,所述位线竖直部沿竖直方向贯穿所述堆叠结构,所述位线水平部位于所述位线竖直部沿所述第二方向的两侧且在所述竖直方向上间隔排布,所述位线水平部与所述有源结构接触。

10.根据权利要求8所述的半导体结构,其特征在于,所述电容结构包括电容竖直部和电容水平部,所述电容竖直部沿竖直方向贯穿所述堆叠结构,所述电容水平部位于所述电容竖直部沿所述第二方向的两侧且在所述竖直方向上间隔排布,所述电容水平部包括第一电极部、电容介质层和第二电极部,所述电容介质层夹设于所述第一电极部和所述第二电极部之间,所述第一电极部与所述有源结构接触,所述第二电极部与所述电容竖直部接触。

11.根据权利要求8所述的半导体结构,其特征在于,所述字线结构包括沿所述第一方向交替连接的第一字线部和第二字线部,所述第一字线部至少覆盖所述有源结构,所述第二字线部位于沿第二方向相邻的第一隔离结构之间,所述第一字线部沿第二方向的尺寸大于所述第二字线部沿第二方向的尺寸。

12.根据权利要求11所述的半导体结构,其特征在于,还包括:

13.根据权利要求11所述的半导体结构,其特征在于,所述第一字线部具有沿所述第二方向彼此相对的弧形侧壁。

14.根据权利要求8所述的半导体结构,其特征在于,所述有源结构在第一方向上的尺寸不均匀,且所述有源结构具有朝向相邻所述第一隔离结构之间接触面的凸出部。

技术总结

一种半导体结构及其制备方法,该半导体结构的制备方法包括:形成位于衬底上的叠层结构;在叠层结构中形成第一隔离结构、牺牲结构和填充层,图形化第一半导体层以形成阵列排布的初始有源图案,第一隔离结构包括第一隔离部和第二隔离部,第一隔离部沿第二方向的尺寸大于第二隔离部沿第二方向的尺寸,沿第二方向相邻的第一隔离部相接触;去除部分填充层并形成初始字线层;去除牺牲结构以分别形成位线槽和电容槽,图形化初始有源图案为有源结构,图形化初始字线层为字线结构;在位线槽和电容槽中分别形成位线结构和电容结构,位线结构和电容结构在第一方向上交替排布且在第二方向上交替排布。上述半导体结构的制备方法简化了字线结构的制造工艺难度。

技术研发人员:曹堪宇,黎冠杰,孟皓,吴楠

受保护的技术使用者:长鑫科技集团股份有限公司

技术研发日:

技术公布日:2025/4/7

- 还没有人留言评论。精彩留言会获得点赞!