一种高速多通道AD采集及高性能网口通讯板卡的制作方法

一种高速多通道ad采集及高性能网口通讯板卡

技术领域

1.本实用新型涉及通讯板卡技术领域,特别是涉及一种高速多通道ad采集及高性能网口通讯板卡。

背景技术:

2.目前,通讯板卡存在有体积大、串口少的缺点,且作用较为单一,没有多样性以及采集速度较慢的缺点。

技术实现要素:

3.针对上述问题,本实用新型提供了一种高速多通道ad采集及高性能网口通讯板卡,具有体积小、多串口且可选做485通讯以及高精度高速ad采集的优点。

4.本实用新型的技术方案是:

5.一种高速多通道ad采集及高性能网口通讯板卡,包括第一i/o接口、ad采集电路和两个独立串口电路,所述ad采集电路包括八个a/d转换器、与若干a/d转换器连接的时钟电路、与时钟电路连接的d/a转换器和分别与时钟电路连接的控制信号总线和并行或串行数据总线,若干a/d转换器分别连接有ch通道。

6.上述技术方案的工作原理如下:

7.ad采集电路上的ch通道在接收到信号后,首先经若干a/d转换器进行转换并输入到时钟电路内进行处理,接着分别时钟电路的信号输出端经d/a转换器进行转换并进入到基准信号端,以及控制信号总线和并行或串行数据总线输出。

8.在进一步的技术方案中,所述时钟电路包括依次连接的控制逻辑模块、配置寄存器和第二i/o接口。

9.控制逻辑模块、配置寄存器和第二i/o接口组成用于进行准确控制的时钟电路。

10.在进一步的技术方案中,所述通讯板卡还包括键盘管理电路、存储电路和显示接口。

11.通讯板卡包括有键盘管理电路、存储电路和显示接口用以完成整个电路的控制运行。

12.在进一步的技术方案中,所述ch通道包括ch_a0、ch_a1、ch

‑

b0、ch_b1、ch

‑

c0、ch_c1、ch

‑

d0和ch_d1。

13.ch通道用于连接板卡与a/d转换器之间的接口,通过设置多个ch通道可以提高ad采集电路的转换效率。

14.在进一步的技术方案中,两个所述独立串口电路分为rs

‑

232接口和rs

‑

422接口。

15.rs

‑

232接口是目前最常用的一种串行通讯接口,rs

‑

422接口采用平衡传输采用单向/非可逆,有使能端或没有使能端的传输线,其中,rs

‑

422接口可以达到选做485通讯的作用。

16.本实用新型的有益效果是:

17.1、能够达到体积小、多串口且可选做485通讯以及高精度高速ad采集的效果;

18.2、控制逻辑模块、配置寄存器和第二i/o接口组成用于进行准确控制的时钟电路;

19.3、通讯板卡包括有键盘管理电路、存储电路和显示接口用以完成整个电路的控制运行;

20.4、ch通道用于连接板卡与a/d转换器之间的接口,通过设置多个ch通道可以提高ad采集电路的转换效率;

21.5、rs

‑

232接口是目前最常用的一种串行通讯接口,rs

‑

422接口采用平衡传输采用单向/非可逆,有使能端或没有使能端的传输线,齐总,rs

‑

422接口可以达到选做485通讯的作用。

附图说明

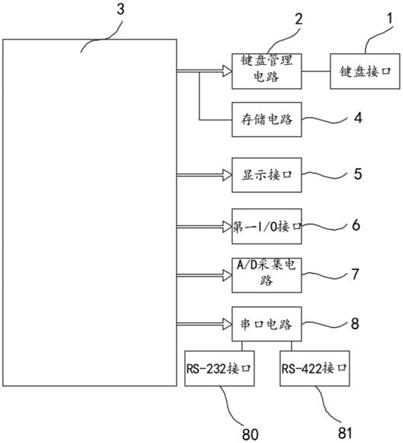

22.图1是本实用新型实施例所述一种高速多通道ad采集及高性能网口通讯板卡的原理图一;

23.图2是本实用新型实施例所述ad采集电路的原理图。

24.附图标记说明:

25.1、键盘接口;2、键盘管理电路;3、板卡;4、存储电路;5、显示接口;6、第一i/o接口;7、a/d采集电路;70、ch通道;71、a/d转换器;72、d/a转换器;8、独立串口电路;80、rs

‑

232接口;81、rs

‑

422接口;9、时钟电路;90、控制逻辑模块;91、配置寄存器;92、第二i/o接口;10、控制信号总线;11、并行或串行数据总线。

具体实施方式

26.下面结合附图对本实用新型的实施例作进一步说明。

27.实施例:

28.如图1和图2所示,一种高速多通道ad采集及高性能网口通讯板卡3,包括第一i/o接口6、ad采集电路7和两个独立串口电路8,所述ad采集电路7包括八个a/d转换器71、与若干a/d转换器71连接的时钟电路9、与时钟电路9连接的d/a转换器72和分别与时钟电路9连接的控制信号总线10和并行或串行数据总线11,若干a/d转换器71分别连接有ch通道70。

29.上述技术方案的工作原理如下:

30.ad采集电路7上的ch通道70在接收到信号后,首先经若干a/d转换器71进行转换并输入到时钟电路9内进行处理,接着分别时钟电路9的信号输出端经d/a转换器72进行转换并进入到基准信号端,以及控制信号总线10和并行或串行数据总线11输出。

31.在另一个实施例中,如图2所示,所述时钟电路9包括依次连接的控制逻辑模块90、配置寄存器91和第二i/o接口92。

32.控制逻辑模块90、配置寄存器91和第二i/o接口92组成用于进行准确控制的时钟电路9。

33.在另一个实施例中,如图1所示,所述通讯板卡3还包括键盘管理电路2、存储电路4和显示接口5。

34.通讯板卡3包括有键盘管理电路2、存储电路4和显示接口5用以完成整个电路的控制运行。

35.在另一个实施例中,如图2所示,所述ch通道70包括ch_a0、ch_a1、ch

‑

b0、ch_b1、ch

‑

c0、ch_c1、ch

‑

d0和ch_d1。

36.ch通道用于连接板卡与a/d转换器之间的接口,通过设置多个ch通道70可以提高ad采集电路7的转换效率。

37.在另一个实施例中,如图2所示,两个所述独立串口电路8分为rs

‑

232接口80和rs

‑

422接口81。

38.rs

‑

232接口80是目前最常用的一种串行通讯接口,rs

‑

422接口81采用平衡传输采用单向/非可逆,有使能端或没有使能端的传输线,其中,rs

‑

422接口81可以达到选做485通讯的作用。

39.以上所述实施例仅表达了本实用新型的具体实施方式,其描述较为具体和详细,但并不能因此而理解为对本实用新型专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本实用新型构思的前提下,还可以做出若干变形和改进,这些都属于本实用新型的保护范围。

技术特征:

1.一种高速多通道ad采集及高性能网口通讯板卡,其特征在于,包括第一i/o接口、ad采集电路和两个独立串口电路,所述ad采集电路包括八个a/d转换器、与若干a/d转换器连接的时钟电路、与时钟电路连接的d/a转换器和分别与时钟电路连接的控制信号总线和并行或串行数据总线,若干a/d转换器分别连接有ch通道。2.根据权利要求1所述的一种高速多通道ad采集及高性能网口通讯板卡,其特征在于,所述时钟电路包括依次连接的控制逻辑模块、配置寄存器和第二i/o接口。3.根据权利要求1所述的一种高速多通道ad采集及高性能网口通讯板卡,其特征在于,所述通讯板卡还包括键盘管理电路、存储电路和显示接口。4.根据权利要求1所述的一种高速多通道ad采集及高性能网口通讯板卡,其特征在于,所述ch通道包括ch_a0、ch_a1、ch

‑

b0、ch_b1、ch

‑

c0、ch_c1、ch

‑

d0和ch_d1。5.根据权利要求1所述的一种高速多通道ad采集及高性能网口通讯板卡,其特征在于,两个所述独立串口电路分为rs

‑

232接口和rs

‑

422接口。

技术总结

本实用新型公开了一种高速多通道AD采集及高性能网口通讯板卡,包括第一I/O接口、AD采集电路和两个独立串口电路,所述AD采集电路包括八个A/D转换器、与若干A/D转换器连接的时钟电路、与时钟电路连接的D/A转换器和分别与时钟电路连接的控制信号总线和并行或串行数据总线,若干A/D转换器分别连接有CH通道。本实用新型具有体积小、多串口且可选做485通讯以及高精度高速AD采集的优点。高精度高速AD采集的优点。高精度高速AD采集的优点。

技术研发人员:张磊

受保护的技术使用者:成都天贸科技有限公司

技术研发日:2021.07.29

技术公布日:2022/1/4

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1