一种基于堆栈式工艺的图像传感器的制作方法

本申请涉及成像,具体涉及一种基于堆栈式工艺的图像传感器。

背景技术:

1、图像传感器是利用光电器件的光电转换功能将感光面上的光像转换为与光像成相应比例关系的电信号。与光敏二极管,光敏三极管等“点”光源的光敏元件相比,图像传感器是将其受光面上的光像,分成许多小单元,将其转换成可用的电信号的一种功能器件。现行图像传感器的曝光方式包括卷帘快门和全局快门等多种方式,图像传感器也逐渐发展为具有体积小、重量轻、集成度高、分辨率高、功耗低、寿命长、价格低等特点,在各个行业得到了广泛应用。

2、在构思及实现本申请过程中,发明人发现至少存在如下问题:其中卷帘快门图像传感器采用逐行曝光量化读出的方式进行一帧的图像信号处理,该特点使得卷帘快门图像传感器的帧率受限于行量化与行数据处理的循环等待时间,即模拟电路量化像素信号的时间与数字电路处理读出的时间不匹配,使得卷帘快门图像传感器量化帧率受限;另外,卷帘快门的逐行曝光量化还会因为行间曝光时间差的原因导致拍摄运动物体图像出现拖尾。

技术实现思路

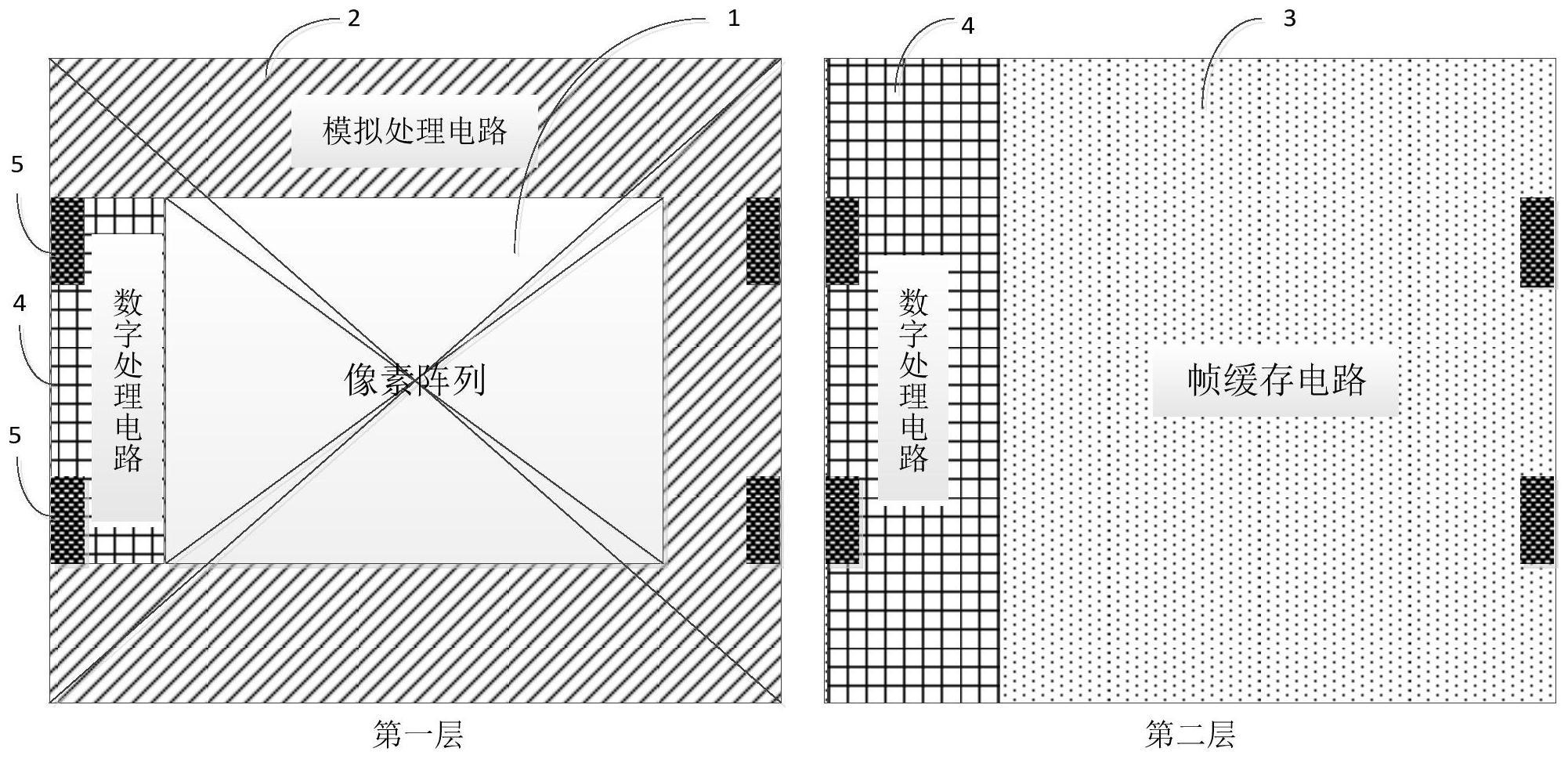

1、为了缓解以上问题,本申请提供一种基于堆栈式工艺的图像传感器,具体地,包括:像素阵列、模拟处理电路、数字处理电路、混合键合走线和帧缓存电路;

2、所述模拟处理电路与所述像素阵列连接,用于将所述像素单元逐行曝光后的像素信号量化读取,以获取行量化信号;

3、所述帧缓存电路与所述模拟处理电路连接,用于将所述行量化信号逐行缓存为行缓存信号;

4、所述数字处理电路与所述帧缓存电路连接,用于处理所述行缓存信号;

5、其中,所述图像传感器包括第一层硅片和第二层硅片,所述第一层硅片与所述第二层硅片通过设置于所述图像传感器边缘的金所述混合键合走线连接,所述像素阵列设置于所述第一层硅片,所述帧缓存电路设置于所述第二层硅片。

6、可选地,所述模拟处理电路包括互相连接的行驱动单元和量化单元,所述行驱动单元用于将每行像素的感光电压驱动输出至所述量化单元,以使所述量化单元对所述感光电压进行量化读取。

7、可选地,组织成行及列的所述像素阵列矩形设置于所述第一层硅片的中心。

8、可选地,所述模拟处理电路部分或全部设置在所述第一层硅片上,且所述模拟处理电路邻接于所述像素阵列的至少两个相邻侧边;或,所述模拟处理电路全部设置在所述第二层硅片上,且所述模拟处理电路通过所述混合键合走线连接所述像素阵列的至少两个相邻侧边。

9、可选地,部分或全部设置在所述第二层硅片上的所述模拟处理电路邻接于所述帧缓存电路的至少一侧边;或,全部设置在所述第一层硅片上的所述模拟处理电路通过所述混合键合走线连接所述帧缓存电路。

10、可选地,所述数字处理电路部分或全部设置在所述第二层硅片上,且所述数字处理电路邻接于所述帧缓存电路的至少一侧边;或,所述数字处理电路全部设置在所述第一层硅片上,且所述数字处理电路通过所述混合键合走线连接所述帧缓存电路。

11、可选地,设置于同一层硅片的所述数字处理电路与所述模拟处理电路具有至少一邻接侧边;

12、或,设置于不同层硅片的所述数字处理电路与所述模拟处理电路通过所述混合键合走线连接。

13、可选地,所述模拟处理电路邻接于或连接所述像素阵列的三个相邻侧边设置,所述三个相邻侧边包括相对的两个列选侧边和一个行选侧边(以使所述模拟处理电路同时量化读取两列像素信号)。

14、可选地,所述帧缓存电路的面积大于所述模拟处理电路的总面积,所述帧缓存电路的面积大于所述数字处理电路的总面积。

15、可选地,所述帧缓存电路将一帧图像的行量化信号逐行缓存为一帧图像的行缓存信号,以获取并发送帧缓存信号至所述数字处理电路;

16、和/或,所述帧缓存电路将一帧图像的行量化信号逐行缓存为多个行缓存信号,以获取并分别发送每个行缓存信号至所述数字处理电路。

17、如上所述,本申请提供的基于堆栈式工艺的图像传感器,通过在第一层硅片上设置像素阵列,在第二层硅片上直接设置帧缓存电路,能够通过硅片上的金属走线直接连接,像素阵列设计简单,在像素区域和电路区域面积增大的同时,提高信号处理速度,实现高帧率量化,达到类似全局快门的图像效果。

技术特征:

1.一种基于堆栈式工艺的图像传感器,其特征在于,包括:像素阵列、模拟处理电路、数字处理电路、混合键合走线和帧缓存电路;

2.如权利要求1所述的图像传感器,其特征在于,所述模拟处理电路包括互相连接的行驱动单元和量化单元,所述行驱动单元用于将每行像素的感光电压驱动输出至所述量化单元,以使所述量化单元对所述感光电压进行量化读取。

3.如权利要求1所述的图像传感器,其特征在于,组织成行及列的所述像素阵列矩形设置于所述第一层硅片的中心。

4.如权利要求3所述的图像传感器,其特征在于,所述模拟处理电路部分或全部设置在所述第一层硅片上,且所述模拟处理电路邻接于所述像素阵列的至少两个相邻侧边;或,

5.如权利要求4所述的图像传感器,其特征在于,部分或全部设置在所述第二层硅片上的所述模拟处理电路邻接于所述帧缓存电路的至少一侧边;或,

6.如权利要求5所述的图像传感器,其特征在于,所述数字处理电路部分或全部设置在所述第二层硅片上,且所述数字处理电路邻接于所述帧缓存电路的至少一侧边;或,

7.如权利要求3所述的图像传感器,其特征在于,设置于同一层硅片的所述数字处理电路与所述模拟处理电路具有至少一邻接侧边;

8.如权利要求3所述的图像传感器,其特征在于,所述模拟处理电路邻接于或连接所述像素阵列的三个相邻侧边设置,所述三个相邻侧边包括相对的两个列选侧边和一个行选侧边。

9.如权利要求3所述的图像传感器,其特征在于,所述帧缓存电路的面积大于所述模拟处理电路的总面积,所述帧缓存电路的面积大于所述数字处理电路的总面积。

10.如权利要求1-9任一项所述的图像传感器,其特征在于,所述帧缓存电路将一帧图像的行量化信号逐行缓存为一帧图像的行缓存信号,以获取并发送帧缓存信号至所述数字处理电路;

技术总结

本申请提供一种基于堆栈式工艺的图像传感器,包括:像素阵列、模拟处理电路、数字处理电路、混合键合走线和帧缓存电路;所述图像传感器包括第一层硅片和第二层硅片,所述第一层硅片与所述第二层硅片通过设置于所述图像传感器边缘的金所述混合键合走线连接,所述像素阵列设置于所述第一层硅片,所述帧缓存电路设置于所述第二层硅片。本申请提供的基于堆栈式工艺的图像传感器,通过在第一层硅片上设置像素阵列,在第二层硅片上直接设置帧缓存电路,能够通过硅片上的金属走线直接连接,像素阵列设计简单,在像素区域和电路区域面积增大的同时,提高信号处理速度,实现高帧率量化。

技术研发人员:徐辰,王锋奇,侯金剑,任冠京,莫要武

受保护的技术使用者:思特威(上海)电子科技股份有限公司

技术研发日:

技术公布日:2024/1/15

- 还没有人留言评论。精彩留言会获得点赞!