连续时间线性均衡器和包括其的装置的制作方法

本发明构思的各示例实施例涉及一种连续时间线性均衡器(ctle),更具体地说,涉及一种用于执行均衡化的ctle装置、一种操作ctle装置的方法、和/或包括其的系统等。

背景技术:

1、随着数据技术的最新发展,需要在装置之间交换大量数据,因此,需要和/或要求平滑数据交换的接口技术。装置可以通过传输数据信号的通道相互连接。然而,由于诸如集肤效应和介电损耗的各种原因,通过通道传输的数据信号可包括诸如码间干扰(isi)之类的噪声,因此,高速传输的数据信号的质量可能会降低。

2、为了提高交换数据信号的质量,装置可包括ctle、判决反馈均衡器(dfe)等。ctle可以支持诸如测试模式和正常模式的各种模式中的均衡化。支持各种模式所需的电路配置可能增加ctle的内部电容,并限制和/或减少ctle的工作频率带宽。

技术实现思路

1、本发明构思的各种示例实施例提供了一种被配置为通过在执行均衡化时减少、减小和/或最小化内部寄生电容来提高工作频率带宽的连续时间线性均衡器(ctle)、一种操作ctle的方法、和/或包括其的系统。

2、根据本发明构思的至少一个示例实施例,提供了一种包括接收器模拟前端电路的装置,该接收器模拟前端电路包括由内部回环电流路径和校准电流路径共享的路径,其中接收器模拟前端电路被配置为在测试模式时利用内部回环电流路径执行内部测试,并且在正常模式时均衡第一数据信号,均衡第一数据信号的步骤包括利用校准电流路径从第一数据信号中去除偏移。

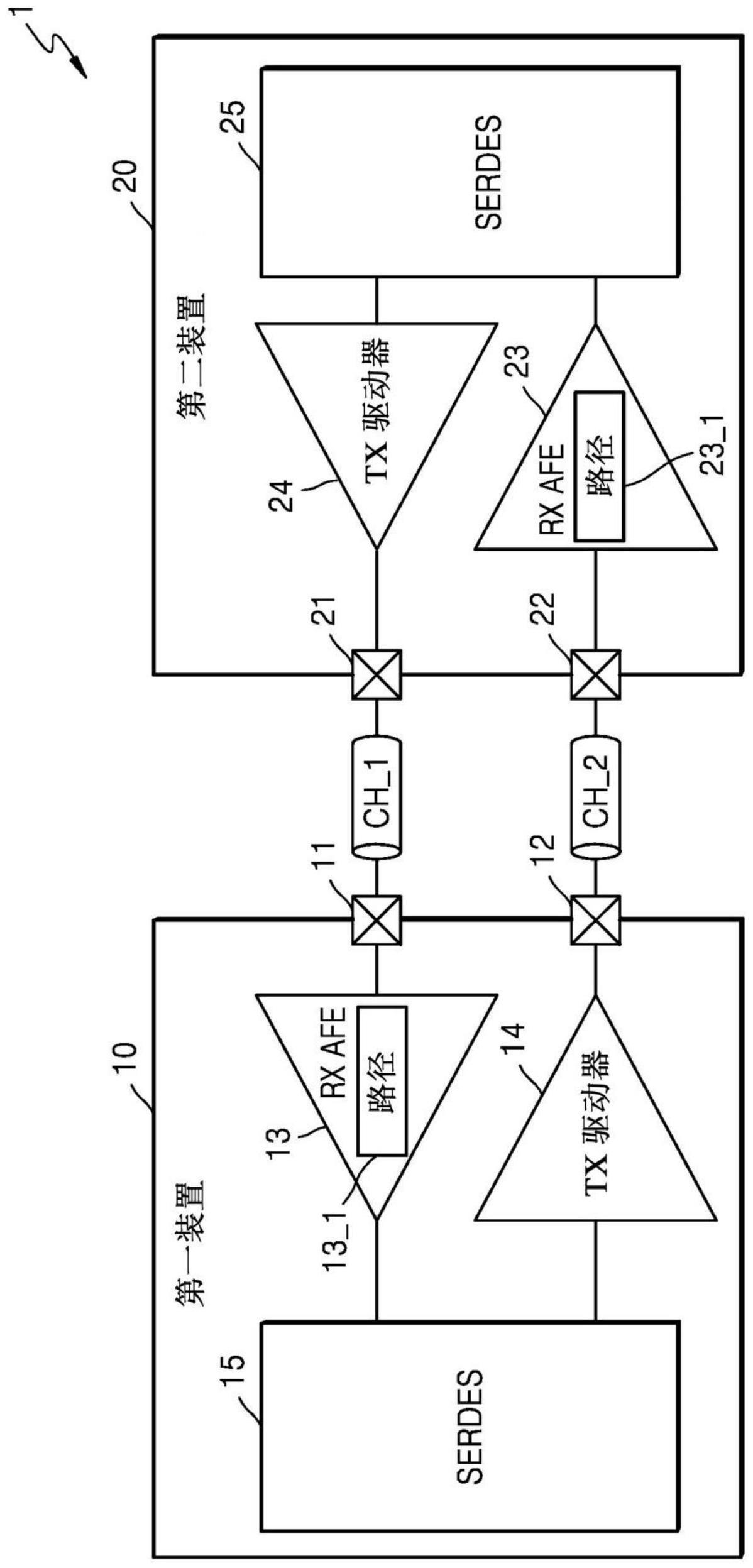

3、根据本发明构思的至少一个示例实施例,提供了一种装置,该装置包括:接收器模拟前端电路,其被配置为均衡第一数据信号;发送器驱动器电路,其被配置为将第二数据信号发送至外部目的地;串行器/解串行器(serdes)电路,其被配置为将从接收器模拟前端电路提供的均衡的第一数据信号并行化,或者将发第二数据信号串行化并提供至发送器驱动器电路;以及控制器,其被配置为控制接收器模拟前端电路和serdes电路,以将内部回环电流路径或校准电流路径启用,其中接收器模拟前端电路还被配置为在测试模式时使用内部回环电流路径测试接收器模拟前端电路和serdes电路,以及在正常模式时使用校准电流路径通过从第一数据信号中去除偏移将第一数据信号均衡,并且接收器模拟前端电路包括与内部回环电流路径和校准电流路径之间共享的路径相对应的多个第一晶体管。

4、根据本发明构思的至少一个示例实施例,提供了一种ctle,该ctle包括:高频滤波器电路,其被配置为接收第一正输入和第一负输入,并且基于第一正输入和第一负输入输出正选择输入和负选择输入;固定增益放大器电路,其被配置为从高频滤波器电路接收第二正输入、第二负输入、正选择输入和负选择输入;以及可变增益放大器电路,其被配置为从固定增益放大器电路接收第三正输入和第三负输入,其中,固定增益放大器电路包括:第一电流源,其被配置为放大第二正输入或第二负输入;第二电流源,其被配置为从第三正输入和第三负输入中去除偏移;多个第一晶体管,其被配置为响应于第二正输入或第二负输入从第一电流源开始形成第一路径;多个第二晶体管,其被配置为响应于正选择输入或负选择输入从第二电流源开始形成第二路径;多个第三晶体管,其被配置为响应于模式选择信号从第一电流源开始生成第三路径,并且正选择输入和负选择输入在ctle处于测试模式时对应于内部测试数据并且在ctle处于正常模式时对应于偏移数据。

5、根据本发明构思的至少一个示例实施例,提供了一种接收器模拟前端电路,该接收器模拟前端电路包括:ctle,其被配置为均衡第一数据信号;判决反馈均衡器(dfe),其被配置为均衡第二数据信号;时钟恢复电路,其被配置为从均衡的第一数据信号中恢复时钟信号;求和电路,其被配置为通过对均衡的第一数据信号和均衡的第二数据信号求和来生成第三数据信号;以及判决电路,其被配置为利用时钟信号通过对第三数据信号采样生成第二数据信号,其中,ctle包括在内部回环电流路径与校准电流路径之间共享的路径,并且ctle还被配置为在测试模式时针对内部测试启用内部回环电流路径,以及在ctle处于正常模式时启用校准电流路径并且通过从ctle的输出中去除偏移来均衡第一数据信号。

技术特征:

1.一种装置,包括:

2.根据权利要求1所述的装置,其中,所述路径包括多个第一晶体管,并且

3.根据权利要求2所述的装置,其中,所述接收器模拟前端电路还被配置为:基于模式选择信号将所述内部测试数据或者所述偏移数据选择性地发送至所述多个第一晶体管。

4.根据权利要求1所述的装置,其中,所述接收器模拟前端电路还包括:

5.根据权利要求4所述的装置,其中,所述连续时间线性均衡器包括:

6.根据权利要求5所述的装置,其中,所述高频滤波器电路被配置为响应于所述接收器模拟前端电路处于所述测试模式而被去激活,并且响应于所述接收器模拟前端电路处于所述正常模式而被激活。

7.根据权利要求5所述的装置,其中,所述固定增益放大器电路包括:

8.根据权利要求7所述的装置,其中,所述接收器模拟前端电路还被配置为:

9.根据权利要求1所述的装置,还包括:

10.根据权利要求1所述的装置,还包括:

11.根据权利要求1所述的装置,还包括:

12.一种装置,包括:

13.根据权利要求12所述的装置,其中,所述控制器还被配置为:

14.根据权利要求13所述的装置,其中,

15.根据权利要求14所述的装置,其中,所述接收器模拟前端电路还包括:

16.根据权利要求12所述的装置,其中,所述接收器模拟前端电路还包括:

17.根据权利要求16所述的装置,其中,所述连续时间线性均衡器包括:

18.一种连续时间线性均衡器,包括:

19.根据权利要求18所述的连续时间线性均衡器,其中,

20.根据权利要求18所述的连续时间线性均衡器,其中,所述高频滤波器电路包括多个第四晶体管,每个第四晶体管被配置为通过相应栅极端子接收所述第一正输入或所述第一负输入,并且

技术总结

提供了一种装置、一种接收器模拟前端电路和一种连续时间线性均衡器。该装置包括接收器模拟前端电路,该接收器模拟前端电路包括由内部回环电流路径和校准电流路径共享的路径,其中接收器模拟前端电路被配置为在测试模式时利用内部回环电流路径执行内部测试,并且在正常模式时均衡第一数据信号,均衡第一数据信号的步骤包括利用校准电流路径从第一数据信号中去除偏移。

技术研发人员:宋镐彬,南润瑾,朴炳珪,朴宰贤,朴河贞,裴俊汉

受保护的技术使用者:三星电子株式会社

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!