一种时钟同步装置、设备及车辆的制作方法

本说明书涉及电子,尤其涉及一种时钟同步装置、设备及车辆。

背景技术:

1、随着无人驾驶车辆上传感器数量的增加以及传感器帧率的不断提高,控制系统对时钟同步精度的要求也会随之增加,时钟同步精度的要求会从ms级别升级到us,甚至是ns级别。

2、由于在时钟长期偏移的情况下,车辆本地时间和服务器时间之间的误差会逐渐增加。比如,若普通晶振频偏在±30ppm,以常规的50mhz的晶体为例,极端情况下一天24小时的频率偏移会到达2.1秒,严重影响车辆驾驶安全。

3、为了保持时钟同步,传统的时钟保持方案采用oxco(oven controlled crystaloscillator,恒温晶体振荡器)按照标准频率提供时钟源,结合系统级芯片soc/现场可编程门阵列fpga对外设同步授时。

4、因oxco时钟源会逐渐偏差,为了和全球定位系统gps时钟同步,soc/fpga通过计算gps生成的pps(pulses per second,每秒脉冲数)时间间隔和ocxo的时间得出差值,利用数字模拟转换器dac调整ocxo压控引脚的电压,从而调整ocxo的输出频率,使其达到标准频率。

5、因传统的时钟保持方案使用了oxco、soc、fpga、dac等器件,使得传统的时钟保持方案的环路控制设计复杂,在设计时需要考虑诸多因素,例如需要考虑ocxo的频偏特性,参考电平的温漂特性,dac输出特性等等才能维持时钟同步的精度,导致传统的时钟保持方案在实际使用中普适性不强。

技术实现思路

1、本说明书提供了一种时钟同步装置、设备及车辆,以解决或者部分解决传统的时钟保持方案的环路控制设计复杂,普适性不强的技术问题。

2、为解决上述技术问题,本说明书的第一方面,公开了一种时钟同步装置,所述时钟同步装置包括:晶振,gps组件,微处理器芯片;其中,所述晶振和所述gps组件均连接所述微处理器芯片;

3、所述晶振,用于产生周期性振荡;

4、在所述微处理器芯片中,具有:

5、时间戳生成组件,用于基于所述晶振的振荡周期,每隔1秒时钟计数值产生一次pps信号对各外部设备进行本地时钟授时;

6、时间差解析组件,和所述gps组件连接,用于接收所述gps组件发送的gps报文并从中解析出gps时间,基于所述gps时间和本地时钟授时的时间计算出时间差;

7、处理组件,用于参考所述时间差,通过pid算法调整所述1秒时钟计数值;

8、所述时间戳生成组件,还用于根据调整后的1秒时钟计数值控制所述pps信号的输出频率,以使所述本地时钟授时的时间和所述gps时间保持同步。

9、优选的,所述时间差解析组件,还用于从所述gps报文中解析出gps状态;

10、所述处理组件,还用于定时获取所述gps状态并判断所述gps状态是否为锁定状态;若是,则不处理;若否,参考所述时间差,通过所述pid算法调整所述1秒时钟计数值。

11、优选的,所述pps信号的输出频率为所述晶振的振荡周期和1秒时钟计数值的乘积的倒数。

12、优选的,时间戳生成组件,具体用于基于所述晶振的振荡周期,每隔所述1秒时钟计数值同时产生一次pps信号和一次gprmc信号对所述各外部设备进行本地时钟授时。

13、优选的,所述微处理器芯片还包括:寄存器组件,分别连接所述时间戳生成组件、所述时间差解析组件、所述处理组件;

14、所述寄存器组件,用于存储所述gps报文、所述时间差、所述调整后的1秒时钟计数值中的一种或者多种。

15、优选的,所述微处理器芯片还包括:倍频组件,连接所述晶振,用于在同步精度未达标时,对所述晶振的振荡周期进行倍频。

16、优选的,所述微处理器芯片采用现场可编程门阵列fpga芯片。

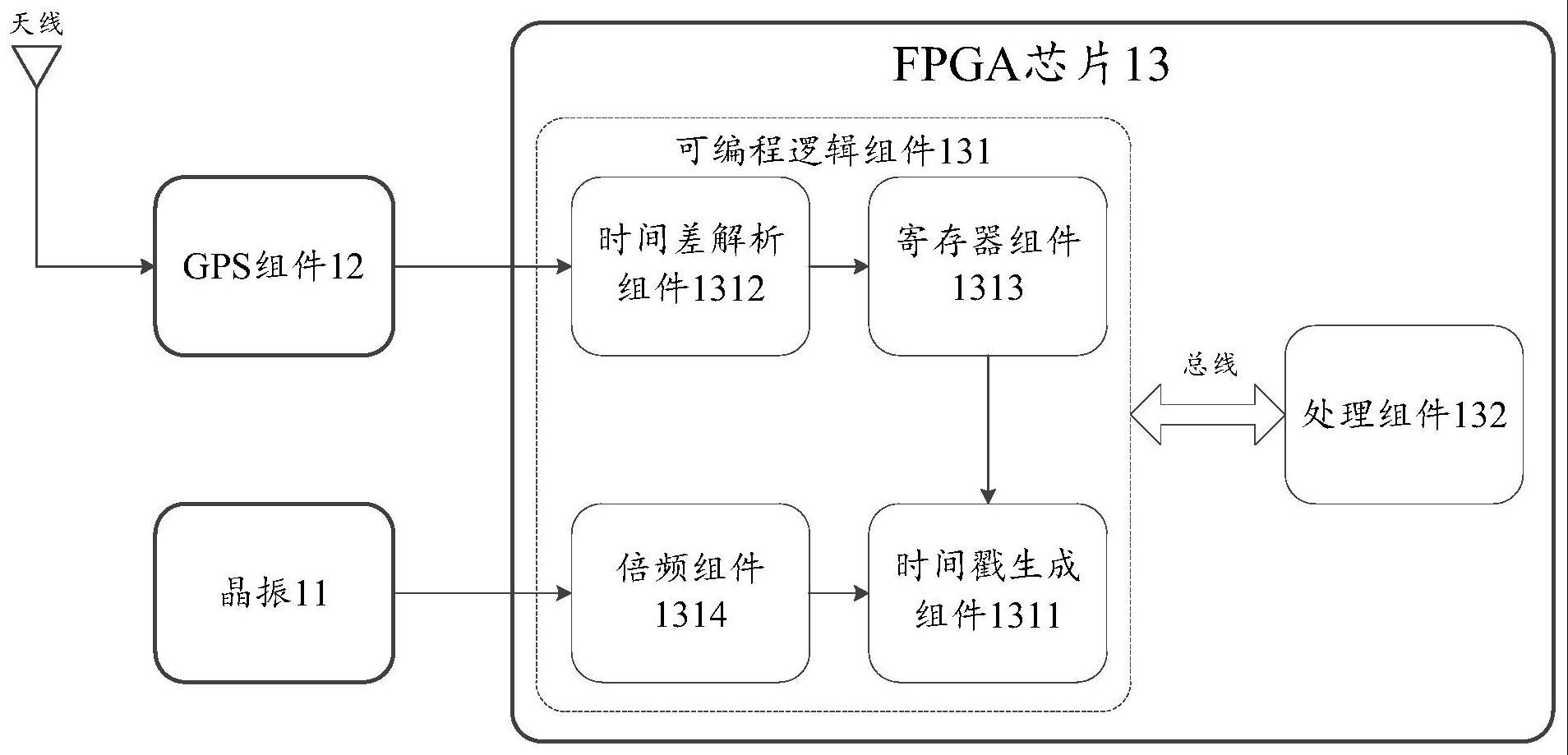

17、优选的,所述fpga芯片包括:可编程逻辑组件和所述处理组件;所述可编程逻辑组件和所述处理组件通过总线连接;

18、其中,所述时间戳生成组件,所述时间差解析组件,所述寄存器组件,所述倍频组件均隶属于所述可编程逻辑组件。

19、本说明书的第二方面,公开了一种设备,包括前述任一技术方案所述的时钟同步装置。

20、本说明书的第二方面,公开了一种车辆,包括前述任一技术方案所述的时钟同步装置。

21、通过本说明书的一个或者多个实施例,本说明书具有以下有益效果或者优点:

22、本说明书中的时钟同步方案,仅采用晶振,gps组件,微处理器芯片的配合实现时钟同步。相比于传统时钟保持方案需要考虑ocxo的频偏特性,参考电平的温漂特性,dac输出特性等等诸多因素,因本说明书的时钟同步装置结构简单,变量只有晶振的温漂,在实际测试过程仅采用单环pid控制即可实现高精度的时钟保持,相比传统时钟保持方案普适性更强,适合广泛推广应用。

23、本说明书中的时钟同步方案,在不改变晶振振荡周期的基础上,通过调整1秒钟时钟计数值即可调整pps的输出频率以及屏蔽不同晶振之间的个体差异,能够保持本地时钟授时的稳定性。

24、相比于传统时钟同步方案采用ocxo、dac的高成本器件,本说明书的时钟同步方案中采用的器件均为低成本普通器件,通过低成本普通器件即可实现高精度时钟同步,相比于传统时钟同步方案,本方案提供的时钟同步装置更有利于广泛推广应用。

25、上述说明仅是本说明书技术方案的概述,为了能够更清楚了解本说明书的技术手段,而可依照说明书的内容予以实施,并且为了让本说明书的上述和其它目的、特征和优点能够更明显易懂,以下特举本说明书的具体实施方式。

技术特征:

1.一种时钟同步装置,所述时钟同步装置包括:晶振,gps组件,微处理器芯片;其中,所述晶振和所述gps组件均连接所述微处理器芯片;

2.如权利要求1所述的时钟同步装置,

3.如权利要求1所述的时钟同步装置,所述pps信号的输出频率为所述晶振的振荡周期和1秒时钟计数值的乘积的倒数。

4.如权利要求1所述的时钟同步装置,时间戳生成组件,具体用于基于所述晶振的振荡周期,每隔所述1秒时钟计数值同时产生一次pps信号和一次gprmc信号对所述各外部设备进行本地时钟授时。

5.如权利要求1所述的时钟同步装置,所述微处理器芯片还包括:寄存器组件,分别连接所述时间戳生成组件、所述时间差解析组件、所述处理组件;

6.如权利要求5所述的时钟同步装置,所述微处理器芯片还包括:倍频组件,连接所述晶振,用于在同步精度未达标时,对所述晶振的振荡周期进行倍频。

7.如权利要求6所述的时钟同步装置,所述微处理器芯片采用现场可编程门阵列fpga芯片。

8.如权利要求7所述的时钟同步装置,所述fpga芯片包括:可编程逻辑组件和所述处理组件;所述可编程逻辑组件和所述处理组件通过总线连接;

9.一种设备,包括如权利要求1-8任一项所述的时钟同步装置。

10.一种车辆,包括如权利要求1-8任一项所述的时钟同步装置。

技术总结

本说明书公开了一种时钟同步装置,包括:晶振,GPS组件,微处理器芯片;其中,晶振和GPS组件均连接微处理器芯片;晶振,用于产生周期性振荡;在微处理器芯片中,具有:时间戳生成组件,用于基于晶振的振荡周期,每隔1秒时钟计数值产生一次pps信号对各外部设备进行本地时钟授时;时间差解析组件,和GPS组件连接,用于接收GPS组件发送的GPS报文并从中解析出GPS时间,基于GPS时间和本地时钟授时的时间计算出时间差;处理组件,用于参考时间差,通过PID算法调整1秒时钟计数值;时间戳生成组件,还用于根据调整后的1秒时钟计数值控制pps信号的输出频率,以使本地时钟授时的时间和GPS时间保持同步。

技术研发人员:张成华,蔡俊杰,秦朋来,王晋伟,王斌,陈先强,顾敏奇,李绍良

受保护的技术使用者:斑马网络技术有限公司

技术研发日:

技术公布日:2024/1/11

- 还没有人留言评论。精彩留言会获得点赞!