基于FPGA的视频帧率动态转换方法、装置及存储介质与流程

本发明涉及视频帧率转换,尤其涉及基于fpga的视频帧率动态转换方法、装置及存储介质。

背景技术:

1、目前大多数的视频帧率变换,可以实现固定帧率之间的转换,比如将30hz转换成60hz;将60hz转换成30hz。如果处理其他帧率,比如25hz,27hz,75hz等等比较少见的帧率之间的转换,每次转换时都需要针对每一种帧率进行不同的控制算法的开发,才能实现相应帧率的转换,软件成本大,不利于节省资源,降低系统性能。

技术实现思路

1、为了克服现有技术的不足,本发明的目的之一在于提供基于fpga的视频帧率转换方法,其能够解决现有技术中对于每种视频帧率在转换时均需要不同的控制算法才能实现导致软件成本大、系统性能低下等问题。

2、本发明的目的之二在于提供基于fpga的视频帧率转换装置,其能够解决现有技术中对于每种视频帧率在转换时均需要不同的控制算法才能实现导致软件成本大、系统性能低下等问题。

3、本发明的目的之三在于提供一种计算机可读存储介质,其能够解决现有技术中对于每种视频帧率在转换时均需要不同的控制算法才能实现导致软件成本大、系统性能低下等问题。

4、本发明的目的之一采用如下技术方案实现:

5、基于fpga的视频帧率动态转换方法,所述视频帧率动态转换方法包括:

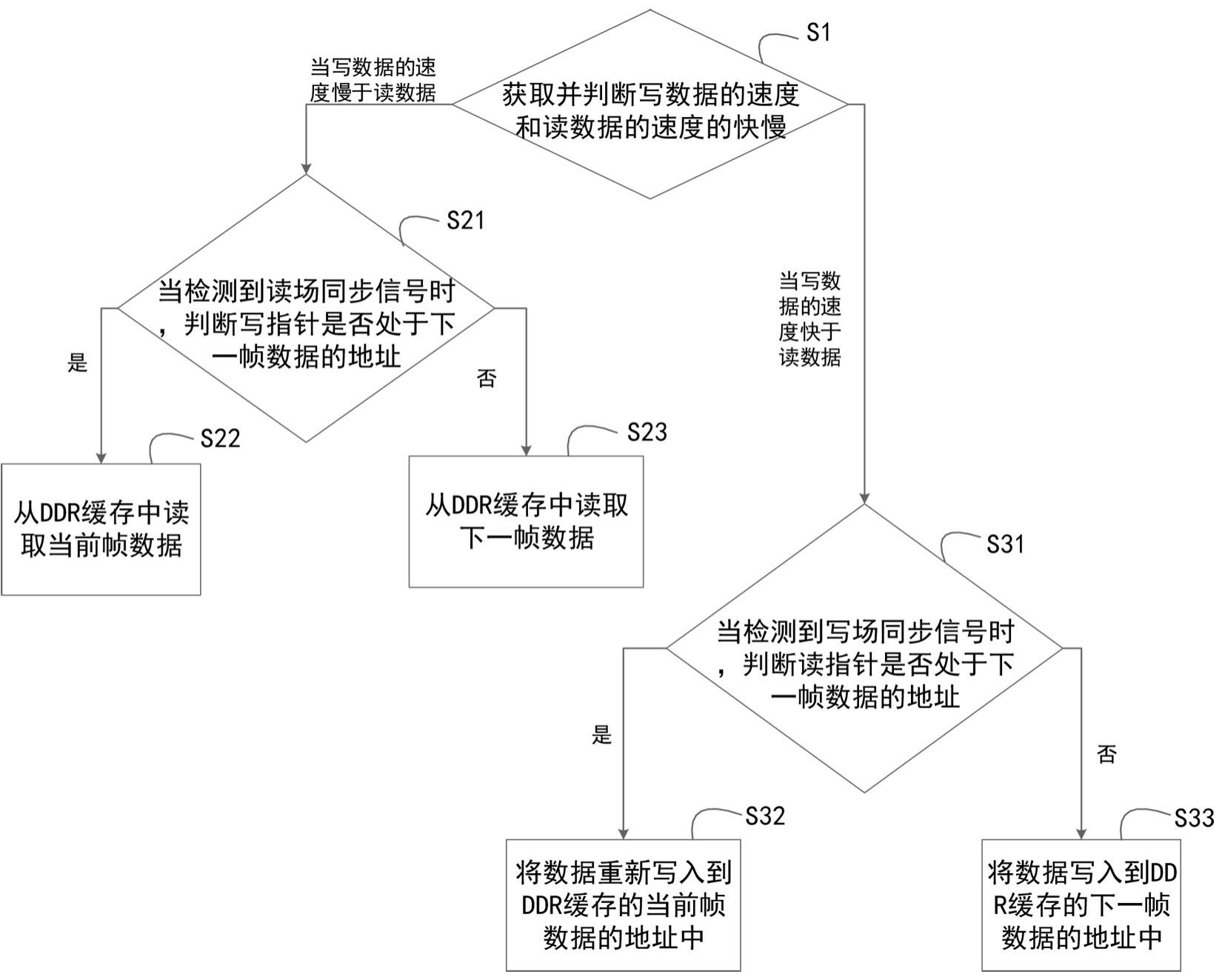

6、读写速度判断步骤:判断写数据的速度与读数据的速度的快慢,以及当写数据的速度慢于读数据的速度时,执行重读机制步骤;当写数据的速度快于读数据的速度时,执行重写机制步骤;

7、重读机制步骤:当检测到读场同步信号时,判断写指针是否处于下一帧数据的地址,若是,则从ddr缓存中读取当前帧数据;若否,则从ddr缓存中读取下一帧数据;

8、重写机制步骤:当检测到写场同步信号时,判断读指针是否处于下一帧数据的地址,若是,则将数据重新写入到ddr缓存的当前帧数据的地址中;若否,则将数据写入到ddr缓存的下一帧数据的地址中。

9、进一步地,所述读写速度判断步骤中判断写数据的速度与读数据的速度的快慢具体根据写入一帧数据的时间与读取一帧数据的时间的大小判断得出。

10、进一步地,所述读写速度判断步骤具体包括:

11、写入一帧数据计算步骤:获取写入相邻两帧数据时的写场同步信号并根据两个写读场同步信号的获取时间计算得出写入一帧数据的时间;

12、读取一帧数据计算步骤:获取读取相邻两帧数据时的读场同步信号并根据两个读场同步信号的获取时间计算得出读取一帧数据的时间;

13、比较步骤:判断写入一帧数据的时间是否大于读取一帧数据的时间,若是,则写数据的速度慢于读数据的速度,执行重读机制步骤;若否,则写数据的速度快于读数据的速度,执行重写机制步骤。

14、进一步地,所述重读机制步骤中:当写指针处于下一帧数据的地址时,将读指针不变,读地址指向当前帧数据的地址开头并从ddr缓存中读取对应视频数据并显示;当写指针未处于下一帧数据的地址时,读指针+1,读地址指向下一帧数据的地址开头并从ddr缓存中读取到对应视频数据并显示。

15、进一步地,所述重写机制步骤中:当读指针处于下一帧数据的地址时,将写指针不变,写地址指向当前帧数据的地址开头并将对应视频数据写入到ddr缓存中;当读指针未处于下一帧数据的地址时,将写指针+1,写地址指向下一帧数据的地址开头并将对应视频数据写入到ddr缓存中。

16、进一步地,所述重读机制步骤还包括:写数据步骤:当检测到写场同步信号时,将写指针+1,写地址指向下一帧数据的地址开头并将对应视频数据写入到ddr缓存中。

17、进一步地,所述重写机制步骤还包括:读数据步骤:当检测到读场同步信号时,将读指针+1,读地址指向下一帧数据的地址开头并从ddr缓存中读取对应视频数据后显示。

18、进一步地,所述ddr缓存的存储空间至少包括3帧视频数据的存储空间。

19、本发明的目的之二采用如下技术方案实现:

20、基于fpga的视频帧率动态转换装置,包括存储器和处理器,所述存储器上存储有在处理器上运行的视频帧率动态转换程序,所述视频帧率动态转换程序为计算机程序,所述处理器执行所述视频帧率动态转换程序时实现如本发明的目的之一采用的基于fpga的视频帧率动态转换方法的步骤。

21、本发明的目的之三采用如下技术方案实现:

22、一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序为视频帧率动态转换程序,所述视频帧率动态转换程序被处理器执行时实现如本发明的目的之一采用的基于fpga的视频帧率动态转换方法的步骤。

23、相比现有技术,本发明的有益效果在于:

24、本发明在进行视频帧率转换时,通过利用fpga读写ddr地址的控制,结合ddr缓存可实现任意视频帧率的转换,从而保证读写速度不匹配时保证读写数据的正确性,同时避免显示画面撕裂或闪烁、或者丢弃数据等,不需额外的视频格式转换工具,以解决现有技术中针对每个视频帧率都需要制定一套对应的控制算法才能实现数据的正确读写的问题。

技术特征:

1.基于fpga的视频帧率动态转换方法,其特征在于,所述视频帧率动态转换方法包括:

2.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述读写速度判断步骤中判断写数据的速度与读数据的速度的快慢具体根据写入一帧数据的时间与读取一帧数据的时间的大小判断得出。

3.根据权利要求2所述的基于fpga的视频帧率动态转换方法,其特征在于,所述读写速度判断步骤具体包括:

4.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述重读机制步骤中:当写指针处于下一帧数据的地址时,将读指针不变,读地址指向当前帧数据的地址开头并从ddr缓存中读取对应视频数据并显示;当写指针未处于下一帧数据的地址时,读指针+1,读地址指向下一帧数据的地址开头并从ddr缓存中读取到对应视频数据并显示。

5.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述重写机制步骤中:当读指针处于下一帧数据的地址时,将写指针不变,写地址指向当前帧数据的地址开头并将对应视频数据写入到ddr缓存中;当读指针未处于下一帧数据的地址时,将写指针+1,写地址指向下一帧数据的地址开头并将对应视频数据写入到ddr缓存中。

6.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述重读机制步骤还包括:写数据步骤:当检测到写场同步信号时,将写指针+1,写地址指向下一帧数据的地址开头并将对应视频数据写入到ddr缓存中。

7.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述重写机制步骤还包括:读数据步骤:当检测到读场同步信号时,将读指针+1,读地址指向下一帧数据的地址开头并从ddr缓存中读取对应视频数据后显示。

8.根据权利要求1所述的基于fpga的视频帧率动态转换方法,其特征在于,所述ddr缓存的存储空间至少包括3帧视频数据的存储空间。

9.基于fpga的视频帧率动态转换装置,包括存储器和处理器,所述存储器上存储有在处理器上运行的视频帧率动态转换程序,所述视频帧率动态转换程序为计算机程序,其特征在于,所述处理器执行所述视频帧率动态转换程序时实现如权利要求1-8中任意一项所述的基于fpga的视频帧率动态转换方法的步骤。

10.一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序为视频帧率动态转换程序,其特征在于,所述视频帧率动态转换程序被处理器执行时实现如权利要求1-8中任意一项所述的基于fpga的视频帧率动态转换方法的步骤。

技术总结

本发明公开了基于FPGA的视频帧率动态转换方法、装置及存储介质,方法包括:判断写数据的速度与读数据的速度的快慢,以及若写数据的速度慢于读数据的速度,执行重读机制步骤;反之,执行重写机制步骤;重读机制步骤:当检测到读场同步信号时,判断写指针是否处于下一帧数据的地址,若是,则从DDR缓存中读取当前帧数据;若否,则从DDR缓存中读取下一帧数据;重写机制步骤:当检测到写场同步信号时,判断读指针是否处于下一帧数据的地址,若是,则将数据重新写入到DDR缓存的当前帧数据的地址中;若否,则将数据写入到DDR缓存的下一帧数据的地址中,能够解决不同视频帧率的动态转换,以解决读写速度不匹配时导致读写错误的问题。

技术研发人员:黄兆锦,于志军

受保护的技术使用者:广州美凯信息技术股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!