一种数据加密装置的制作方法

本发明涉及信息安全,特别涉及一种数据加密装置。

背景技术:

1、密码杂凑算法被广泛应用于数字签名和验证、消息认证码的生成和验证及随机数的生成等方面,满足了多种密码应用的安全需求。其中,sm3密码算法是我国应用较为广泛的密码杂凑算法。hmac(hash-based message authentication code,哈希消息认证码)是一种基于哈希函数和密钥进行数据加密的方法,在ipsec和其他网络协议(如ssl)中得到广泛应用,密码杂凑算法和hmac都需要经过哈希运算。现有的安全ip核中的hmac算法和哈希算法分属于两个哈希模块,造成硬件冗余,对于硬件资源消耗较大。

技术实现思路

1、有鉴于此,本发明的目的在于提供一种数据加密装置,能够同时支持哈希算法和hmac运算,两种运算复用一个哈希算法模块,结构简单,易实现,硬件成本降低。其具体方案如下:

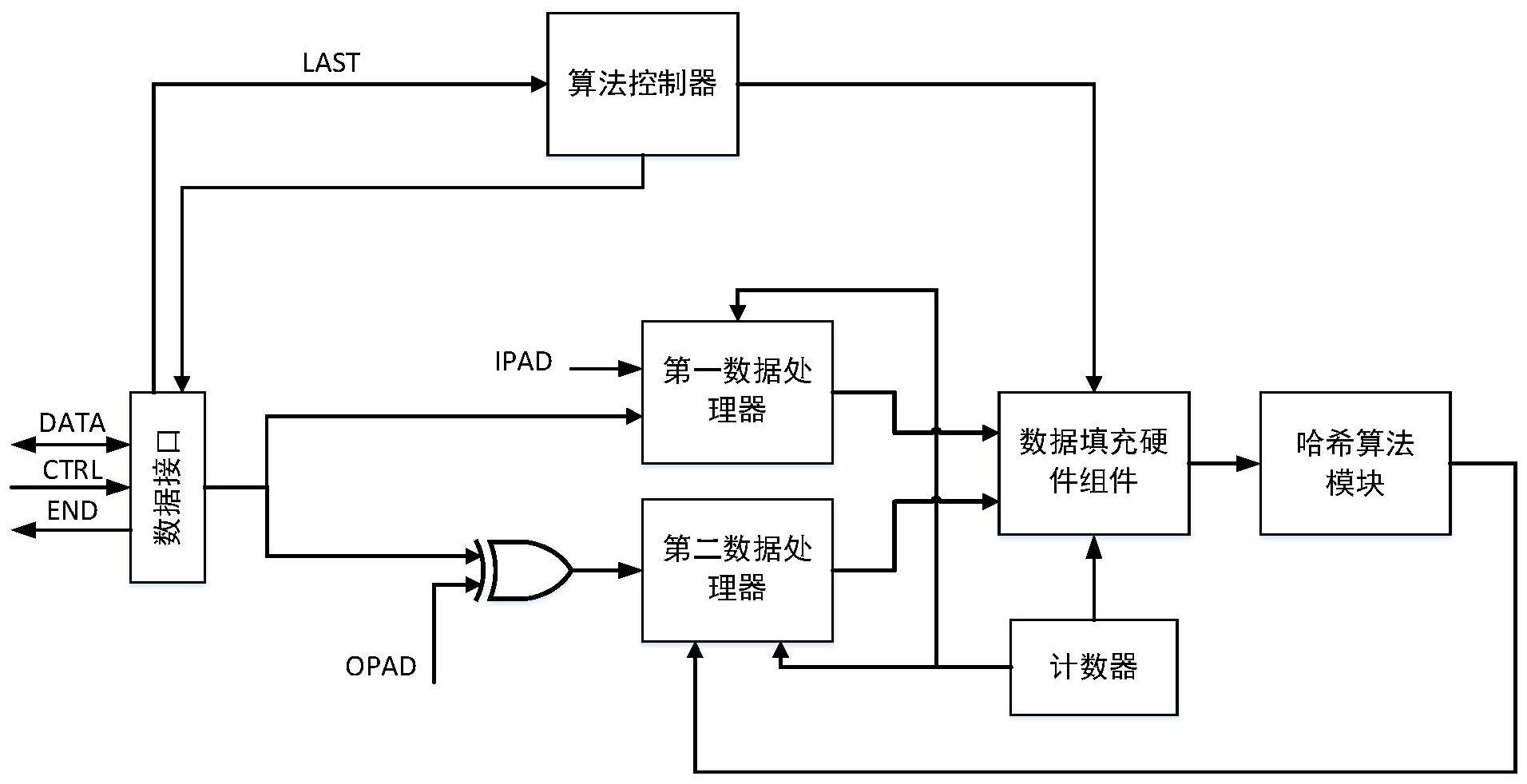

2、本申请的第一方面提供了一种数据加密装置,所述数据加密装置包括数据接口和哈希算法模块,其中:

3、所述数据接口,用于接收输入数据和模式控制信号;

4、所述哈希算法模块,用于在哈希模式下对所述输入数据进行哈希运算得到对应的哈希加密运算结果;

5、所述哈希算法模块,还用于在hmac模式下进行hmac算法的哈希运算得到与所述输入数据对应的hmac加密运算结果。

6、可选的,所述数据加密装置还包括还包括数据填充硬件组件和算法控制器;

7、所述数据填充硬件组件,用于执行所述哈希算法模块在哈希模式或hmac模式下的哈希运算过程中的数据填充步骤;

8、所述算法控制器,用于控制所述数据填充硬件组件执行数据填充步骤;

9、所述算法控制器,还用于根据所述模式控制信号开启或终止所述哈希算法模块的哈希运算。

10、可选的,所述数据加密装置还包括第一数据处理器和第二数据处理器;

11、所述第一数据处理器,用于当所述哈希算法模块在hmac模式下进行hmac算法的第一轮哈希运算时,对hmac算法的第一轮哈希运算中的异或计算进行处理;

12、所述第二数据处理器,用于当所述哈希算法模块在hmac模式下进行hmac算法的第二轮哈希运算时,对hmac算法的第二轮哈希运算中的异或计算进行处理;

13、相应的,所述数据填充硬件组件,分别用于执行hmac算法的第一轮哈希运算和hmac算法的第二轮哈希运算中的数据填充步骤。

14、可选的,所述第一数据处理器,用于对所述输入数据中的目标密钥与ipad字符串进行异或计算处理,得到第一异或结果;

15、所述数据填充硬件组件,用于将所述第一异或结果进行第一数据填充,并利用剩余数据进行第二数据填充;

16、所述哈希算法模块,用于在第二数据填充完成后进行hmac算法的第一轮哈希运算。

17、可选的,所述第二数据处理器,用于对所述输入数据中的目标密钥与opad字符串进行异或计算处理,得到第二异或结果;

18、所述数据填充硬件组件,用于将所述第二异或结果进行第三数据填充;

19、所述哈希算法模块,用于在第三数据填充完成后进行hmac算法的第二轮哈希运算。

20、可选的,所述第二数据处理器,还用于在对所述输入数据中的目标密钥与opad字符串进行异或计算处理之前,判断是否为hmac模式且进行第二轮哈希运算,如果是,则执行对所述输入数据中的目标密钥与opad字符串进行异或计算处理的步骤。

21、可选的,所述第二数据处理器通过状态机配置判断是否为hmac模式且进行第二轮哈希运算。

22、可选的,所述数据加密装置还包括计数器;

23、所述计数器,用于对所述数据填充硬件组件从所述第一数据处理器和所述第二数据处理器中接收32比特位数据的数量进行计数。

24、可选的,所述数据加密装置还包括添加在所述哈希算法模块中的进位保留加法器的线性计算路径上的第一奇偶校验组件;

25、所述第一奇偶校验组件,用于将经过所述进位保留加法器处理得到的各与运算结果分别经过奇偶校验数得到相应数量的输出结果,并将相应数量的输出结果进行异或运算得到第一比对值;与运算结果为每两个操作数之间的与运算结果;

26、所述第一奇偶校验组件,还用于将所述第一比对值与第一目标值进行比对,如果所述第一比对值与所述第一目标值一致,则校验通过;其中,所述第一目标值为所述奇偶校验组件将经过所述进位保留加法器处理得到的或运算结果经过一个奇偶校验数得到的输出结果;或运算结果为对每两个操作数之间的与运算结果进行或运算后的结果。

27、可选的,所述数据加密装置还包括添加在所述哈希算法模块中的第一数据选择器和第二数据选择器的线性计算路径上的第二奇偶校验组件;

28、所述第二奇偶校验组件,用于将各路输入数据分别经过奇偶校验数得到相应数量的输出结果,并将相应数量的输出结果输入所述第一数据选择器,得到第二比对值;

29、所述第二奇偶校验组件,还用于将所述第二比对值与第二目标值进行比对,如果所述第二比对值与所述第二目标值一致,则校验通过;其中,所述第二目标值为所述奇偶校验组件对将直接输出结果经过一个奇偶校验数得到的输出结果;直接输出结果为将各路输入数据直接输入所述第二数据选择器得到的相应输出结果。

30、本申请中,数据加密装置包括数据接口和哈希算法模块,其中:所述数据接口,用于接收输入数据和模式控制信号;所述哈希算法模块,用于在哈希模式下对所述输入数据进行哈希运算得到对应的哈希加密运算结果;所述哈希算法模块,还用于在hmac模式下进行hmac算法的哈希运算得到与所述输入数据对应的hmac加密运算结果。本申请实施例通过数据接口的模式控制信号控制哈希算法模块的运算过程,使得哈希算法模块同时支持哈希模式和hmac模式的哈希运算,两种运算复用一个哈希算法模块,结构简单,易实现,降低硬件成本。

技术特征:

1.一种数据加密装置,其特征在于,所述数据加密装置包括数据接口和哈希算法模块,其中:

2.根据权利要求1所述的数据加密装置,其特征在于,所述数据加密装置还包括数据填充硬件组件和算法控制器;

3.根据权利要求1所述的数据加密装置,其特征在于,所述数据加密装置还包括第一数据处理器和第二数据处理器;

4.根据权利要求3所述的数据加密装置,其特征在于,所述第一数据处理器,用于对所述输入数据中的目标密钥与ipad字符串进行异或计算处理,得到第一异或结果;

5.根据权利要求3所述的数据加密装置,其特征在于,所述第二数据处理器,用于对所述输入数据中的目标密钥与opad字符串进行异或计算处理,得到第二异或结果;

6.根据权利要求5所述的数据加密装置,其特征在于,所述第二数据处理器,还用于在对所述输入数据中的目标密钥与opad字符串进行异或计算处理之前,判断是否为hmac模式且进行第二轮哈希运算,如果是,则执行对所述输入数据中的目标密钥与opad字符串进行异或计算处理的步骤。

7.根据权利要求6所述的数据加密装置,其特征在于,所述第二数据处理器通过状态机配置判断是否为hmac模式且进行第二轮哈希运算。

8.根据权利要求3所述的数据加密装置,其特征在于,所述数据加密装置还包括计数器;

9.根据权利要求1至8任一项所述的数据加密装置,其特征在于,所述数据加密装置还包括添加在所述哈希算法模块中的进位保留加法器的线性计算路径上的第一奇偶校验组件;

10.根据权利要求1至8任一项所述的数据加密装置,其特征在于,所述数据加密装置还包括添加在所述哈希算法模块中的第一数据选择器和第二数据选择器的线性计算路径上的第二奇偶校验组件;

技术总结

本申请涉及信息安全技术领域,公开了一种数据加密装置,包括数据接口和哈希算法模块,其中:所述数据接口,用于接收输入数据和模式控制信号;所述哈希算法模块,用于在哈希模式下对所述输入数据进行哈希运算得到对应的哈希加密运算结果;所述哈希算法模块,还用于在HMAC模式下进行HMAC算法的哈希运算得到与所述输入数据对应的HMAC加密运算结果。本申请通过数据接口的模式控制信号控制哈希算法模块的运算过程,使得哈希算法模块同时支持哈希模式和HMAC模式的哈希运算,两种运算复用一个哈希算法模块,结构简单,易实现,降低硬件开销。

技术研发人员:陈子荷,陈晓玲,袁涛

受保护的技术使用者:湖南国科微电子股份有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!