一种图像采集与处理芯片的制作方法

本发明涉及一种图像采集与处理芯片。

背景技术:

1、vps4114a是一款高质量、高性能图像采集与处理芯片。该芯片背后的技术涉及到以下方面:

2、1、高像素传感器技术:vps4114a采用了先进的10亿像素传感器技术,可以捕捉到极其丰富的图像细节,并通过mipi接口以高带宽输出。

3、2、mipi接口技术:mipi接口是一种专门用于移动设备和嵌入式系统的高速串行接口技术。vps4114a采用了mipi接口技术,可以以高速、稳定的方式输出高清图像。

4、3、图像处理技术:vps4114a内部集成了多种先进的图像处理技术,包括噪声滤波、颜色校正、锐化、白平衡、智能补光等。这些技术可以帮助用户快速、准确地处理和分析图像数据。

5、4、高速数据传输技术:vps4114a的输出速率高达48gbps,需要采用高速、稳定的数据传输技术,以确保数据能够在短时间内准确地传输到目标设备。

6、综合这些技术,vps4114a可以实现高质量、高性能的图像采集与处理,广泛应用于高端摄像头、工业视觉、医疗影像等领域。

7、但是现有vps4114a芯片只能进口,价格较高,而且有泄密风险。

8、因此,需要一种新的图像采集与处理芯片以解决上述问题。

技术实现思路

1、本发明的目的在于,克服现有技术中存在的问题,提供一种图像采集与处理芯片。

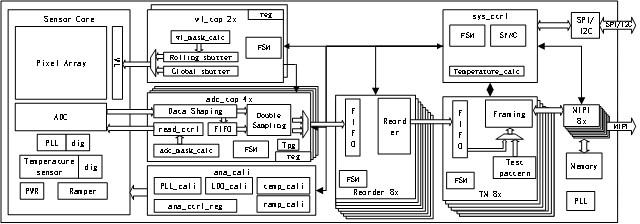

2、本发明的图像采集与处理芯片,包括图像传感器像素阵列、数字控制电路、外围模拟电路和数据输出接口,所述图像传感器像素阵列的两侧均设置有240列的假像素,所述图像传感器像素阵列的有效像素阵列大小为30720x34048,所述图像传感器像素阵列包括像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_4、像素子阵列subarray_5、像素子阵列subarray_6和像素子阵列subarray_7,所述像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_4、像素子阵列subarray_5、像素子阵列subarray_6和像素子阵列subarray_7均包括7800x17024个像素,所述数据输出接口包括mipi接口mipi0、mipi接口mipi1、mipi接口mipi2、mipi接口mipi3、mipi接口mipi4、mipi接口mipi5、mipi接口mipi6和mipi接口mipi7,所述mipi接口mipi0对应所述像素子阵列subarray_0,所述mipi接口mipi1对应所述像素子阵列subarray_1, 所述mipi接口mipi2对应所述像素子阵列subarray_2, 所述mipi接口mipi3对应所述像素子阵列subarray_3,所述mipi接口mipi4对应所述像素子阵列subarray_4,所述mipi接口mipi5对应所述像素子阵列subarray_5,所述mipi接口mipi6对应所述像素子阵列subarray_6,所述mipi接口mipi7对应所述像素子阵列subarray_7,芯片的工作模式包括全采样模式、抽采样模式和开窗模式。

3、更进一步的,所述数字控制电路包括时序控制模块、数据读取模块、数据传输模块、数据处理模块、数据存储模块和通信接口。

4、更进一步的,所述模拟电路包括像素测量与数据生成模块、开关物理实现模块、温度检测模块、电压转换模块和时钟生成模块。

5、更进一步的,所述像素子阵列subarray_2和像素子阵列subarray_0上下镜像对称,所述像素子阵列subarray_3和像素子阵列subarray_1上下镜像对称,所述像素子阵列subarray_6和像素子阵列subarray_4上下镜像对称,所述像素子阵列subarray_7和像素子阵列subarray_5上下镜像对称。

6、更进一步的,当工作模式为全采样模式时,所述像素子阵列subarray_1、像素子阵列subarray_4和像素子阵列subarray_5与所述像素子阵列subarray_0的每行像素读取顺序一致,所述像素子阵列subarray_3、像素子阵列subarray_6和像素子阵列subarray_7与所述像素子阵列subarray_2的每行像素读取顺序一致。

7、更进一步的,当工作模式为全采样模式时,所述像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_4和像素子阵列subarray_5均从第0行向第17023行读取像素,所述像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_6和像素子阵列subarray_7均从第34047行向第17024行读取像素。

8、更进一步的,当工作模式为抽采样模式时,对整个所述图像传感器像素阵列的行和列进行抽采样,只输出抽采样的像素。

9、更进一步的,当工作模式为开窗模式时,在整个所述图像传感器像素阵列里随机开1到16个窗,每个窗的大小为512x512像素。

10、更进一步的,每个像素输出的数据为10bit。

11、更进一步的,所述mipi接口mipi0、mipi接口mipi1、mipi接口mipi2和mipi接口mipi3的数据位宽是64位,芯片内部数据字的位宽是256位,所述芯片内部数据字转换成4个64位串行并通过mipi接口mipi0、mipi接口mipi1、mipi接口mipi2或mipi接口mipi3发送。

12、有益效果:本发明的图像采集与处理芯片将图像传感器的像素阵列分为八个像素子阵列,并在可以在实现10亿像素并通过mipi接口输出48gbps高清图像的高质量、高性能图像采集与处理芯片。

技术特征:

1.一种图像采集与处理芯片,包括图像传感器像素阵列、数字控制电路、外围模拟电路和数据输出接口,其特征在于,所述图像传感器像素阵列的两侧均设置有240列的假像素,所述图像传感器像素阵列的有效像素阵列大小为30720x34048,所述图像传感器像素阵列包括像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_4、像素子阵列subarray_5、像素子阵列subarray_6和像素子阵列subarray_7,所述像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_4、像素子阵列subarray_5、像素子阵列subarray_6和像素子阵列subarray_7均包括7800x17024个像素,所述数据输出接口包括mipi接口mipi0、mipi接口mipi1、mipi接口mipi2、mipi接口mipi3、mipi接口mipi4、mipi接口mipi5、mipi接口mipi6和mipi接口mipi7,所述mipi接口mipi0对应所述像素子阵列subarray_0,所述mipi接口mipi1对应所述像素子阵列subarray_1, 所述mipi接口mipi2对应所述像素子阵列subarray_2, 所述mipi接口mipi3对应所述像素子阵列subarray_3,所述mipi接口mipi4对应所述像素子阵列subarray_4,所述mipi接口mipi5对应所述像素子阵列subarray_5,所述mipi接口mipi6对应所述像素子阵列subarray_6,所述mipi接口mipi7对应所述像素子阵列subarray_7,芯片的工作模式包括全采样模式、抽采样模式和开窗模式。

2.如权利要求1所述图像采集与处理芯片,其特征在于,包括时序控制模块、数据读取模块、数据传输模块、数据处理模块、数据存储模块和通信接口。

3.如权利要求1所述图像采集与处理芯片,其特征在于,所述模拟电路包括像素测量与数据生成模块、开关物理实现模块、温度检测模块、电压转换模块和时钟生成模块。

4.如权利要求1所述图像采集与处理芯片,其特征在于,所述像素子阵列subarray_2和像素子阵列subarray_0上下镜像对称,所述像素子阵列subarray_3和像素子阵列subarray_1上下镜像对称,所述像素子阵列subarray_6和像素子阵列subarray_4上下镜像对称,所述像素子阵列subarray_7和像素子阵列subarray_5上下镜像对称。

5.如权利要求1所述图像采集与处理芯片,其特征在于,当工作模式为全采样模式时,所述像素子阵列subarray_1、像素子阵列subarray_4和像素子阵列subarray_5与所述像素子阵列subarray_0的每行像素读取顺序一致,所述像素子阵列subarray_3、像素子阵列subarray_6和像素子阵列subarray_7与所述像素子阵列subarray_2的每行像素读取顺序一致。

6.如权利要求1所述图像采集与处理芯片,其特征在于,当工作模式为全采样模式时,所述像素子阵列subarray_0、像素子阵列subarray_1、像素子阵列subarray_4和像素子阵列subarray_5均从第0行向第17023行读取像素,所述像素子阵列subarray_2、像素子阵列subarray_3、像素子阵列subarray_6和像素子阵列subarray_7均从第34047行向第17024行读取像素。

7.如权利要求1所述图像采集与处理芯片,其特征在于,当工作模式为抽采样模式时,对整个所述图像传感器像素阵列的行和列进行抽采样,只输出抽采样的像素。

8.如权利要求1所述图像采集与处理芯片,其特征在于,当工作模式为开窗模式时,在整个所述图像传感器像素阵列里随机开1到16个窗,每个窗的大小为512x512像素。

9.如权利要求1所述图像采集与处理芯片,其特征在于,每个像素输出的数据为10bit。

技术总结

本发明公开了一种图像采集与处理芯片,包括图像传感器像素阵列、数字控制电路、外围模拟电路和数据输出接口,所述图像传感器像素阵列的有效像素阵列大小为30720x34048,所述图像传感器像素阵列包括八个像素子阵列,八个像素子阵列分别对应八个MIPI接口。本发明的图像采集与处理芯片将图像传感器的像素阵列分为八个像素子阵列,并在可以在实现10亿像素并通过mipi接口输出48Gbps高清图像的高质量、高性能图像采集与处理芯片。

技术研发人员:黄敏红

受保护的技术使用者:南京威派视半导体技术有限公司

技术研发日:

技术公布日:2024/1/13

- 还没有人留言评论。精彩留言会获得点赞!