基于USB降速桥并应用于USB从机的数据包处理系统、方法、终端及介质与流程

本申请涉及usb通信,特别是涉及基于usb降速桥并应用于usb从机的数据包处理系统、方法、终端及介质。

背景技术:

1、随着电子产品的广泛使用和大量数据传输需求的提升,usb正成为当今应用最广泛的接口之一,因此众多芯片厂商都将usb作为芯片中必不可少的功能之一,而想实现usb功能,必须要使用到usb控制器。当这些芯片厂商在做原型验证时,受制于硬件加速平台的最高工作频率(1~2mhz),必须要使用usb降速桥来适配验证平台极低的工作频率和usb主机的正常工作频率。目前的usb3降速桥屈指可数,即使可以用也只能使用在特定的设备中,并与特定的主机进行连接,只能验证很少一部分基础功能,有很大局限性。

技术实现思路

1、鉴于以上所述现有技术的缺点,本申请的目的在于提供基于usb降速桥并应用于usb从机的数据包处理系统、方法、终端及介质,用于解决如何适配验证平台极低的工作频率和usb主机正常工作频率的技术问题。

2、为实现上述目的及其他相关目的,本申请的第一方面提供一种基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,包括:usb从机、usb降速桥、usb phy子卡及usb主机;usb从机电性连接usb降速桥,usb降速桥电性连接usb phy子卡,usb phy子卡电性连接usb主机;其中,usb降速桥设有低频pipe接口和高频pipe接口;所述低频pipe接口和与之相连的usb从机位于低频时钟域;所述高频pipe接口和与之相连的usb phy子卡、与usbphy子卡通过usb差分线相连的usb主机均位于高频时钟域;在批量输入模式下:usb主机发出原始的确认事务包以请求usb从机返回数据包;若所述原始的确认事务包中nump字段大于或者等于1,则所述usb降速桥在将所述原始的确认事务包中nump字段改为1并重新进行循环冗余校验计算后再将更新后的确认事务包转发给usb从机,并根据所述原始的确认事务包拼凑得到端点未就绪事务包发送给usb主机;usb降速桥在收到来自usb从机的响应后发送端点就绪事务包给usb主机。

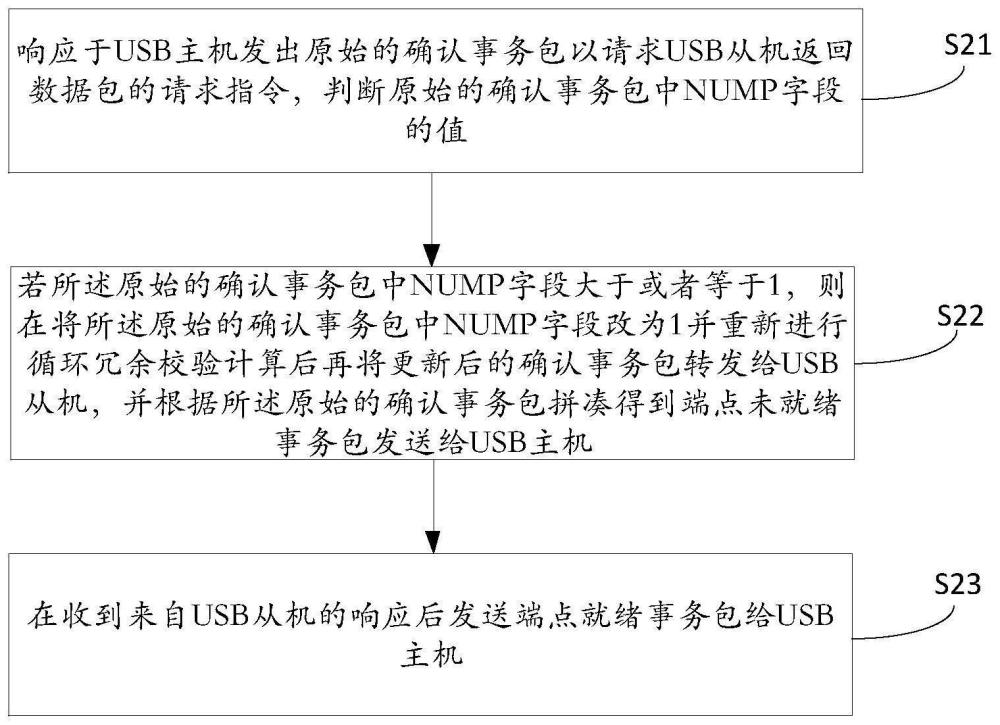

3、于本申请的第一方面的一些实施例中,所述系统还包括批量输出模式;在所述批量输出模式下:当usb主机发出数据包时,usb降速桥将数据包转发给usb从机,并根据所述数据包的数据包头字段拼凑得到一个重新发送字段被置上且mump字段为1的确认事务包,重复重新发送该数据包直至收到usb从机的反馈后将该数据包转发给usb从机。

4、于本申请的第一方面的一些实施例中,所述系统还包括控制传输模式;所述控制传输模式包括setup阶段、data阶段和status阶段;其中:在setup阶段基于所述批量输出模式进行数据传输;其中,用以表征数据包头的dph字段中的setup字段被视为1,且用以表征数据长度的data length字段被设为8;在data阶段和status阶段,若对于usb主机而言是数据输入,则基于所述批量输入模式进行数据传输;若对于usb主机而言是数据输出,则基于所述批量输出模式进行数据传输。

5、于本申请的第一方面的一些实施例中,所述系统还包括中断传输模式;所述中断传输模式包括中断输入阶段和中断输出阶段;其中,在所述中断输入阶段基于所述批量输入模式进行数据传输,在所述中断输出阶段基于所述批量输出模式进行数据传输。

6、于本申请的第一方面的一些实施例中,所述系统还包括等时传输模式;在所述等时传输模式下,当usb降速桥收到usb主机发来的数据包时将其转发给usb从机;而当usb降速桥收到来自usb从机发来的数据包时将其转发给usb主机。

7、为实现上述目的及其他相关目的,本申请的第二方面提供一种基于usb降速桥并应用于usb从机的数据包处理方法,应用于usb降速桥;所述usb降速桥电性连接usb从机和usb phy子卡,所述usb phy子卡电性连接usb主机;usb降速桥设有低频pipe接口和高频pipe接口;所述低频pipe接口和与之相连的usb从机位于低频时钟域;所述高频pipe接口和与之相连的usb phy子卡、与usb phy子卡通过usb差分线相连的usb主机均位于高频时钟域;所述方法包括:响应于usb主机发出原始的确认事务包以请求usb从机返回数据包的请求指令,判断原始的确认事务包中nump字段的值;若所述原始的确认事务包中nump字段大于或者等于1,则在将所述原始的确认事务包中nump字段改为1并重新进行循环冗余校验计算后再将更新后的确认事务包转发给usb从机,并根据所述原始的确认事务包拼凑得到端点未就绪事务包发送给usb主机;在收到来自usb从机的响应后发送端点就绪事务包给usb主机。

8、于本申请的第二方面的一些实施例中,所述方法还包括在批量输出模式下执行如下:当usb主机发出数据包时,将数据包转发给usb从机,并根据所述数据包的数据包头字段拼凑得到一个重新发送字段被置上且mump字段为1的确认事务包,重复重新发送该数据包直至收到usb从机的反馈后将该数据包转发给usb从机。

9、于本申请的第二方面的一些实施例中,所述方法还包括在控制传输模式下执行如下:在所述控制传输模式的setup阶段,基于所述批量输出模式进行数据传输;其中,用以表征数据包头的dph字段中的setup字段被视为1,且用以表征数据长度的data length字段被设为8;在所述控制传输模式的data阶段和status阶段,若对于usb主机而言是数据输入,则基于所述批量输入模式进行数据传输;若对于usb主机而言是数据输出,则基于所述批量输出模式进行数据传输。

10、为实现上述目的及其他相关目的,本申请的第三方面提供一种计算机可读存储介质,其上存储有计算机程序,所述计算机程序被处理器执行时实现所述基于usb降速桥并应用于usb从机的数据包处理方法。

11、为实现上述目的及其他相关目的,本申请的第四方面提供一种电子终端,包括:处理器及存储器;所述存储器用于存储计算机程序,所述处理器用于执行所述存储器存储的计算机程序,以使所述终端执行所述基于usb降速桥并应用于usb从机的数据包处理方法。

12、如上所述,本申请的基于usb降速桥并应用于usb从机的数据包处理系统、方法、终端及介质,具有以下有益效果:本申请可极大降低降速桥中缓存的使用,具有高兼容性,并具有错误上报机制,且在无需修改usb从机控制器参数和驱动软件的情况下依然可以正常工作。

技术特征:

1.一种基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,包括:usb从机、usb降速桥、usb phy子卡及usb主机;

2.根据权利要求1所述的基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,所述系统还包括批量输出模式;在所述批量输出模式下:当usb主机发出数据包时,usb降速桥将数据包转发给usb从机,并根据所述数据包的数据包头字段拼凑得到一个重新发送字段被置上且mump字段为1的确认事务包,重复重新发送该数据包直至收到usb从机的反馈后将该数据包转发给usb从机。

3.根据权利要求2所述的基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,所述系统还包括控制传输模式;所述控制传输模式包括setup阶段、data阶段和status阶段;其中:

4.根据权利要求2所述的基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,所述系统还包括中断传输模式;所述中断传输模式包括中断输入阶段和中断输出阶段;其中,在所述中断输入阶段基于所述批量输入模式进行数据传输,在所述中断输出阶段基于所述批量输出模式进行数据传输。

5.根据权利要求1所述的基于usb降速桥并应用于usb从机的数据包处理系统,其特征在于,所述系统还包括等时传输模式;在所述等时传输模式下,当usb降速桥收到usb主机发来的数据包时将其转发给usb从机;而当usb降速桥收到来自usb从机发来的数据包时将其转发给usb主机。

6.一种基于usb降速桥并应用于usb从机的数据包处理方法,其特征在于,应用于usb降速桥;所述usb降速桥电性连接usb从机和usb phy子卡,所述usb phy子卡电性连接usb主机;usb降速桥设有低频pipe接口和高频pipe接口;所述低频pipe接口和与之相连的usb从机位于低频时钟域;所述高频pipe接口和与之相连的usb phy子卡、与usb phy子卡通过usb差分线相连的usb主机均位于高频时钟域;所述方法包括:

7.根据权利要求6所述的基于usb降速桥并应用于usb从机的数据包处理方法,其特征在于,所述方法还包括在批量输出模式下执行如下:

8.根据权利要求7所述的基于usb降速桥并应用于usb从机的数据包处理方法,其特征在于,所述方法还包括在控制传输模式下执行如下:

9.一种计算机可读存储介质,其上存储有计算机程序,其特征在于,所述计算机程序被处理器执行时实现权利要求6至8中任一项所述基于usb降速桥并应用于usb从机的数据包处理方法。

10.一种电子终端,其特征在于,包括:处理器及存储器;

技术总结

本申请提供基于USB降速桥并应用于USB从机的数据包处理系统、方法、终端及介质,包括:USB从机、USB降速桥、USB PHY子卡及USB主机;USB从机电性连接USB降速桥,USB降速桥电性连接USB PHY子卡,USB PHY子卡电性连接USB主机;其中,USB降速桥设有低频pipe接口和高频pipe接口;所述低频pipe接口和与之相连的USB从机位于低频时钟域;所述高频pipe接口和与之相连的USB PHY子卡、与USB PHY子卡通过USB差分线相连的USB主机均位于高频时钟域。本申请可极大降低降速桥中缓存的使用,具有高兼容性,并具有错误上报机制,且在无需修改USB从机控制器参数和驱动软件的情况下依然可以正常工作。

技术研发人员:曾科南,卢笙,范凯,阴智昊,李红凯,唐仕武

受保护的技术使用者:芯启源(上海)半导体科技有限公司

技术研发日:

技术公布日:2024/1/22

- 还没有人留言评论。精彩留言会获得点赞!