用于PUCCH的覆盖增强的装置和方法与流程

本公开的实施例总体涉及通信领域,具体地,涉及用于响应于msg4物理下行链路共享信道(pdsch)、携带混合自动重传请求(harq)-确认(ack)的物理上行链路控制信道(pucch)的覆盖增强的装置和方法。

背景技术:

1、移动通信已从早期的语音系统显著发展到如今的高度复杂的集成通信平台。下一代无线通信系统、第五代(5g)或新无线电(nr)将通过各种终端和应用随时随地提供信息访问和数据共享。nr有望成为统一的网络/系统,旨在满足截然不同且有时相互冲突的性能维度和服务。这种不同的多维需求是由不同的服务和应用驱动的。通常,nr可以基于第三代合作伙伴计划(3gpp)长期演进(lte)-高级和其他潜在的新无线电接入技术(rat)进行演进,从而通过更好、简单和无缝的无线连接解决方案来丰富人们的生活。nr可以启用通过无线连接的所有事物,并提供快速、丰富的内容和服务。

技术实现思路

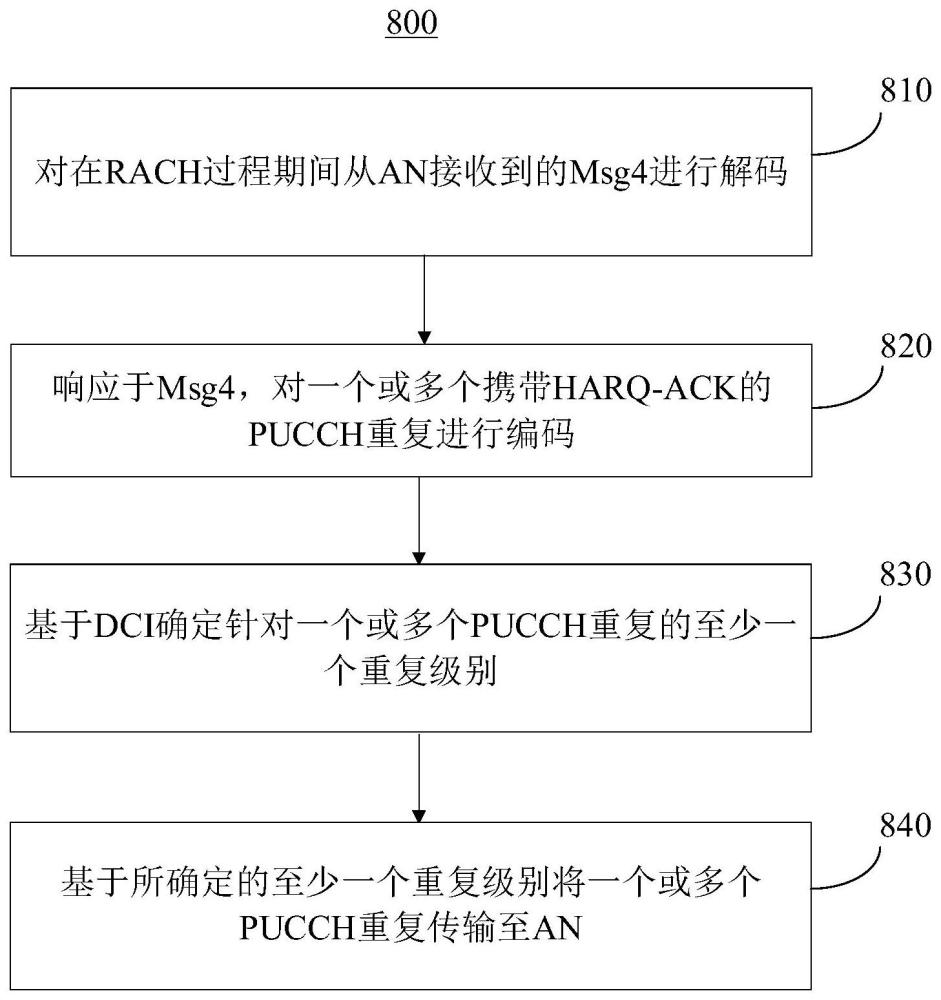

1、本公开的一方面提供了一种装置,包括:接口电路;和处理器电路,所述处理器电路与所述接口电路耦合,其中,所述处理器电路用于:对经由所述接口电路、在随机接入信道(rach)过程期间从接入节点(an)接收到的msg4进行解码;响应于所述msg4,对一个或多个携带混合自动重传请求(harq)-确认(ack)的物理上行链路控制信道(pucch)重复进行编码;基于下行链路控制信息(dci)来确定针对所述一个或多个pucch重复的至少一个重复级别;以及使得基于所确定的至少一个重复级别将所述一个或多个pucch重复传输至所述an。

2、本公开的一方面提供了一种装置,包括:接口电路;和处理器电路,所述处理器电路与所述接口电路耦合,其中,所述处理器电路用于:针对响应于随机接入信道(rach)过程的msg4的、携带混合自动重传请求(harq)-确认(ack)的物理上行链路控制信道(pucch)重复,配置多个重复级别;以及经由下行链路控制信息(dci)来通过所述接口电路向用户设备(ue)指示所述多个重复级别中的一个重复级别。

技术特征:

1.一种装置,包括:

2.如权利要求1所述的装置,其中,所述dci包括dci格式1_0,所述dci格式1_0具有由临时小区-无线电网络临时标识符(tc-rnti)加扰的循环冗余校验(crc)。

3.如权利要求1所述的装置,其中,所述至少一个重复级别是由下行链路分配索引字段表明的。

4.如权利要求1所述的装置,其中,所述至少一个重复级别是由如下项中的至少一项表明的:

5.如权利要求1所述的装置,其中,针对msg3物理上行链路共享信道(pusch)重复的每个重复级别与针对所述pucch重复的一个或多个重复级别相关联。

6.如权利要求1所述的装置,其中,所述处理器电路还用于:

7.如权利要求6所述的装置,其中,频谱是非成对的,并且其中,所述处理器电路还用于确定所述一个或多个可用时隙与如下项不重叠:

8.如权利要求6所述的装置,其中,频谱是成对的或者包括补充上行链路频带,所述一个或多个可用时隙的数量是n个可用时隙,并且其中,所述处理器电路还用于:

9.如权利要求6所述的装置,其中,所述一个或多个可用时隙是连续的或非连续的。

10.如权利要求1所述的装置,其中,所述处理器电路还用于:

11.如权利要求10所述的装置,其中,用于所述一个或多个pucch重复的空间域滤波器与用于由所述rar ul准予所调度的所述pusch传输的空间域滤波器相同。

12.如权利要求1所述的装置,其中,所述处理器电路还用于:

13.如权利要求12所述的装置,其中,所述配置是经由系统信息块1(sib1)、新无线电(nr)剩余最小系统信息(rmsi)、nr其他系统信息(osi)、或专用无线电资源控制(rrc)信令携带的。

14.如权利要求12所述的装置,其中,所述跳频模式包括时隙内跳频模式和/或时隙间跳频模式。

15.如权利要求14所述的装置,其中,所述时隙内跳频模式和时隙间跳频模式不被同时启用。

16.如权利要求14所述的装置,其中,所述跳频模式包括时隙间跳频模式,并且其中,所述处理器电路还用于基于如下项来执行跳频:

17.如权利要求1至16中任一项所述的装置,其中,所述装置适用于用户设备(ue)。

18.一种装置,包括:

19.如权利要求18所述的装置,其中,所述dci包括dci格式1_0,所述dci格式1_0具有由临时小区-无线电网络临时标识符(tc-rnti)加扰的循环冗余校验(crc)。

20.如权利要求18所述的装置,其中,所述多个重复级别是由下行链路分配索引字段指示的。

技术总结

本公开提供了用于PUCCH的覆盖增强的装置和方法。一种装置,包括:接口电路;和处理器电路,所述处理器电路与所述接口电路耦合,其中,所述处理器电路用于:对经由所述接口电路、在RACH过程期间从AN接收到的Msg4进行解码;响应于所述Msg4,对一个或多个携带HARQ‑ACK的PUCCH重复进行编码;基于DCI来确定针对所述一个或多个PUCCH重复的至少一个重复级别;以及使得基于所确定的至少一个重复级别将所述一个或多个PUCCH重复传输至所述AN。还可以公开并要求保护其他实施例。

技术研发人员:熊岗,维克多·谢尔盖耶夫

受保护的技术使用者:英特尔公司

技术研发日:

技术公布日:2024/4/7

- 还没有人留言评论。精彩留言会获得点赞!