一种全数字并行基带通信编码方法和装置与流程

本申请涉及通信编码,具体涉及一种全数字并行基带通信编码方法和装置。

背景技术:

1、在导弹/火箭的未来发展中,无线测发控体系将逐渐占据主导地位,由于无线测发控系统设计的传输内容涉及弹上重要的控制指令,例如解保、点火等,同时需要与地面进行状态监测数据交互,其数据地稳定可靠传输会影响发射前的状态判断。如何确保稳定可靠传输数据已成为了目前通信编码技术中亟需解决的技术问题。

技术实现思路

1、为了解决上述技术问题,本发明提出了一种可变速率高码率全数字并行基带通信编码方法和装置,旨在为无线测发控系统提供一种高速、可靠的无线数据传输方式,实现无线测发控数据的压缩、帧格式编排、编码、调制、功率放大等操作,实现弹上地面的高速可靠数据传输。

2、本发明所采用的技术方案如下:

3、一种全数字并行基带通信编码方法,该方法包括如下步骤:

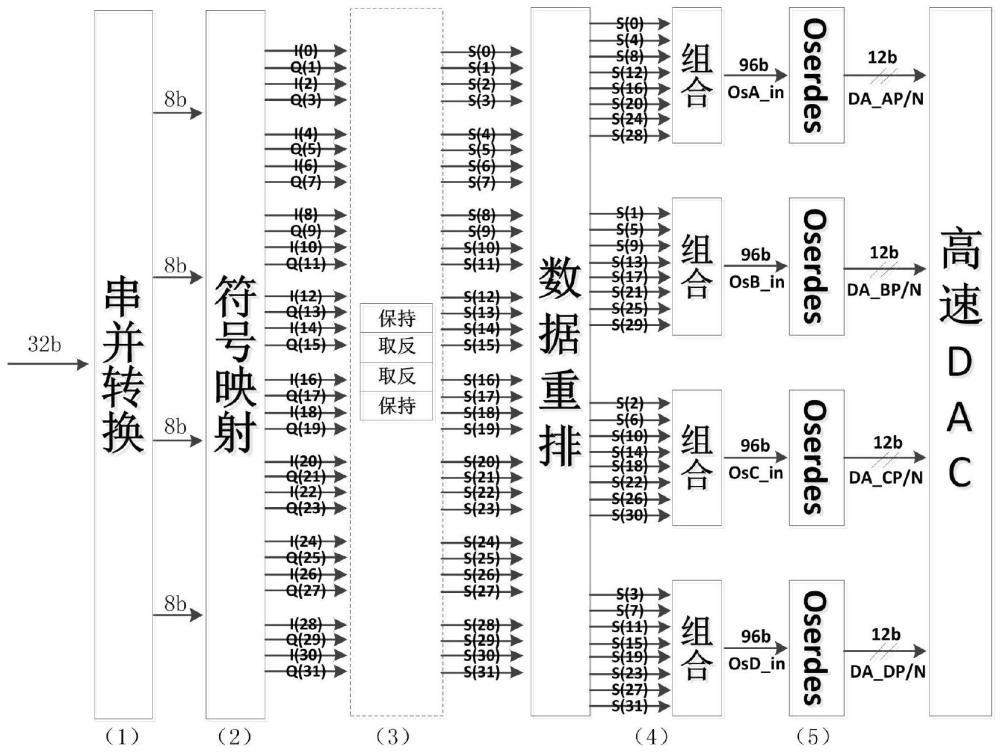

4、步骤1、串并转换模块对接收到的比特流进行串并转换以获得并行数据流,并将所述并行数据流输出至符号映射模块;

5、步骤2、所述符号映射模块采用16qam映射方式对所述并行数据流进行符号映射处理,以得到i、q各8路并行符号数据,并输出至所述数据整理模块;

6、步骤3、所述数据整理模块对所述i、q各8路并行符号数据进行数字正交上变频处理以对i、q依次进行保持、取反、取反、保持操作,并得到32路并行的基带信号s,将所述基带信号s以12位寄存器形式一次性操作,并将整理后的32路数据输出至所述数据重排模块;

7、步骤4、所述数据重排模块将所述整理后的32路数据按abcd的顺序重排,组合成4路96bit数据并输出至所述并串转换模块;

8、步骤5、所述并串转换模块将所述4路96bit数据分别送入4个并串转换器,得到4路差分并行输出数据,并输出至高速dac以转换成模拟信号,其中,所述并串转换器的转换率为8:1。

9、进一步的,在步骤1中,输入的比特流以4字节的方式按照时钟节拍5gbps输入,经过1:4串并转换,变成4路1字节的并行数据流,该并行数据流的速率为1.25gbps。

10、进一步的,在步骤2中,所采用的16qam映射方式如下表所示:

11、

12、所采用的16qam映射方式的解映射的硬判决通过如下公式来实现:

13、

14、其中,每路8字节对应两组i、q,其中b0b1对应i路幅值,b2b3对应q路幅值。

15、进一步的,所述对所述并行数据流进行符号映射处理,还包括:

16、对并行数据流进行重采样,以得到每路8字节的i、q各8路并行符号数据。

17、进一步的,在步骤3中,所述数字正交上变频处理采用如下公式来实现:

18、s(n)=i(n)cos(2πfcn/fs)-q(n)sin(2πfcn/fs)

19、其中,中频fc选择为fc=fs/4。

20、一种全数字并行基带通信编码装置,该编码装置包括串并转换模块、符号映射模块、数据整理模块、数据重排模块以及并串转换模块,所述串并转换模块,用于对接收到的比特流进行串并转换以获得并行数据流,并将所述并行数据流输出至符号映射模块;

21、所述符号映射模块,用于采用16qam映射方式对所述并行数据流进行符号映射处理,以得到i、q各8路并行符号数据,并输出至所述数据整理模块;

22、所述数据整理模块,用于对所述i、q各8路并行符号数据进行数字正交上变频处理以对i、q依次进行保持、取反、取反、保持操作,并得到32路并行的基带信号s,将所述基带信号s以12位寄存器形式一次性操作,并将整理后的32路数据输出至所述数据重排模块;

23、所述数据重排模块,用于将所述整理后的32路数据按abcd的顺序重排,组合成4路96bit数据并输出至所述并串转换模块;

24、所述并串转换模块,用于将所述4路96bit数据分别送入4个并串转换器,得到4路差分并行输出数据,并输出至高速dac以转换成模拟信号,其中,所述并串转换器的转换率为8:1。

25、进一步的,在所述串并转换模块中,输入的比特流以4字节的方式按照时钟节拍5gbps输入,经过1:4串并转换,变成4路1字节的并行数据流,该并行数据流的速率为1.25gbps。

26、进一步的,在所述符号映射模块中,所采用的16qam映射方式如下表所示:

27、

28、所采用的16qam映射方式的解映射的硬判决通过如下公式来实现:

29、

30、其中,每路8字节对应两组i、q,其中b0b1对应i路幅值,b2b3对应q路幅值。

31、进一步的,在所述数据整理模块中,所述对所述并行数据流进行符号映射处理,还包括:

32、对并行数据流进行重采样,以得到每路8字节的i、q各8路并行符号数据。

33、进一步的,在所述数据整理模块中,所述数字正交上变频处理采用如下公式来实现:

34、s(n)=i(n)cos(2πfcn/fs)-q(n)sin(2πfcn/fs)

35、其中,中频fc选择为fc=fs/4。

36、通过本申请的技术方案,可以获得如下技术效果:

37、1)本发明通过对数据进行重采样,可不生成本振信号,直接通过对i、q两路基带信号进行奇偶交替抽取和取反,就能得到中频信号,简化调制算法;

38、2)本发明采用串并转换,能够实现码率5gbps,中心频率1.25ghz的告诉调制方法,且码率在1mbps可变,大大提升了编码方法的灵活性与拓展性。

技术特征:

1.一种全数字并行基带通信编码方法,其特征在于,该方法包括如下步骤:

2.根据权利要求1所述的基带通信编码方法,其特征在于,在步骤1中,输入的比特流以4字节的方式按照时钟节拍5gbps输入,经过1:4串并转换,变成4路1字节的并行数据流,该并行数据流的速率为1.25gbps。

3.根据权利要求1所述的基带通信编码方法,其特征在于,在步骤2中,所采用的16qam映射方式如下表所示:

4.根据权利要求1所述的基带通信编码方法,其特征在于,所述对所述并行数据流进行符号映射处理,还包括:

5.根据权利要求1所述的基带通信编码方法,其特征在于,在步骤3中,所述数字正交上变频处理采用如下公式来实现:

6.一种全数字并行基带通信编码装置,该编码装置包括串并转换模块、符号映射模块、数据整理模块、数据重排模块以及并串转换模块,其特征在于,

7.根据权利要求6所述的编码装置,其特征在于,在所述串并转换模块中,输入的比特流以4字节的方式按照时钟节拍5gbps输入,经过1:4串并转换,变成4路1字节的并行数据流,该并行数据流的速率为1.25gbps。

8.根据权利要求1所述的编码装置,其特征在于,在所述符号映射模块中,所采用的16qam映射方式如下表所示:

9.根据权利要求6所述的编码装置,其特征在于,在所述数据整理模块中,所述对所述并行数据流进行符号映射处理,还包括:

10.根据权利要求6所述的编码装置,其特征在于,在所述数据整理模块中,所述数字正交上变频处理采用如下公式来实现:

技术总结

本发明提供了一种可变速率高码率全数字并行基带通信编码方法和装置。该方法基于时域并行调制结构,设计了高速并行可变速率调制架构,包含串并转换、符号映射、取反、数据重排、并串转换等过程。本发明旨在为无线测发控系统提供一种高速、可靠的无线数据传输方式,实现无线测发控数据的压缩、帧格式编排、编码、调制、功率放大等操作,实现弹上地面的高速可靠数据传输。

技术研发人员:王亨,徐春铃,潘明健,王琳,张晶莹,孙精华,付秋军,郭心怡,潘宇,崔同锴,蒋永瑞,梁宇,邱长泉,薛志超,王洪武,谢飞强

受保护的技术使用者:北京临近空间飞行器系统工程研究所

技术研发日:

技术公布日:2024/5/6

- 还没有人留言评论。精彩留言会获得点赞!