一种基于FPGA的高分辨率彩色图像叠加系统及方法与流程

本发明属于图像处理,尤其涉及一种基于fpga的高分辨率彩色图像叠加系统及方法。

背景技术:

1、由于航空航天领域的部分摄像装置需要完成跟踪的行为,为了增加视觉分析的便利性,这就要求后端软件在摄像装置捕获的图像上叠加图形或字符信息。现在大都采用dsp+fpga+emif的方式实现,dsp通过emif(external memory interface)总线下发叠加指令和叠加内容,fpga实现叠加。另有一种快速叠加方法,将要叠加的图形事先存储在fpga内部rom中,通过dsp给fpga发送叠加控制指令,由fpga实现叠加显示。

2、使用emif总线来传输叠加信息的方式,由于emif(external memory interface)总线通信的数据速率不高,从而限制了叠加信息的实时性,也限制了叠加信息的大小。使用内部rom的这种方法解决了实时性和丰富性要求,但灵活性差,只能叠加事先写入fpga内部rom中的图形,如果应用场景对叠加图形的要求不一致,需要修改fpga内部rom,这种方法操作复杂,应用对象单一,无法做到通用性。

技术实现思路

1、本发明的目的是提出一种兼具实时性、灵活性和通用性的字符叠加和图形叠加系统及方法。

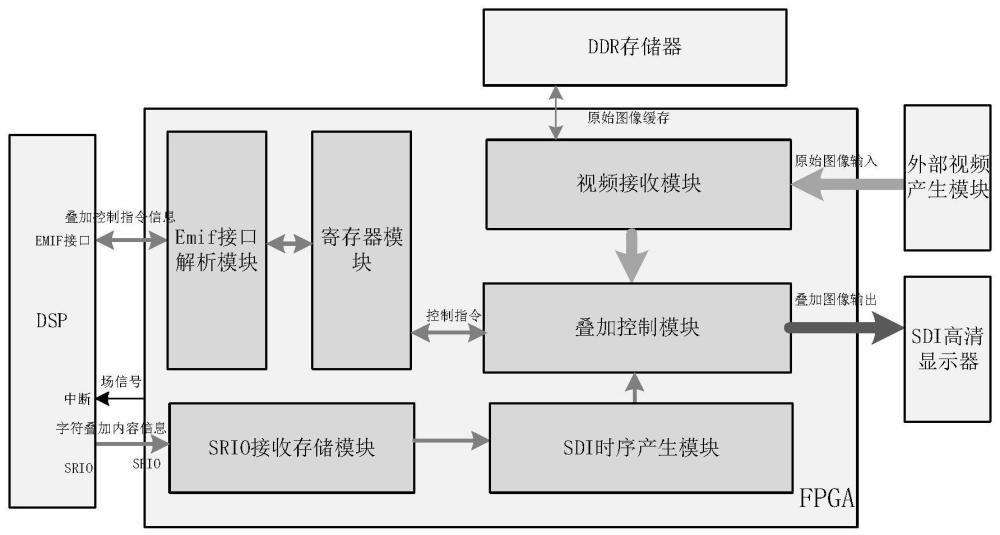

2、本发明提出一种基于fpga的高分辨率彩色图像叠加系统,包括dsp、fpga、外部视频产生模块、sdi高清显示器和ddr存储器,其中,dsp用于产生每帧图像的叠加控制指令信息和字符叠加内容信息;fpga用于接收视频数据并根据dsp产生的叠加控制指令信息和字符叠加内容信息,在原始图像上实现图形叠加和字符叠加;外部视频产生模块用于产生原始图像;sdi高清显示器用于将叠加后的图像进行显示;ddr存储器用于将fpga接收的图像进行帧缓存。

3、进一步地,fpga还包含emif接口解析模块、寄存器模块、视频接收模块、srio接收存储模块、sdi时序产生模块和叠加控制模块,其中,

4、视频接收模块用于每帧视频图像的接收,并将接收到的图像数据帧缓存到ddr存储器中;

5、sdi时序产生模块用于产生能够驱动sdi高清显示器的接口时序和数据,并产生行、场同步信号,并将场同步信号作为中断送给dsp,要求dsp在场信号的上升沿生成叠加控制指令信息和字符叠加内容信息,并要求dsp在场信号的下降沿通过emif接口将叠加控制指令信息发送给fpga,并要求dsp在场信号的下降沿通过srio接口将字符叠加内容信息发送给fpga;

6、fpga通过srio接收存储模块接收dsp的字符叠加内容信息;

7、fpga通过emif接口解析模块接收dsp叠加控制指令信息;

8、寄存器模块用来寄存dsp每帧下发的叠加控制指令信息;

9、叠加控制模块用于实现图形叠加和字符叠加,并输出到sdi高清显示器。

10、本发明还提出一种基于fpga的高分辨率彩色图像叠加方法,包括以下步骤:

11、步骤一、fpga通过视频接收模块获取原始图像数据;

12、步骤二、fpga中的sdi时序产生模块产生sdi显示时序;

13、步骤三、fpga获取叠加控制指令信息和字符叠加内容信息;

14、步骤四、根据获取的叠加控制指令信息将获取的原始图像数据、获取的字符叠加内容信息与sdi显示时序的相关信号做叠加处理,得到叠加图像输出信号。

15、进一步地,步骤三包括:

16、步骤1)、叠加控制指令信息由dsp发送给fpga;

17、步骤2)、字符叠加内容信息由dsp发送给fpga。

18、进一步地,在步骤1)中:

19、dsp接收来自fpga的中断信号,并在中断信号的上升沿产生下一帧的叠加控制指令信息,在中断信号的下降沿通过emif接口将叠加控制指令信息发送给fpga。

20、进一步地,所述中断信号为场同步信号,产生自sdi时序产生模块。

21、进一步地,所述叠加控制指令信息包含两种类型的控制信息,一种是针对图形叠加,一种是针对字符叠加,针对图形叠加的控制信息有:每种图形的使能、半长、半宽、线宽、空白区半长和中心点位置。

22、进一步地,在步骤2)中:

23、dsp接收来自fpga的中断信号后,在中断信号的上升沿生成下一帧的字符叠加内容信息,在中断信号的下降沿通过srio接口将字符叠加内容信息发送给fpga。

24、进一步地,字符叠加内容信息为全图叠加使能块,通过构造叠加基本单元来构建任意全图叠加使能块,dsp在8bit*8bit的叠加基本单元中创造字符,并将基本单元拼接成全图叠加使能块,该全图叠加使能块即为字符叠加内容信息。

25、进一步地,步骤四具体为:

26、fpga中的叠加控制模块以像素时钟为基准时钟,分别产生行计数计数器和列计数计数器,列计数计数器在行同步信号为0时清零,在行同步信号为1时累加;行计数计数器在场同步信号为0时清零,在每个行同步的下降沿累加,在图像显示区域,根据当前像素时钟周期下判断行计数计数器、列计数计数器的值即可得知前像素点在显示器上的位置;

27、fpga根据行计数计数器和列计数计数器的值判断当前像素点的位置,如果图形叠加使能有效,fpga输出图形叠加对应的yuv数值;如果字符叠加使能有效,fpga输出字符叠加对应的yuv值,否则,输出对应位置的原始图像数据。

28、与现有技术相比,本发明的字符叠加更具灵活性(dsp可任意构造叠加基本单元并拼接全图叠加使能块),叠加信息传输更快(采用srio接口,rapid io),传输的数据量更小(1bit叠加使能),继而可支持的分辨率更高。基于系统的快速性该发明也能降低dsp对叠加操作的处理时间们可以允许更多的时间放在更复杂的其他数据处理上。

29、本发明还具备fpga图形叠加功能,dsp通过配置简单的控制寄存器fpga即可实现图形叠加的功能,将图像叠加功能设计在fpga内,可降低dsp操作的复杂性,减少对dsp系统时间的占用,同时,还能实现任意位置任意大小的图形叠加显示。

技术特征:

1.一种基于fpga的高分辨率彩色图像叠加系统,其特征在于:包括dsp、fpga、外部视频产生模块、sdi高清显示器和ddr存储器,其中,dsp用于产生每帧图像的叠加控制指令信息和字符叠加内容信息;fpga用于接收视频数据并根据dsp产生的叠加控制指令信息和字符叠加内容信息,在原始图像上实现图形叠加和字符叠加;外部视频产生模块用于产生原始图像;sdi高清显示器用于将叠加后的图像进行显示;ddr存储器用于将fpga接收的图像进行帧缓存。

2.根据权利要求1所述的一种基于fpga的高分辨率彩色图像叠加系统,其特征在于:fpga还包含emif接口解析模块、寄存器模块、视频接收模块、srio接收存储模块、sdi时序产生模块和叠加控制模块,其中,

3.一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,包括以下步骤:

4.如权利要求3所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,步骤三包括:

5.如权利要求4所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,在步骤1)中:

6.如权利要求5所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,所述中断信号为场同步信号,产生自sdi时序产生模块。

7.如权利要求3所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,所述叠加控制指令信息包含两种类型的控制信息,一种是针对图形叠加,一种是针对字符叠加,针对图形叠加的控制信息有:每种图形的使能、半长、半宽、线宽、空白区半长和中心点位置。

8.如权利要求5所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,在步骤2)中:

9.如权利要求8所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于:字符叠加内容信息为全图叠加使能块,通过构造叠加基本单元来构建任意全图叠加使能块,dsp在8bit*8bit的叠加基本单元中创造字符,并将基本单元拼接成全图叠加使能块,该全图叠加使能块即为字符叠加内容信息。

10.如权利要求3所述的一种基于fpga的高分辨率彩色图像叠加方法,其特征在于,步骤四具体为:

技术总结

本发明属于图像处理技术领域,公开了一种基于FPGA的高分辨率彩色图像叠加系统及方法,该系统包括DSP、FPGA、外部视频产生模块、SDI高清显示器和DDR存储器,其中,外部视频产生模块产生原始图像数据;DDR存储器用于将FPGA接收的图像进行帧缓存;DSP用于产生每帧图像的叠加控制指令信息和叠加控制数据;FPGA用于视频接收及根据DSP产生的叠加控制指令和叠加控制数据实现叠加;SDI高清显示器用于将叠加后的图像进行显示。本发明的字符叠加更具灵活性,叠加信息传输更快,传输的数据量更小,继而可支持的分辨率更高。本发明还具备FPGA图形叠加功能,降低DSP操作的复杂性,减少对DSP系统时间的占用,同时,还能实现任意位置任意大小的图形叠加显示。

技术研发人员:葛瑜,樊周华,张浩,聂震

受保护的技术使用者:北京计算机技术及应用研究所

技术研发日:

技术公布日:2024/3/17

- 还没有人留言评论。精彩留言会获得点赞!