一种基于OCML的数据链系统及方法与流程

本发明属于终端领域,尤其涉及一种基于ocml的数据链系统及方法。

背景技术:

1、目前对数据链通信系统的研究中使用的扰码序列大多为伪随机序列(pn序列),但pn序列相关性较差且序列复杂度低,安全性不高,不能满足模型的设计要求,而本发明选用的ocml序列具有良好的正交性和自相关性、不变分布性、序列数量等多个优点,较于pn序列能使系统具有更好的性能。同时在数据链模型中引入跳频技术,利用跳频使载波不断跳变,能够有效的对抗外界干扰。

2、为了解决上述问题,本发明提出一种基于ocml的数据链系统及方法。

技术实现思路

1、鉴于以上现有技术的不足,发明的目的在于提供一种基于ocml的数据链系统,以解决背景技术问题。

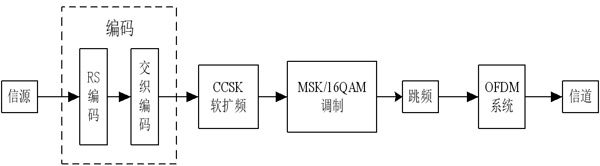

2、本发明的第一方面,提出了一种基于ocml的数据链系统,所述系统包括:

3、编码模块:用于对输入的数据进行编码处理;

4、软扩频模块:用于编码模块处理后的数据进行扩频;

5、msk调制模块:用于将扩频后的数据进行调制,将信号搬移到适合信道传播的载波频率上;

6、跳频模块:用于对信号扩展频谱;

7、ofdm调制模块,用于将扩展频谱后的数据流转换为适合信道传输的信号形式进行传输。

8、进一步的,所述编码模块包括rs编码和交织编码,所述rs编码采用rs (15,11)的编码方式,所述交织编码将码元序列经过交织处理,将连续的错误码元分散。

9、进一步的,所述软扩频模块采用ocml序列作为基序列进行ccsk扩频编码。

10、进一步的,所述msk调制模块采用msk调制方式,将信号搬移到适合信道传播的载波频率上。

11、进一步的,所述跳频模块利用伪随机二进制代码控制载波频率振荡器的输出频率,即信号经过msk调制模块数字调制之后,再将调制后的信号与跳频频率合成器相乘得到跳频调制后的信号,跳频部分使用的是伪随机二进制代码,来控制载波频率振荡器的输出频率。

12、进一步的,所述ofdm调制模块中的串并转换将高速串行的数据转变为低速并行的数据流进行传输,并将每个子载波上传输的信号速率降低为原来的1/n。

13、本发明的第二方面,提供一种基于ocml的数据链系统的方法,包括:

14、步骤s1:信号源生成伯努利信号 ;

15、步骤s2,信号经过编码模块,rs编码与交织编码双重编码,生成监督码元用于纠正错误码;

16、步骤s3,经过编码后信号传入ccsk软扩频模块,以ocml混沌序列作为基序列进行数据加密并提升信号传输速率 ;

17、步骤s4,加密后的信号经过调制模块,将信号搬移到适合信道传播的载波频率上,降低带宽受限对信号传输速率的影响;

18、步骤s5,信号进入跳频模块对信号进行扩展频谱 ;

19、步骤s6,信号最后经过ofdm模块;通过串并转换子模块将高速串行的数据转变为低速并行的数据流进行传输。

20、本发明有益效果如下:

21、采用rs编码和交织编码结合的方法,更好地纠正了信息传输过程中出现的随机差错和突发差错,从而大大降低了信号在传输过程中出现错误码元的概率;信号经过编码模块后进入ccsk软扩频模块,将较短的序列映射为更长的序列,并且加大了映射码的随机性,大大提高了信号的保密性;通过ofdm模块降低了各子载波上信号的传输速率,从而保证了数据链中高速率、大数据量的数据传输要求。

技术特征:

1.一种基于ocml的数据链系统,其特征在于,所述系统包括:

2.根据权利要求1所述的一种基于ocml的数据链系统,其特征在于,所述编码模块包括rs编码和交织编码,所述rs编码采用rs(15,11)的编码方式。

3.根据权利要求2所述的一种基于ocml的数据链系统,其特征在于,所述交织编码将码元序列经过交织处理,将连续的错误码元分散。

4.根据权利要求1所述的一种基于ocml的数据链系统,其特征在于,所述软扩频模块采用ocml序列作为基序列进行ccsk扩频编码。

5.根据权利要求1所述的一种基于ocml的数据链系统,其特征在于,所述msk调制模块采用msk调制方式。

6.根据权利要求5所述的一种基于ocml的数据链系统,其特征在于,所述msk调制方式将信号搬移到适合信道传播的载波频率上。

7.根据权利要求1所述的一种基于ocml的数据链系统,其特征在于,所述跳频模块利用伪随机二进制代码控制载波频率振荡器的输出频率,即信号经过msk调制模块数字调制之后,再将调制后的信号与跳频频率合成器相乘得到跳频调制后的信号,跳频部分使用的是伪随机二进制代码,来控制载波频率振荡器的输出频率。

8.根据权利要求1所述的一种基于ocml的数据链系统,其特征在于,所述ofdm调制模块中的串并转换将高速串行的数据转变为低速并行的数据流进行传输,并将每个子载波上传输的信号速率降低为原来的1/n。

9.一种基于ocml的数据链系统的方法,其特征在于,所述方法用于执行权利要求1-6任一项所述的系统,包括:

10.根据权利要求9所述的一种基于ocml的数据链系统的方法,其特征在于,所述步骤s6通过串并转换子模块将高速串行的数据转变为低速并行的数据流进行传输。

技术总结

本发明涉及一种基于OCML的数据链系统及方法,终端领域,包括:编码模块:用于对输入的数据进行编码处理;软扩频模块:用于编码模块处理后的数据进行扩频;MSK调制模块:用于将扩频后的数据进行调制,将信号搬移到适合信道传播的载波频率上;跳频模块:用于对信号扩展频谱;OFDM调制模块,用于将扩展频谱后的数据流转换为适合信道传输的信号形式进行传输。本发明发送端信源发送伯努利信号,该信号首先经过编码模块,包括RS编码和交织编码。采用RS编码和交织编码结合的方法,更好地纠正了信息传输过程中出现的随机差错和突发差错,从而大大降低了信号在传输过程中出现错误码元的概率。

技术研发人员:翟鄀

受保护的技术使用者:天翼云科技有限公司

技术研发日:

技术公布日:2024/8/26

- 还没有人留言评论。精彩留言会获得点赞!