一种加密模块、加扰时间戳的生成方法及超带宽通信系统与流程

本发明涉及超带宽通信,特别涉及一种加密模块、加扰时间戳的生成方法及超带宽通信系统。

背景技术:

1、超宽带(uwb,ultra-wideband)是一种短距离无线通信技术,其具有高数据速率、低功耗和高定位精度的特点。随着无线通信技术的飞速发展,uwb技术逐渐在物联网、智能家居、工业自动化和医疗等领域得到了广泛应用。

2、加扰时间戳序列(scrambled timestamp sequence,sts)是由802.15.4z引入的一项关键技术。其通过使用128位密钥长度的对称加密算法aes-128(advanced encryptionstandard)及确定性随机比特生成器(deterministic random bit generator,drbg)生成。sts的引入提升了uwb通讯中的安全性和时间同步精度。图1示出sts在uwb包的位置。在802.15.4z中,uwb系统生成sts码字的流程如图2所示,stsvcounter与32位计数器组成aes明文的低32位,stsvupper96为aes明文的高96位,所述aes明文与128位的sts key进行aes-128运算得到128位伪随机数用于传输/接收流程。所述128位伪随机数也可称为aec-128码字。通常uwb的一轮传输/接收中会连续生成多轮sts码字,多轮生成过程中stsvupper96、stsvcounter及sts key均不会改变,且在进行下一轮码字生成之前所述32位计数器会进1,从而达到确定性随机的目的。uwb系统对sts的处理流程如图3所示,所述128位伪随机数经过扩展增量函数处理,生成用于sts的扩展码片(512chips),作为基础的sts数据。sts段由多个512chips单元构成,且sts段之间通过“gap”分隔。gap表示无信号传输的时间间隔,旨在避免符号间干扰,并增加信号随机性。由于在802.15.4z规定下uwb极限脉冲重复频率(prf)高达499.2mhz,这会使uwb的发射层整体时钟频率较高,对于低成本旧制程的设计稳定性会有较大挑战。而sts部分每128位传输就要进行一次aes运算,会带来较大的瞬时功耗,使得整系统功耗呈周期性变化,且有明显峰值。这种功耗变化会影响系统稳定性和传输安全性,同时,周期性变化的峰值功耗容易被旁路攻击所利用。

技术实现思路

1、针对现有技术中的部分或全部问题,本发明第一方面提供一种加密模块,包括:

2、计算子模块,其用于基于aes明文及密钥生成aes码字;

3、计数子模块,其用于确定aes码字的生成次数;

4、控制子模块,其用于控制所述计算子模块,以控制aes码字生成时间;以及

5、同步子模块,其用于所述加密模块与其他模块的时钟同步。

6、进一步地,所述加密模块的时钟频率低于500mhz。

7、进一步地,控制aes码字生成时间包括:

8、检测到sts段间隔后,等待随机时长,控制所述计算子模块开始生成aes码字。

9、进一步地,所述控制子模块还用于:

10、确定上一轮码字输出剩余时长是否大于生成一轮aes码字所需时长,若大于,则控制所述计算子模块生成下一轮aes码字或伪装aes码字。

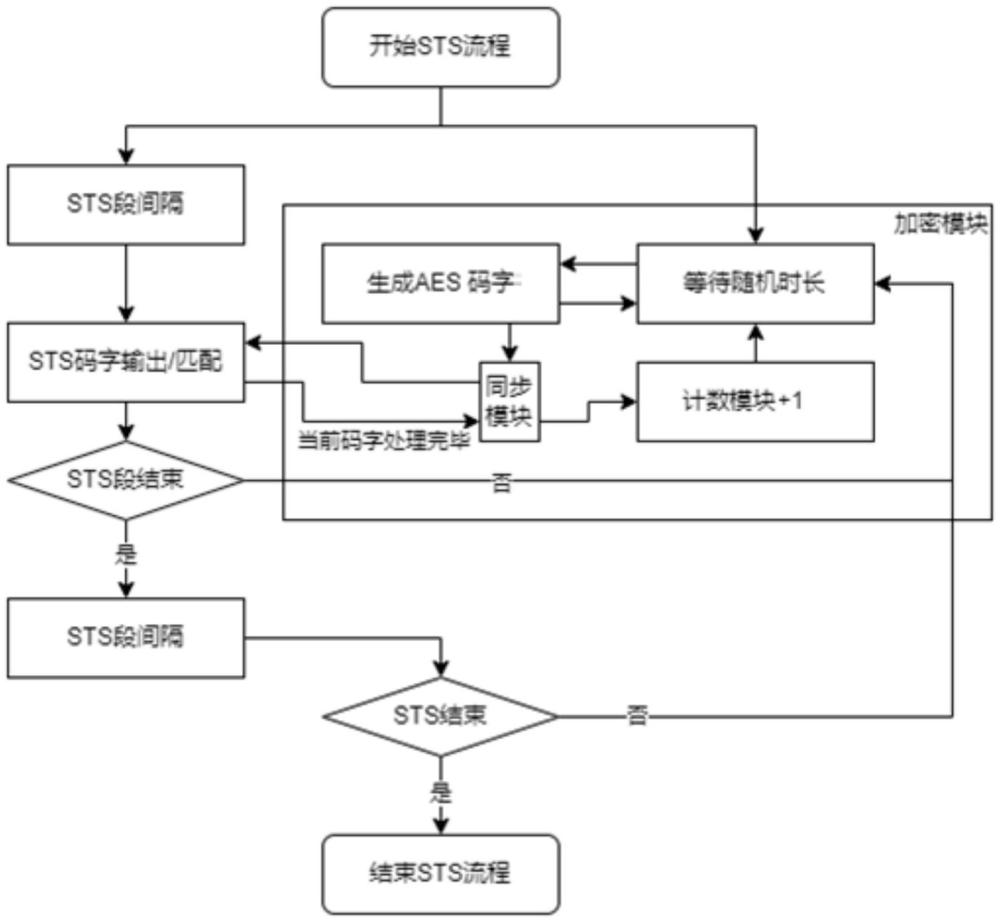

11、基于如前所述的加密模块,本发明第二方面提供一种加扰时间戳的生成方法,包括:

12、生成sts间隔后,等待随机时长,通过加密模块生成一轮aes码字;

13、通过sts码字输出/匹配模块对所述aes码字进行处理,以形成sts码片;

14、等待随机时长,再次生成aes码字,并形成sts码片,重复该步骤多次,以得到多个sts码片;以及

15、将所述多个sts码片组成sts段,并插入sts间隔,形成加扰时间戳。

16、进一步地,所述生成方法还包括:

17、形成sts码片期间,进行随机次数的伪装aes码字生成。

18、进一步地,所述生成方法还包括:

19、通过同步子模块将所述aes码字发送至所述sts码字输出/匹配模块。

20、进一步地,所述生成方法还包括:

21、生成aes码字前,判断剩余时长是否满足生成一轮aes码字所需时长。

22、基于如前所述的生成方法,本发明第三方面提供一种超带宽通信系统,其采用如前所述的加扰时间戳的生成方法。

23、本发明提供的一种加密模块、加扰时间戳的生成方法及超带宽通信系统,通过增加随机等待时长使得加密过程失去周期性,不再与码字周期相匹配,配合伪装的码字可以混淆整个sts流程的功耗变化。同时由于单次加密周期的延长,aes-128加密模块也不会有明显的功耗峰值。这些改动显著提升了uwb的sts系统对于旁路攻击的抗性,以及整个系统的稳定性。

技术特征:

1.一种加密模块,其特征在于,包括:

2.如权利要求1所述的加密模块,其特征在于,所述加密模块的时钟频率低于500mhz。

3.如权利要求1所述的加密模块,其特征在于,所述加密模块的时钟频率低于100mhz。

4.如权利要求1所述的加密模块,其特征在于,控制aes码字生成时间包括:

5.如权利要求1所述的加密模块,其特征在于,所述控制子模块还被配置为:

6.一种加扰时间戳的生成方法,其特征在于,包括步骤:

7.如权利要求6所述的生成方法,其特征在于,还包括步骤:

8.如权利要求6所述的生成方法,其特征在于,还包括步骤:

9.如权利要求7所述的生成方法,其特征在于,还包括步骤:

10.一种超带宽通信系统,其特征在于,采用如权利要求6至9任一所述的加扰时间戳的生成方法生成加扰时间戳。

技术总结

本发明公开一种加密模块,其包括计算子模块、计数子模块、控制子模块以及同步子模块,其中计算子模块用于基于AES明文及密钥生成AES码字,计数子模块用于确定AES码字的生成次数,控制子模块用于控制所述计算子模块,以控制AES码字生成时间,以及同步子模块执行所述加密模块与其他模块的时钟同步。通过增加随机等待时长使得加密过程失去周期性,不再与码字周期相匹配,配合伪装的码字可以混淆整个STS流程的功耗变化,以更好地抗击旁路攻击。

技术研发人员:王超琪,陈言言,陈玉祥,沈智浩

受保护的技术使用者:青芯半导体科技(上海)有限公司

技术研发日:

技术公布日:2025/2/10

- 还没有人留言评论。精彩留言会获得点赞!