一种针对CKKS同态加密算法中密钥切换算法的硬件加速器

本发明属于隐私计算和全同态加密硬件加速,具体涉及一种针对ckks同态加密算法中密钥切换算法的硬件加速器。

背景技术:

1、随着信息技术的迅猛发展,数字经济在全球范围内爆发式增长,数据作为新型生产要素的地位愈发凸显。数据的开放共享与高效流通成为驱动经济发展、释放生产力潜能的关键路径。但各数据主体之间、甚至数据主体内部之间都因为数据安全问题而存在数据孤岛现象,导致数据不能进行有效流通,难以发挥数据的价值。因此如何在满足数据流动需求的同时保护数据隐私、防止敏感信息泄露,已成为大数据应用中的重大挑战。

2、同态加密(homomorphic encryption,he)是一种特殊的加密技术,它可以在不解密数据的情况下,对加密数据进行计算,并且得到的结果在解密后与在原始数据上进行相同计算的结果相同。基于以上特点,该技术在云计算、隐私保护等领域具有重要的应用价值。

3、同态加密算法在加密时会引入一定噪声,但在对密文的计算过程中,噪声也将会不断膨胀,直至模糊有效信息进而无法正确解密。对此,密码学界提出了全同态加密(fullyhomomorphic encryption,fhe)方案,通过一种名为“自举”(bootstrapping)的操作不断刷新密文噪声,以达到支持任意次运算。目前学界已提出多种全同态加密算法,其中ckks(cheon-kim-kim-song)算法因其支持浮点数运算和批处理的特点,具有最先进的计算效率,在隐私保护领域得到广泛应用。

4、在ckks算法中,输入的待加密信息是一个复数域向量,可以表示浮点数或复数。该信息首先会通过批量编码技术被编码为整数环上的多项式(该多项式称为明文),并进行一定缩放以保证精度。随后多项式明文再被加密为密文,并可进行后续的密文运算。解密过程即先将密文解密为明文,再解码至可读的消息值。

5、但密文之间的计算算法在数学原理上非常复杂,导致ckks算法仍然表现出较高的计算延迟。具体的研究工作表明,ckks算法的密文计算过程中,密钥切换(keyswitch)操作占计算总延迟的90%以上,是算法延迟的最主要瓶颈。因此针对密钥切换进行加速将对ckks算法的进一步应用具有重要意义。

6、密钥切换主要包括快速数论变换及其逆变换(ntt和intt)和多项式的点值模运算,其中ntt中又主要包括蝶形运算核。近年来,研究人员开始关注针对该密钥切换操作的硬件加速器设计,以提供更好的加速效果。

技术实现思路

1、为解决现有技术中的问题,本发明提出了一种针对ckks同态加密算法中密钥切换算法的硬件加速器。

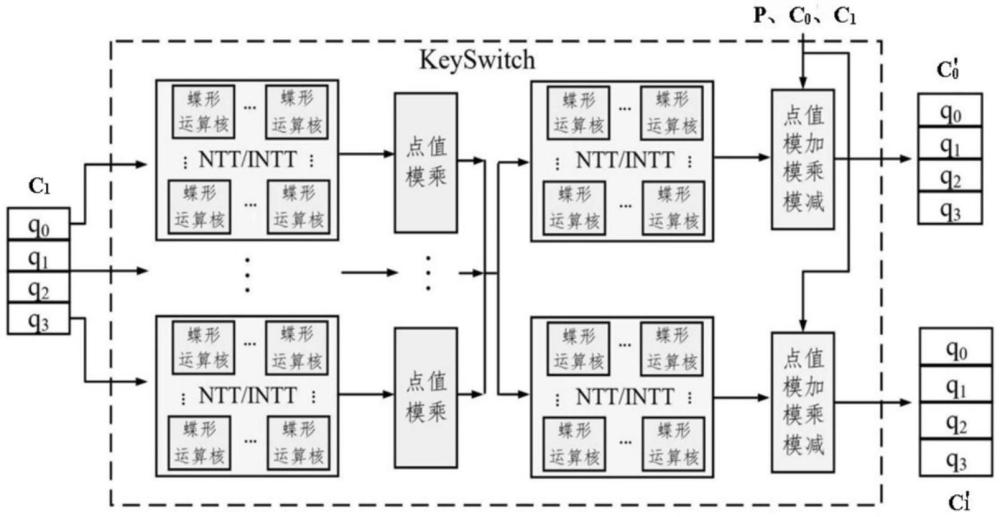

2、本发明的针对ckks同态加密算法中密钥切换算法的硬件加速器包括ntt/intt电路和外围多项式运算电路;

3、ntt/intt电路用于实现多项式的域变换,其包括多个并行的蝶形运算核、用于存储多项式系数的多个片上存储器和一个寄存器组、以及生成内存地址和数据流控制的ntt控制模块;所述外围多项式运算电路包括点值模加模块、点值模乘模块和点值模减模块,各模块分别用于进行相应的点值运算;外部输入密文和外部输入模数经硬件加速器的intt、ntt、多项式点值模乘、模加、模减计算后得到密钥切换操作的输出密文;

4、所述蝶形运算核包括存储阵列、计算阵列和外围数字电路;存储阵列用于存储旋转因子,计算阵列用于计算旋转因子与多项式系数乘法的部分积;外围数字电路由旋转因子写控制电路、地址译码与读地址生成电路、移位加法电路和模约减电路组成。

5、与现有技术相比,本发明所具有的有益效果有:

6、(1)本发明提出了一种新的密钥切换算法加速器架构,基于所设计的ntt和有限状态机,实现高度并行的密钥切换操作,并提出相应的密钥切换算法数据流和流水线架构,解决了其他工作中因数据依赖性而导致的全流水数据流存储开销过大问题,有效降低了电路的面积和功耗。

7、(2)本发明提出了一种新的模约减电路中的模约减方案,采用形如232–2b±2c+1形式的模数,仅需要进行加法、减法、移位操作,避免了计算开销更大的乘法操作。

8、(3)本发明提出了一种新的ntt/intt电路中的ntt数据流设计方案,采用横向数据流与纵数据流结合的方式减少中间数据的读写次数,并采用可复用的旋转因子存储方案,减少访存次数,有效降低了ntt运算的总延时和功耗。

技术特征:

1.一种针对ckks同态加密算法中密钥切换算法的硬件加速器,其特征在于,包括ntt/intt电路和外围多项式运算电路,

2.根据权利要求1所述的硬件加速器,其特征在于,在所述蝶形运算核内,对于每次蝶形计算过程,需要输入两个多项式系数a和b,在运算前通过旋转因子写控制电路将对应的旋转因子w写入存储阵列中,之后再根据地址译码与读地址生成电路产生的地址,读出相应的旋转因子w,并在计算阵列中将其与输入多项式b进行部分积计算;随后,部分积结果将经过移位加法计算,得到旋转因子与多项式系数的64比特乘法结果,即b×w,再通过模约减电路将其约减至32比特并与另一输入多项式a计算,最终得到多项式系数输出结果a+b·wmodq和a-b·wmod q,完成一次蝶形计算,其中,q为模数。

3.根据权利要求2所述的硬件加速器,其特征在于,所述模数q位宽为32比特,所述模约减电路进行模约减算法时,取q=232-2b±2c+1,b、c为预设常数,即有:

4.根据权利要求1所述的硬件加速器,其特征在于,所述ntt/intt电路包含了128个蝶形运算核,用于存储多项式系数的128个片上存储器和一个寄存器组,以及生成内存地址和数据流控制的ntt控制模块。

5.根据权利要求1所述的硬件加速器,其特征在于,所述ntt/intt电路将ntt/intt计算过程分为横向处理和纵向处理两部分;

6.根据权利要求5所述的硬件加速器,其特征在于,横向处理中每一级的旋转因子数均不超para,横向处理每一级蝶形计算所需的旋转因子存储在para个存储阵列的同一深度上。

7.根据权利要求5或6所述的硬件加速器,其特征在于,纵向处理采用跨级共享的方式存储旋转因子,ntt/intt电路最后一级蝶形计算的旋转因子将存储在横向处理旋转因子之后;从存储阵列中深度为log2 para+1的位置开始,首先将指数为偶数次的旋转因子存储在深度log2 para+1至深度log2 para+n/(4para)-1处,然后,将指数为奇数次的旋转因子存储在接下来的深度log2 para+n/(4para)至深度log2 para+n/(2para)-1处,由于深度从0开始编号,因此蝶形运算核中使用的存储阵列总深度为log2 para+n/(2para)。

技术总结

本发明公开了一种针对CKKS同态加密算法中密钥切换算法的硬件加速器,属于隐私计算和全同态加密硬件加速领域。该硬件加速器包括NTT/INTT电路和外围多项式运算电路,NTT/INTT电路用于实现多项式的域变换,其包括多个并行的蝶形运算核以及生成内存地址和数据流控制的NTT控制模块;所述蝶形运算核包括存储阵列、计算阵列和外围数字电路;存储阵列用于存储旋转因子,计算阵列用于计算旋转因子与多项式系数乘法的部分积。本发明硬件加速器可以实现高度并行的密钥切换操作,解决了其他工作中因数据依赖性而导致的全流水数据流存储开销过大问题,有效降低了电路的面积和功耗。

技术研发人员:王田宇,叶泽文,黄科杰

受保护的技术使用者:浙江大学

技术研发日:

技术公布日:2025/4/6

- 还没有人留言评论。精彩留言会获得点赞!