发光二极管驱动器以及发光二极管驱动设备的制作方法

1.本公开总地涉及显示领域,具体涉及一种发光二极管(light-emitting diode;led)驱动器以及包括led驱动器的led驱动设备。

背景技术:

2.通常,在led显示系统中采用级联的led驱动器来驱动led进行显示。在级联led驱动器之间,一般采用串行外设接口(spi),各个led驱动器需要设置独立的用于接收数据信号的数据信号引脚和用于接收时钟信号的时钟信号引脚。因为不仅需要使用数据信号线来进行数据传输,还需要使用公共时钟信号线来传输时钟信号,以便利用接收到的时钟信号对数据进行采样。换句话说,在级联的led驱动器之间需要设置单独的时钟信号线以及相应的硬件引脚,以便将时钟信号与数据信号分开进行传输,从而使得led显示系统能够正常工作。如图1所示,级联的各个led驱动器1,2,

…

n之间设置有公共时钟信号线,以便为各级led驱动器提供时钟信号sclk。

技术实现要素:

3.根据本公开的一方面,提出了一种led驱动器,其包括:解码电路,接收数据信号并从中解码出用于驱动led发光显示的显示数据和恢复时钟信号;以及编码电路,利用恢复时钟信号对解码的显示数据进行编码以产生编码数据信号,其中,所述数据信号是以第一编码格式编码的,而所述编码数据信号是采用第二编码格式编码的,其中,第一编码格式和第二编码格式也可以采用不同的编码格式。

4.可选地,根据上述的led驱动器,第一编码格式和第二编码格式中的至少一个可以采用曼彻斯特编码格式和四级脉幅调制pam4编码格式之一。

5.可选地,根据上述的led驱动器,在第一编码格式采用曼彻斯特编码格式的情况下,所述解码电路可以包括:第一延迟电路,对接收的数据信号的时序进行延迟,产生第一恢复数据信号;第一采样电路,对接收的数据信号进行采样,产生第二恢复数据信号;以及第一逻辑运算电路,对第一恢复数据信号和第二恢复数据信号进行逻辑运算,产生解码的显示数据和恢复时钟信号;其中,第一采样电路利用恢复时钟信号对接收的数据信号进行采样。

6.可选地,根据上述的led驱动器,第一延迟电路可以对接收的数据信号进行1/4周期延迟,以产生第一恢复数据信号。

7.可选地,根据上述的led驱动器,第一采样电路可以包括:第二延迟电路,接收第一逻辑运算电路产生的恢复时钟信号,并对恢复时钟信号进行1/2周期延迟而产生采样时钟信号;以及第一寄存器,利用所述采样时钟信号对接收的数据信号进行采样,产生第二恢复数据信号。

8.可选地,根据上述的led驱动器,第一逻辑运算电路可以包括:第一逻辑门电路,对第一恢复数据信号和第二恢复数据信号进行异或运算,产生所述恢复时钟信号;以及第二

逻辑门电路,对第二恢复数据信号进行反相,以产生解码的显示数据。

9.可选地,根据上述的led驱动器,在第二编码格式采用曼彻斯特编码格式的情况下,所述编码电路可以包括:第一数据转换电路,利用基于恢复时钟信号生成的第一时钟信号对解码的显示数据进行转换而产生第一转换数据;第二采样电路,对第一转换数据进行采样而产生第二转换数据;以及第二逻辑运算电路,对第二转换数据和基于恢复时钟信号生成的第二时钟信号进行逻辑运算而产生编码数据信号。

10.可选地,根据上述的led驱动器,第一数据转换电路可以包括:第一分频电路,对接收的恢复时钟信号进行分频产生第二时钟信号,并将所述第二时钟信号作为第一时钟信号输出;第二寄存器,利用第一时钟信号对解码的显示数据进行采样,并输出第一经采样数据;第三寄存器,利用与第一时钟信号反相的信号对解码的显示数据进行采样,并输出第二经采样数据;以及数据选择器,接收第一经采样数据和第二经采样数据,并基于第一时钟信号的电平选择第一经采样数据和第二经采样数据之一作为第一转换数据输出给第二采样电路。

11.可选地,根据上述的led驱动器,第一数据转换电路可以包括第一分频电路,对接收的恢复时钟信号进行分频产生第二时钟信号;相位延迟电路,所述相位延迟电路对第一分频电路输出的第二时钟信号进行相位延迟,并将经相位延迟的第二时钟信号作为所述第一时钟信号输出;第二寄存器,利用第一时钟信号对解码的显示数据进行采样,并输出第一经采样数据;第三寄存器,利用与第一时钟信号反相的信号对解码的显示数据进行采样,并输出第二经采样数据;以及数据选择器,接收第一经采样数据和第二经采样数据,并基于第一时钟信号的电平选择第一经采样数据和第二经采样数据之一作为第一转换数据输出给第二采样电路。

12.可选地,根据上述的led驱动器,第一经采样数据可以由第二寄存器的第二数据输出端输出,而第二经采样数据可以由第三寄存器的第一数据输出端输出。

13.可选地,根据上述的led驱动器,第二采样电路可以包括:第四寄存器,利用与恢复时钟信号反相的信号对第一转换数据进行采样,并输出第二转换数据。

14.可选地,根据上述的led驱动器,第二逻辑运算电路可以包括:第三逻辑门电路,对第一分频电路输出的第二时钟信号与第二转换数据进行异或运算,产生编码数据信号。

15.可选地,根据上述的led驱动器,在第一编码格式采用pam4编码格式的情况下,所述解码电路可以包括:预处理电路,对接收的数据信号进行预处理并输出经预处理的数据信号;比较器电路,将经预处理的数据信号与相应的阈值信号进行比较,产生相应的位元温度计码;pam4解码器,对位元温度计码进行解码并输出解码的数据信号。

16.可选地,根据上述的led驱动器,所述比较器电路可以包括:第一比较器、第二比较器和第三比较器,其中,第一、第二和第三比较器设定了不同的阈值信号,并且分别将经预处理的数据信号与不同的阈值信号进行比较而产生相应的位元温度计码。

17.可选地,根据上述的led驱动器,解码电路还可以包括时钟恢复电路和第二数据转换电路,其中,所述时钟恢复电路接收来自第一、第二和第三比较器之一输出的位元温度计码,从中提取恢复时钟信号并将其输出给第二数据转换电路;所述第二数据转换电路,利用恢复时钟信号对pam4解码器输出的解码的数据信号进行转换,产生二元形式的解码显示数据。

18.可选地,根据上述的led驱动器,第二数据转换电路可以包括:第五寄存器和第六寄存器,利用恢复时钟信号对pam4解码器输出解码的数据信号进行采样,以分别输出第三经采样数据和第四经采样数据作为二元形式的解码显示数据。

19.可选地,根据上述的led驱动器,在第一编码格式采用pam4编码格式且第二编码格式采用曼彻斯特编码格式的情况下,所述解码电路还可以包括:接口电路,接收第三经采样数据和第四经采样数据,并基于恢复时钟信号的电平选择第三经采样数据和第四经采样数据之一作为解码的显示数据。

20.根据本公开的另一方面,提出了一种发光二极管led驱动设备,其包括串行连接的n级led驱动器,其中,第一级led驱动器接收初始数据信号并输出第一级数据信号,第k级led驱动器接收第k-1级led驱动器输出的第k-1级数据信号并输出第k级数据信号,1《k≤n。

21.根据本公开提出的led驱动器以及相应的led驱动设备,由于不再需要单独传输时钟信号,而是通过对在各级led驱动器之间传输的数据信号进行相应的编码,将时钟信号嵌入到数据信号中,相应取消了各级led驱动器之间单独传输时钟信号的硬件设置,降低了印刷电路板布线复杂度,并且降低了产品的成本;此外,还可以降低led驱动设备的耗电和电磁干扰,从而提高了led的显示质量。

附图说明

22.图1示出了传统的led驱动设备的示意性架构。

23.图2a-2c示出了时钟信号与数据信号采用不同的传输路径进行传输可能引起的采样问题。

24.图3示出了根据本公开一实施例的led驱动设备的示意性架构。

25.图4是根据本公开一实施例的led驱动器的示意性框图。

26.图5是根据本公开另一实施例的led驱动器的示意性框图。

27.图6是根据本公开一实施例的对一数据位元进行编码以及相应解码的示意图。

28.图7是根据图6所示的编码方式对一数据流进行编码以及相应的解码的示意图。

29.图8a-8d是根据本公开一实施例的利用不同的编码方式对两个连续数据位元进行编码以及相应解码的示意图。

30.图8e是分别根据图8a-8d所示的不同编码方式对一数据流进行编码以及相应解码的示意图。

31.图9是根据本公开一实施例的led驱动器中的解码电路的示意性框图。

32.图10a-10b是根据本公开一实施例的led驱动器中的解码电路以及相应信号时序的示意图。

33.图11是根据本公开一实施例的led驱动器中的编码电路的示意性框图。

34.图12a-12b是根据本公开一实施例的led驱动器中的编码电路以及相应信号时序的示意图。

35.图13是根据本公开又一实施例的led驱动器中的编码电路的电路示意图。

36.图14是根据本公开的一实施例的利用四级脉幅调制(pam4)对数据进行编码的示意图。

37.图15是示出根据本公开的一实施例的对pam4编码的数据信号进行解码的解码电

路的示意图。

38.图16是根据本公开的一实施例的编码电路和解码电路之间的接口电路的示意图。

39.图17是根据本公开的一实施例的led驱动器中接收数据的接收器rx的示意图。

40.图18是根据本公开的一实施例的led驱动器中发送数据的发送器tx的示意图。

具体实施方式

41.现在参考附图来描述主题,其中,全文中相似的参考标号用于指代相似的元件。在下面的描述中,出于解释的目的,阐述了许多具体细节以便提供对主题的透彻理解。然而,显然的是,在没有这些具体细节的情况下也可以实施本原理。

42.本说明书示出了本公开的原理。因此,可以理解的是,尽管本文未明确描述或示出,但是本领域技术人员能够设计出体现本公开原理的各种配置。

43.本原理自然不限于在此描述的实施例。

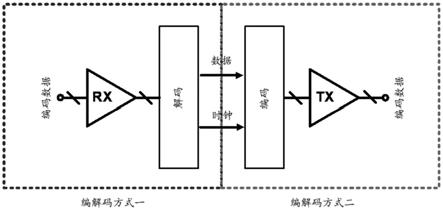

44.图1示出了传统的led驱动设备的示意性架构。如图1所示,其传输接口采用串行外设接口(spi or serial peripheral interface),数据信号data和时钟信号sclk被输入给led驱动器1,经由级联串接的方式,通过驱动器1将数据传输给驱动器2,驱动器2再将数据传输给驱动器3,以此类推。在所有驱动器1-n电路都收到数据后,再同步将数据data输出给led显示系统从而显示画面。此外,级联的各级led驱动器之间还连接有公共的时钟信号线,从而可以接收时钟信号sclk,并且各级led驱动器通过利用时钟信号sclk对接收到的数据信号data进行采样。

45.由于时钟信号和数据信号采用不同的传输路径进行传输,这可能会产生问题。图2a-2c示出了时钟信号与数据信号采用不同的传输路径进行传输可能导致的采样问题。

46.如图2a所示,在发送端和接收端之间通过两条传输路径分别传输时钟信号和数据信号。如果由于某些原因,例如,由于工艺或者材料等原因,印刷电路板(pcb)布线不当,当传输时钟信号的路径的长度l1不等于传输数据信号的路径的长度l2时,会造成接收端取样或保持时间的损失。如图2b所示,假设发送端发送一组数据信号和时钟信号,为保证在利用时钟信号对数据信号进行采样时具有最佳的采样和保持时间,例如,理想的最佳采样时间和保持时间皆为0.5ui。然而,由于传输路径l1和l2之不匹配,实际到达接收端的数据信号和时钟信号的时序如图2c所示,则在这种情况下,将剩下0.2ui的采样时间而损失了0.3ui的采样时间。

47.为此,根据本公开的原理,通过对待传输的数据进行编码,将时钟信号嵌入编码后的数据信号中,从而在各级led驱动器之间仅仅传输编码后的数据信号,而不再需要提供额外的时钟信号,消除了由于设置两条传输路径分别传输数据信号和时钟信号时不同传输路径之间可能存在的不匹配所导致的对数据进行采样的精度和稳定度的影响。

48.图3示出了根据本公开一实施例的led驱动设备的示意性架构。与图1所示的常规led驱动设备相比,取消了向各级led驱动器单独提供时钟信号,而是在各级led驱动器之间传输经编码的数据信号,其中通过对经编码的数据信号进行解码,可以恢复出数据和时钟信号。

49.图4示出了根据本公开一实施例的可用于图3所示的led驱动设备的单级led驱动器的示意性框图。如图4所示,该led驱动器,包括解码电路,其接收数据信号并从中解码用

于驱动led发光显示的显示数据data和恢复时钟信号clk;以及编码电路,其利用恢复时钟信号对解码的显示数据进行编码以产生编码数据信号,其中,所述数据信号是以第一编码格式编码的,而所述编码数据信号是采用第二编码格式编码的。

50.图4还示出了通过接收器rx从外部接收编码的数据信号,例如,从前一级led驱动器或者从控制器接收编码的数据信号,而通过发送器tx向下一级led驱动器发送经编码的数据信号。

51.可选地,第一级led驱动器亦可直接接收未经过任何编码的数据信号。

52.可选地,根据本公开的实施例,可以在单级led驱动器内采用多种编解码方式。图5是根据本公开一实施例的led驱动器的示意性框图。例如,如图5所示,接收器rx可接收编码方式一的数据信号,并通过解码方式一解码,以生成解码后的数据data和恢复的时钟信号clk,然后可再通过编码器使用编码方式二对解码后的数据data进行编码,以生成经编码的数据信号,并通过发送器rx将经编码的数据信号发送给下一级led驱动器,而该下一级led驱动器的接收器再以相对应的解码方式进行解码。

53.利用本公开的原理的led驱动器以及驱动设备,可以实现以下优点:

54.例如,由于取消了单独传输时钟信号,相应取消了在各级led驱动器之间设置的时钟信号线以及对应的硬件引脚,可以降低印刷电路板的布线复杂度、节省印刷电路板的使用层数,降低印刷电路板成本。

55.另外,通过使用某种编码方式对待传输的数据信号进行编码,无需单独传输时钟信号,还可以降低驱动电路耗电和电磁干扰,并可减小芯片面积、降低芯片封装成本。

56.此外,如果在各级led驱动器的发送端和接收端使用不同编码和解码方式,例如,如果若交叉混用不同编解码方式,由于数据流同时以不同形式传输并且使用不同带宽,还可以实现进一步降低电磁干扰的益处。

57.根据本公开的原理,提出了通过使用某种编码方式对待传输的数据信号进行编码,无需在各级led驱动器之间单独传输时钟信号。由于将时钟信号内嵌于数据信号中,通过接收端对采样时钟信号和数据进行恢复,因此,不会造成sclk和data在传输过程中之偏移,也不会对时钟信号和数据的同步特性造成不利影响。图6是根据本公开一实施例的对一数据位元进行编码以及相应解码的示意图。如图6所示,例如,可以采用曼彻斯特编码方式将数据信号(例如,数据流)中的数据位元“1”编码为“01”,而将数据位元“0”编码为“10”。相应地,在接收到数据信号时,采用对应的解码方式,例如,将“01”解码为数据位元“1”而将“10”解码为数据位元0。图7是根据图6所示的编码方式对一数据流进行编码以及从编码的数据信号中对数据位元进行解码的示意图。

58.图8a-8d是根据本公开另一实施例的利用不同的编码方式对两个连续数据位元进行编码以及相应解码的示意图。

59.例如,根据一实施例,如图8a所示,在发送数据流之前,先对数据流进行编码时,将连续的两个数据位元“00”编码为“1010”,将连续的两个数据位元“01”编码为“1001”,将连续的两个数据位元“10”编码为“0110”,而将连续的两个数据位元“11”编码为“0101”,然后向下一级发送编码后的数据信号。相应地,在接收到编码后的数据信号时,采用对应的解码方式进行解码,将“1010”解码为连续的两个数据位元“00”,将“1001”解码为连续的两个数据位元“01”,将“0110”解码为连续的两个数据位元“10”,而将“0101”解码为连续的两个数

据位元“11”。

60.可选地,根据另一实施例,如图8b所示,在发送数据流之前,先对数据流进行编码时,将连续的两个数据位元“00”编码为“0101”,将连续的两个数据位元“01”编码为“0110”,将连续的两个数据位元“10”编码为“1001”,而将连续的两个数据位元“11”编码为“1010”,然后向下一级发送编码后的数据信号。相应地,在对接收到的编码后的数据信号时,采用对应的解码方式进行解码,将“0101”解码为连续的两个数据位元“00”,将“0110”解码为连续的两个数据位元“01”,将“1001”解码为连续的两个数据位元“10”,而将“1010”解码为连续的两个数据位元“11”。

61.可选地,根据又一实施例,如图8c所示,在发送数据流之前,先对数据流进行编码时,将连续的两个数据位元“00”编码为“1001”,将连续的两个数据位元“01”编码为“1010”,将连续的两个数据位元“10”编码为“0101”,而将连续的两个数据位元“11”编码为“0110”,然后向下一级发送编码后的数据信号。相应地,在接收到编码后的数据信号时,采用对应的解码方式进行解码,将“1001”解码为连续的两个数据位元“00”,将“1010”解码为连续的两个数据位元“01”,将“0101”解码为连续的两个数据位元“10”,而将“0110”解码为连续的两个数据位元“11”。

62.可选地,根据再一实施例,如图8d所示,在发送数据流之前,先对数据流进行编码时,将连续的两个数据位元“00”编码为“0110”,将连续的两个数据位元“01”编码为“0101”,将连续的两个数据位元“10”编码为“1010”,而将连续的两个数据位元“11”编码为“1001”,然后向下一级发送编码后的数据信号。相应地,在对接收到的编码后的数据信号时,采用对应的解码方式进行解码,将“0110”解码为连续的两个数据位元“00”,将“0101”解码为连续的两个数据位元“01”,将“1010”解码为连续的两个数据位元“10”,而将“1001”解码为连续的两个数据位元“11”。

63.图8e是分别根据图8a-8d所示的四种编码方式分别对一数据流进行编码的示意图。此外,如上所述,如果在各级led驱动器的发送端和接收端使用不同编码和解码方式,例如,如果若交叉混用不同编解码方式,例如,交叉混用图8a-8d所示的四种编解码方式,由于数据流同时以不同形式传输并且使用不同带宽,还可以实现进一步降低电磁干扰的益处。

64.图9示出了根据本公开一实施例的led驱动器中的解码电路的示意性框图。图9示出的解码电路可以用于对接收到的采用曼彻斯特编码方式编码的数据信号进行解码,并且从中恢复数据data和时钟信号。如图9所示,该解码电路包括:第一延迟电路,对接收的数据信号的时序进行延迟,产生第一恢复数据信号;第一采样电路,对接收的数据信号进行采样,产生第二恢复数据信号;以及第一逻辑运算电路,对第一恢复数据信号和第二恢复数据信号进行逻辑运算,产生解码的显示数据和恢复时钟信号;其中,第一采样电路利用恢复时钟信号对接收的数据信号进行采样。

65.根据本公开的一实施例,第一延迟电路对接收的数据信号进行1/4周期延迟,以产生第一恢复数据信号。

66.可选地,第一采样电路包括:第二延迟电路,接收第一逻辑运算电路产生的恢复时钟信号,并对恢复时钟信号进行1/2周期延迟而产生采样时钟信号;以及第一寄存器,利用所述采样时钟信号对接收的数据信号进行采样,产生第二恢复数据信号。

67.可选地,第一逻辑运算电路包括:第一逻辑门电路,对第一恢复数据信号和第二恢

复数据信号进行异或运算,产生所述恢复时钟信号;以及第二逻辑门电路,对第二恢复数据信号进行反相,以产生解码的显示数据。

68.作为示例,图10a示出根据本公开一实施例的led驱动器中的解码电路的具体结构的示意图。

69.如图10a所示,在接收到编码的数据信号后,第一延迟电路将编码的数据信号延迟1/4周期((1/4)tb,其中tb表示编码数据信号的周期),产生第一恢复数据信号a;第一采样电路(dff1),对接收到的编码的数据信号进行采样,产生第二恢复数据信号b;第一逻辑运算电路中的第一逻辑门电路(xor1),对第一恢复数据信号a和第二恢复数据信号b进行“异或(xor)”逻辑运算,从而产生恢复时钟信号;第一逻辑运算电路中的第二逻辑门电路,对第二恢复数据信号b进行反相,以产生解码的显示数据。

70.可选地,如图10a所示,第一采样电路中的第二延迟电路,接收第一逻辑运算电路产生的恢复时钟信号,并对恢复时钟信号进行1/2周期((1/2)tb,其中tb表示编码数据信号的周期)延迟而产生采样时钟信号rck1;以及第一采样电路中的第一寄存器dff1,利用所述采样时钟信号rck1对接收的数据信号进行采样,产生第二恢复数据信号b。

71.图10b是示出了对应于图10a所示的解码电路的相应信号的时序的示意图。如图10b所示,接收到的编码数据信号经过1/4周期延迟后得到第一恢复数据信号a,第一恢复数据信号a与第一寄存器dff1输出的第二恢复数据信号b经过异或运算,得到恢复时钟信号,恢复时钟信号经由1/2周期延迟得到采样时钟信号rck1,其中,第二恢复数据信号b是通过第一寄存器dff1利用采样时钟信号rck1的上升沿对接收到的编码数据信号进行采样而获得的,而第二恢复数据信号b经过逻辑门反相,得到解码的数据。作为示例,在图10b示出的数据信号中,d0b、d1b、d2b、d3b、d4b、d5b表示数据位元d0、d1、d2、d3、d4、d5的反相后的位元。

72.图11示出了根据本公开一实施例的led驱动器中的编码电路的示意性框图。图11示出的编码电路可以用于对数据流进行曼彻斯特编码,从而产生编码后的数据信号。

73.如图11所示,编码电路包括:第一数据转换电路,利用基于恢复时钟信号生成的第一时钟信号对解码的显示数据进行转换而产生第一转换数据;第二采样电路,对第一转换数据进行采样而产生第二转换数据;以及第二逻辑运算电路,对第二转换数据和基于恢复时钟信号生成的第二时钟信号进行逻辑运算而产生编码数据信号。可选的,所述第一时钟信号与所述第二时钟信号相同,或者所述第一时钟信号是所述第二时钟信号的相位延迟的信号。

74.根据本公开的一实施例,其中,第一数据转换电路包括:第一分频电路,对接收的恢复时钟信号进行分频产生第二时钟信号,并将所述第二时钟信号作为第一时钟信号输出;第二寄存器,利用第一时钟信号对解码的显示数据进行采样,并输出第一经采样数据;第三寄存器,利用与第一时钟信号反相的信号对解码的显示数据进行采样,并输出第二经采样数据;以及数据选择器,接收第一经采样数据和第二经采样数据,并基于第一时钟信号的电平选择第一经采样数据和第二经采样数据之一作为第一转换数据输出给第二采样电路。

75.可选地,第一数据转换电路包括:第一分频电路,对接收的恢复时钟信号进行分频产生第二时钟信号;相位延迟电路,对第一分频电路输出的第二时钟信号进行相位延迟,并

将经相位延迟的第二时钟信号作为所述第一时钟信号输出。此外,第一数据转换电路还包括:第二寄存器,利用第一时钟信号对解码的显示数据进行采样,并输出第一经采样数据;第三寄存器,利用与第一时钟信号反相的信号对解码的显示数据进行采样,并输出第二经采样数据;以及数据选择器,接收第一经采样数据和第二经采样数据,并基于第一时钟信号的电平选择第一经采样数据和第二经采样数据之一作为第一转换数据输出给第二采样电路。

76.可选地,第一经采样数据由第二寄存器的第二数据输出端输出,而第二经采样数据由第三寄存器的第一数据输出端输出。

77.可选地,第二采样电路包括:第四寄存器,利用与恢复时钟信号反相的信号对第一转换数据进行采样,并输出第二转换数据。

78.可选地,第二逻辑运算电路包括:第三逻辑门电路,对第一分频电路输出的第二时钟信号与第二转换数据进行异或运算,产生编码数据信号。

79.作为示例,图12a示出根据本公开一实施例的led驱动器中的编码电路的示意图。根据一实施例,在编码电路中,在接收到待编码的数据流之后,通过第一数据转换电路(例如包括串行转并行电路以及相应的数据选择器)利用恢复时钟信号对待编码的数据流进行数据转换,产生第一转换数据,第二采样电路(例如,包括相应的寄存器)对第一转换数据进行采样而产生第二转换数据,而第二逻辑运算电路通过对第二转换数据和基于恢复时钟信号得到的采样时钟进行逻辑运算而产生编码的数据信号。

80.如图12a所示,通过串行转并行电路利用恢复时钟信号f

ck

将待编码的数据流转换为奇数位元dodd和偶数位元deven的并行输出,并且利用相应的数据选择器对并行输出的奇数位元和偶数位元进行选择,从而产生第一转换数据out1;第二采样电路对第一转换数据out1进行采样而产生第二转换数据out2;而第二逻辑运算电路通过对第二转换数据out2和基于恢复时钟信号的第二时钟信号进行逻辑运算而产生编码的数据信号。

81.图12b是示出了对应于图12a所示的编码电路的相应信号的时序的示意图。如图12b所示,解码数据表示待编码的数据流。f

ck

表示恢复时钟信号,(f

ck

/2)表示对恢复时钟信号进行二分频后产生的作为采样时钟的第二时钟信号,out1表示第一转换数据,out2表示第二转换数据,编码数据表示编码后的数据信号。

82.作为示例,可以结合图13所示的编码电路的结构来具体说明对数据流进行编码的过程。如图13所示,将待编码的数据流输入到第一数据转换电路中的第二寄存器和第三寄存器的数据端,将恢复时钟信号rck经过第一分频电路进行二分频之后,产生第二时钟信号rck2,并将其作为第一时钟信号rck2(其被用作采样时钟),第二寄存器利用第一时钟信号rck2对待编码的数据流进行采样,并且经由其第二输出端/q输出第一经采样数据a,而第三寄存器利用与第一时钟信号rck2反相的信号对待编码的数据流进行采样,并且经由其第一输出端q输出第二经采样数据b;数据选择器利用第一时钟信号rck2的电平来选择第一经采样数据和第二经采样数据之一作为第一转换数据out1输出给第二采样电路中的第四寄存器,第四寄存器利用与恢复时钟信号反相的信号对第一转换数据out1进行采样,并且输出第二转换数据out2;第二逻辑运算电路中的第三逻辑门电路,对第一分频电路输出的第二时钟信号rck2与第二转换数据进行异或运算,产生编码的数据信号。

83.可选地,如图13所示,还可以包括相位延迟电路,所述相位延迟电路对第一分频电

路输出的第二时钟信号进行相位延迟phi(π)(即,将第二时钟信号相位延迟1/2周期),并将经相位延迟的第二时钟信号作为所述第一时钟信号输出给第二寄存器和第三寄存器。

84.根据本公开的一实施例,还提供了一种对数据流进行编码的另一种方式,即,利用四级脉幅调制(pam4)的编码方式。图14是根据本公开的一实施例的利用四级脉幅调制(pam4)对数据进行编码的示意图。如图14所示,通过将两个位元数据调制在信号振幅上,可以将四组数据位元(00,01,11,10)对应于不同振幅大小,从而实现对数据流的压缩编码,并且实现只使用一半频宽的益处。

85.根据本公开的一实施例,提供了一种对通过pam4编码格式编码的数据信号进行解码的解码电路,该解码电路包括:预处理电路,对接收的数据信号进行预处理并输出经预处理的数据信号;比较器电路,将经预处理的数据信号与相应的阈值信号进行比较,产生相应的位元温度计码;以及pam4解码器,对位元温度计码进行解码并输出解码的数据信号。

86.可选地,所述比较器电路包括:第一比较器、第二比较器和第三比较器,其中,第一、第二和第三比较器设定了不同的阈值信号,并且分别将经预处理的数据信号与不同的阈值信号进行比较而产生相应的位元温度计码。

87.可选地,所述解码电路还包括时钟恢复电路和第二数据转换电路,其中,所述时钟恢复电路接收来自第一、第二和第三比较器之一输出的位元温度计码,从中提取恢复时钟信号并将其输出给第二数据转换电路;所述第二数据转换电路,利用恢复时钟信号对pam4解码器输出的解码的数据信号进行转换,产生二元形式的解码显示数据(即,解码显示数据包括两个元素)。

88.可选地,第二数据转换电路包括:第五寄存器和第六寄存器,利用恢复时钟信号对pam4解码器输出解码的数据信号进行采样,以分别输出第三经采样数据和第四经采样数据作为二元形式的解码显示数据(即,第三经采样数据和第四经采样数据作为解码显示数据的两个元素)。

89.例如,如图14所示,由于利用pam4编码方式分别将数据流的位元组00,01,11,10编码至不同的电压振幅基准,在接收到编码后的pam4数据信号后,可以经过第一级放大器放大且均衡化,然后先经过由三组具有不同临界值的比较器进行量化,从而将pam4编码信号转换成位元温度计码,再通过位元温度计码转二进制码解码器(thermometer code to binary code decoder),将该信号转换二进制码形式,从而完成将具有多电压基准的信号转换至二进制电压基准信号,并且利用由时钟数据恢复电路cdr产生的恢复时钟信号通过对该二进制电压基准信号进行采样而产生恢复数据流。尽管在图15中没有明确示出,可选地,在该解码电路的放大器之前,可以设置相应的信号预处理器电路,以便例如对接收到的pam4编码数据信号进行预处理,例如,信号整形、均衡化等等。当然,这些预处理也可以结合信号的放大处理一并进行。

90.图15是示出根据本公开的一实施例的对pam4编码的数据信号进行解码的解码电路的示意图。如图15所示,接收的pam4编码的数据信号通过放大器进行放大处理(如上所述,可以一并进行信号的整形、均衡化的预处理),将放大后的信号送入三组比较器comp.a,comp.b和comp.c进行比较量化,由于三组比较器分别设置有不同的阈值,因此可以根据接收的放大信号的幅度,输出不同的位元温度计码,将不同的位元温度计码输出给位元温度计码转二进制码解码器(例如,图15所示的pam4解码器),可以将其转换至二进制电压基准。

此外,如图15所示,通过时钟数据恢复电路(clock and data recovery,cdr)从例如第二组比较器输出的位元温度计码vout,b中提取出正确的频率和相位的恢复时钟信号,并且通过该恢复时钟信号对位元温度计码转二进制码解码器输出的二进制数据信号进行采样,例如,通过将恢复时钟信号作为第五和第六寄存器的采样时钟,从而对位元温度计码转二进制码解码器输出的二进制数据信号进行采样,来实现对数据的恢复。

91.根据本公开的一实施例,可以在各级led驱动器之间采用不同编码方式,并且通过相应的接口电路来实现不同编解码方式之间的转换。以曼彻斯特编码转换至pam4编码为例,可以采用曼彻斯特解码器搭配pam4编码器,换句话说,可以采用曼彻斯特解码器对接收到的以曼彻斯特编码方式编码的数据信号进行解码,得到待传输的数据流,然后,可以采用pam4编码器对待传输的数据流进行编码,并将编码后的数据信号发送给下一级led驱动器;反之,当将pam4编码转换至曼彻斯特编码时,可以采用pam4解码器搭配曼彻斯特编码器,具体而言,可以采用pam4解码器对接收到的以pam4编码方式编码的数据信号进行解码,得到待传输的数据流,然后,可以采用曼彻斯特编码器对待传输的数据流进行编码,并将编码后的数据信号发送给下一级led驱动器。

92.此外,应注意,尽管本公开作为示例,列举了可以采用曼彻斯特编码方式和pam4编码方式对待传输的数据流进行编码和相应的解码,但本实用新型技术方案不限于这两种编码方式,而是可以涵盖其他类型的编码方式,只要相应的编码方式可以实现对数据流的编码,以便将时钟信号嵌入到编码后的数据信号中,并且在对编码后的数据信号进行解码时,可以恢复出编码之前的数据流和时钟信号即可。

93.作为示例,图16示出了根据本公开的一实施例的编码电路和解码电路之间的示意性的接口电路。如图16所示,由pam4解码器产生的恢复数据和恢复时钟信号经由一组串行器(serializer)产生串行的数据,并且将产生的串行数据和恢复时钟信号送入如图12a所示的编码电路,从而对串行数据和恢复时钟信号进行编码后,即可完成pam4编码至曼彻斯特编码的转换。

94.作为示例,图17示出了可以用于图4和/或图5中所示的接收器rx的具体电路。如图17所示,该接收器可以采用差分电路的形式,其中,可以通过图17所示的din+和/或din-端子接收如图3中所示的数据信号data,并且通过voutn和voutp端子将接收器rx输出的信号提供给相应的解码器。作为示例,接收器接收的数据信号可以是单端信号或者双端差动信号,接收器输出的信号也可以是是单端信号或者双端信号(例如差动信号),

95.作为示例,图18示出了可以用于图4和/或图5中所示的发送器tx的具体电路。如图18所示,该发送器可以采用全差分电路的形式,其中,可以通过图18所示的din+和/或din-端子接收如图4和/或图5中所示的编码后的数据信号,并且通过vout+和vout-端子(例如,可以将其对应于图3所示的sdout引脚)将信号输出给下一级的led驱动器的接收器rx。作为示例,编码后的数据信号可以是单端信号或者双端信号(例如,差动信号)。

96.根据本公开提出的led驱动器以及相应的led驱动设备,由于不再需要单独传输时钟信号,而是通过对在各级led驱动器之间传输的数据信号进行相应的编码,将时钟信号嵌入到数据信号中,相应取消了各级led驱动器之间单独传输时钟信号的硬件设置,降低了印刷电路板布线复杂度,并且降低了产品的成本;此外,还可以降低led驱动设备的耗电和电磁干扰,从而提高了led的显示质量。

97.本技术描述了包括工具,特征,实施例,模型,方法等的各种方面。这些方面中的许多是专门描述的,并且至少为了示出各个特征,通常以听起来可能受到限制的方式来描述。然而,这是出于描述清楚的目的,并且不限制那些方面的应用或范围。实际上,所有不同方面都可以组合和互换以提供其他方面。此外,这些方面也可以与先前申请中描述的方面组合和互换。

98.当附图作为流程图呈现时,应当理解,其还提供对应装置的框图。类似地,当附图作为框图呈现时,应当理解,其还提供对应方法/过程的流程图。

99.本文描述的实现方式和方面可以在例如方法或处理,装置,软件程序,数据流或信号中实现。即使仅在单个实现形式的上下文中讨论(例如,仅作为方法讨论),讨论的特征的实现方式也可以以其他形式(例如,装置或程序)来实现。装置可以在例如适当的硬件,软件和固件中实现。方法例如可以在例如处理器中实现,该处理器一般指代处理设备,包括例如计算机,微处理器,集成电路或可编程逻辑设备。处理器也包括通信设备,例如计算机,蜂窝电话,便携/个人数字助理(“pda”),以及便于终端用户之间的信息通信的其他设备。

100.对“一个实施例”或“实施例”或“一个实现方式”或“实现方式”的引用以及其其他变型意味着结合实施例描述的具体特征,结构,特性等包括在至少一个实施例中。因此,在整个文件中出现在各个地方的短语“在一个实施例中”或“在实施例中”或“在一个实现方式中”或“在实现方式中”以及任何其他变型的出现不一定都指代同一个实施例。

101.我们描述许多实施例。这些实施例的特征可以单独提供或以任何组合提供。此外,实施例可以单独或以任何组合而跨各种权利要求类别和类型包括以下特征,设备或方面中的一个或多个。

102.进一步地,当结合实施例来描述该特定的特征、结构或特性时,可以认为结合其他实施例(无论是否明确描述)来实施这种特征、结构或特性是在本领域技术人员的知识范围内的。

103.已经描述了许多实施方式。然而,可以理解的是,可以对其进行各种修改。例如,不同实施方式的元素可以被组合、补充、修改、或移除,以产生其他实施方式。另外,本领域普通技术人员可以理解的是,可以用其他结构和过程代替所公开的结构和过程,并且所得到的实施方式将以至少基本上相同的方法执行至少基本上相同的功能,以至少实现与所公开的实施方式基本相同的结果。因此,本技术考虑了这些和其他实施方式。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1