压电式微机械超声换能器的制作方法

1.本公开涉及微机电系统(下文称为“mems”)的领域。特别地,本公开涉及一种压电式微机械超声换能器(下文称为“pmut”)。

背景技术:

2.mems器件包括借助微机械技术(例如,光刻、沉积、蚀刻、沉积、生长)在相同半导体材料基底(例如硅)中集成小型化机械、电气和/或电子部件。

3.微机械超声换能器器件(下文称为“mut器件”)是一种适于发射/接收超声波的mems器件。在已知的mut器件之间,压电mut器件(以下称为“pmut器件”)是已知的。pmut器件是一种mut器件,其操作基于与薄压电元件机械耦合的一个或多个薄膜元件的弯曲运动。

4.当pmut器件作为发射器操作时,在对压电元件施加ac电信号时,膜元件在压电元件的作用下在平衡位置周围弯曲和振荡。因此,膜元件的振荡会导致超声波的生成。

5.当pmut器件作为接收器操作时,超声波撞击膜元件会导致膜在其平衡位置周围振荡。膜元件的振荡作用在压电元件上,压电元件相应地生成ac电信号。

6.在超声波的生成和接收期间(即,在pmut器件作为发射器操作的情况下以及pmut器件作为接收器操作的情况下),膜元件以对应的共振频率在其平衡位置周围振荡。

7.为了在其平衡位置周围自由振荡,(一个或多个)膜元件相对于pmut器件的半导体基底悬置(例如,悬臂式)。

8.为此目的,在pmut器件的制造期间,已知形成锚定部分,该锚定部分适用于将pmut器件的(一个或多个)膜元件机械地连接到其半导体基底。

9.在设计阶段,pmut器件的共振频率是基于诸如膜元件的大小和材料的参数确定的。给定具体的材料的情况下,(一个或多个)膜元件的厚度是定义共振频率的最重要参数之一。

10.美国专利no.6,913,941公开了一种用于创建mems结构的方法。根据所述方法,提供了一种基底,具有布置在其上的牺牲层和布置在牺牲层之上的硅层。第一沟槽被创建,其延伸穿过二氧化硅层和牺牲层,并且第一沟槽将牺牲层分隔成由第一沟槽包围的第一区域以及在第一沟槽外部的第二区域。将第一材料沉积到第一沟槽中,使得第一材料填充第一沟槽的深度至少等于牺牲层的厚度。在第一沟槽的外部形成第二沟槽,第二沟槽至少延伸穿过硅层并且暴露牺牲层的第二区域的至少部分。牺牲层的第二区域通过第二沟槽与适用于蚀刻牺牲层的化学蚀刻溶液接触,蚀刻溶液对第一材料具有选择性。

技术实现要素:

11.申请人已经发现用于制造mems器件(诸如pmut器件)的已知解决方案不是特别有效。

12.根据已知解决方案制造的pmut器件受到膜厚度控制精度降低的负面影响。使用已知的制造方法,不可以以足够的精度控制膜的厚度,从而导致从相同半导体材料晶片获得

的pmut器件之间的谐振频率的不可忽略的扩展。

13.如上所述,申请人设计了一种用于改善制造pmut器件的工艺的解决方案。

14.本公开的一方面涉及一种用于制造pmut器件的方法,该pmut器件包括位于膜元件处的压电元件。该方法包括提供绝缘体上硅基底,绝缘体上硅基底包括第一硅层、氧化物层和第二硅层。

15.根据本公开的实施例,第一硅层沿着第一方向在氧化物层上堆叠,并且氧化物层沿着所述第一方向在第二硅层上堆叠。

16.根据本公开的实施例,方法进一步包括移除所述第一硅层的暴露侧部分以及氧化物层的对应的部分,以暴露先前由所述氧化物层覆盖的第二硅层的第一表面的部分,以及限定包括第一硅层和氧化物层的剩余部分的中心部分。

17.根据本公开的实施例,方法进一步包括在第二硅层的第一表面的暴露部分处形成用于所述膜元件的锚定部分。

18.根据本公开的实施例,方法进一步包括沿着所述第一方向在所述中心部分上方形成所述压电元件。

19.根据本公开的实施例,方法进一步包括选择性地移除所述第二层,以及从第一硅层的剩余部分下方移除所述氧化物的剩余部分,以限定所述膜元件。

20.根据本公开的实施例,所述膜元件包括第一硅层的剩余部分。

21.根据本公开的实施例,第一硅层沿着第一方向的厚度对应于膜元件沿着第一方向的厚度。

22.根据本公开的实施例,第一硅层沿着第一方向的厚度小于膜元件沿着第一方向的厚度。

23.根据本公开的实施例,方法进一步包括在形成所述压电元件之前,在第一硅层的所述剩余部分上生长硅,直到第一硅层的剩余部分的厚度达到所述膜元件的所述厚度为止。

24.根据本公开的实施例,在第一硅层的所述剩余部分上的所述生长硅包括使用外延技术生长硅。

25.根据本公开的实施例,所述形成锚定部分包括:在第二硅层的第一表面的所述暴露部分上生长硅。

26.根据本公开的实施例,在第二硅层的第一表面的所述暴露部分上的所述生长硅包括使用外延技术生长硅。

27.根据本公开的实施例,方法进一步包括执行平滑过程,旨在从生长的单晶硅获得由单晶硅制成的基本平坦的顶表面,所述平滑过程使用以下至少一项来执行:

28.化学机械抛光技术,以及

29.高温氢退火技术。

30.根据本公开的实施例,方法进一步包括,在形成所述压电元件之后并且在移除所述氧化物的剩余部分之前,选择性地移除第一硅层的剩余部分,直到到达氧化物的所述剩余部分为止。

31.根据本公开的实施例,所述第一硅层、所述第二硅层和所述锚定部分由单晶硅制成。

32.本公开的另一方面涉及pmut器件。

33.根据本公开的实施例,pmut器件包括硅基底。

34.根据本公开的实施例,pmut器件包括膜元件,适用于通过以对应的共振频率在平衡位置周围振荡来生成和接收超声波。

35.根据本公开的实施例,pmut器件包括用于将所述膜元件固定到硅基底的锚定部分。

36.根据本公开的实施例,pmut器件包括位于所述膜元件上的压电元件,被配置为:

37.当电信号被施加至压电元件时,使膜元件振荡,以及

38.响应于膜元件的振荡生成电信号。

39.根据本公开的实施例,膜元件和锚定部分由单晶硅制成。

40.本公开的另一方面涉及包括至少一个或多个pmut器件的电子系统。

附图说明

41.通过阅读以下仅通过非限制性示例提供的对其实施例进行的详细描述(将结合附图阅读),将更好地理解根据本公开的解决方案的这些和其他特征及优点。在这方面,明确指出是,附图不必按比例绘制(其一些细节可以被放大和/或简化),并且除非另有说明,否则它们仅用于概念性地说明所描述的结构和过程。特别地:

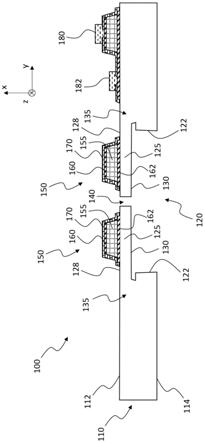

42.图1示意性地示出了根据本公开的实施例的pmut器件的横截面图;

43.图2a至图2k示出了根据本公开的第一实施例的用于制造图1的pmut器件的方法的主要步骤;

44.图3a至图3f示出了根据本公开的第二实施例的用于制造图1的pmut器件的方法的主要步骤,以及

45.图4以简化框的形式示出了包括至少一个图1的pmut器件的电子系统。

具体实施方式

46.图1示意性地示出了根据本公开的实施例的pmut器件的横截面视图,该pmut器件以附图标记100全局标识。

47.在本说明书的下文中,方向术语(诸如,顶部、底部、高处、低处、侧面、中心纵向、横向、竖直)将仅用于相对于图中所示的非常具体的方向来描述pmut器件100,而不用于描述pmut器件100在其操作期间将具有的可能的具体的方向。

48.在这方面,示出了包括三个正交方向x、y、z的参考方向系统。

49.根据本公开的实施例,pmut器件100具有圆形(或基本圆形)的形状(沿着平行于方向y和z的平面)。根据本公开的其他实施例,pmut器件100具有不同的形状,例如正方形(或基本正方形)的形状、矩形(或基本矩形)的形状、三角形(或基本三角形)的形状、六角形(或基本六角形)的形状或八角形(或基本八角形)的形状。

50.根据本公开的实施例,pmut器件100包括半导体基底110,集成pmut器件100本身的其他部件。根据本公开的实施例,半导体基底110是单晶硅基底,下文简称为硅基底110。图1中所示的pmut器件100的硅基底110具有前操作表面112和相对(沿着方向x)的后操作表面114。前操作表面112和后操作表面114平行于方向y和z延伸。

51.根据本公开的实施例,硅基底110包括从后操作表面114沿着方向x向前操作表面112延伸(但是没有到达前操作表面112)的凹部120。

52.根据本公开的实施例,凹部120在硅基底110中限定了由基本沿着方向x延伸的侧壁122界定的中空空间。类似的考虑也适用于侧壁122相对于方向x倾斜的情况。

53.根据本公开的实施例,pmut器件100包括膜元件125,适用于通过以对应的共振频率在平衡位置周围振荡来生成和接收超声波。根据本公开的实施例,膜元件125具有沿着平行于方向y和z的平面延伸的顶表面128和底表面130。

54.根据本公开的实施例,膜元件125具有圆形(或基本上圆形)的形状(沿着平行于方向y和z的平面)。根据本公开的其他实施例,膜元件125具有不同的形状,例如正方形(或基本方形)的形状、矩形(或基本矩形)的形状、三角形(或基本三角形)的形状、六角形(或基本六角形)的形状或八角形(或基本八角形)的形状。

55.根据本公开的实施例,膜元件125的底表面130对应于由凹部120限定的中空空间的顶表面。

56.根据本公开的实施例,膜元件125的顶表面128与硅基底110的前操作表面112平齐。

57.根据本公开的实施例,膜元件125由与硅基底110相同的材料(即,硅,特别是单晶硅)制成。

58.根据本公开的实施例,膜元件125的厚度(沿着方向x)在1μm至2.5μm的范围内,在一些实施例中,在1.5μm至2μm之间。

59.根据本公开的实施例,膜元件125借助于由与硅基底110相同的材料(即,硅,特别是单晶硅)制成的锚定部分135连接(即,固定)到硅基底110。锚定部分135位于凹部120的侧壁122与膜元件125的底表面130之间的交叉部处的硅基底110的部分中。

60.根据本公开的实施例,在膜元件125的中心部分中提供有通气孔140,用于在膜元件125振荡时允许空气排出。

61.根据本公开的实施例,pmut器件100包括压电元件150,压电元件150位于膜元件125的顶表面128上。根据本公开的实施例,压电元件150具有圆形(或基本圆形)的形状(沿着平行于方向y和z的平面),并且包围通气孔140。根据本公开的其他实施例,压电元件150具有不同的形状,例如正方形(或基本正方形)的形状、矩形(或基本矩形)的形状、三角形(或基本三角形)的形状、六边形(或基本六边形)的形状或八角形(或基本八角形)的形状。

62.根据本公开的实施例,压电元件150包括在由导电材料(诸如钼)制成的第一层160与第二层162之间的一层压电材料155(例如,包括氮化铝)。第一层160与第二层162形成压电元件150的电极,其上:

63.电信号可以被应用以引起膜元件125的振荡(当pmut器件100作为发射器操作时),以及

64.电信号可以响应于膜元件125的振荡而被生成(当pmut器件100作为接收器操作时)。

65.根据本公开的实施例,压电元件150覆盖有钝化层170(例如,包括氮化铝)。

66.根据本公开的实施例,为了访问pmut器件100以向其应用输入电信号以及从其读取电信号,提供接触元件180以电接触导电材料的第一层160,并且提供接触元件182以电接

触导电材料的第二层162。根据本公开的实施例,接触元件180、182由高导电材料(诸如金、铝或铝铜)制成。

67.图2a至图2k示出了根据本公开的第一实施例的用于制造图1的pmut器件100的方法的主要步骤。

68.参考图2a,根据本公开的实施例的制造工艺开始于提供绝缘体上硅基底200作为起始基底,该绝缘体上硅基底200包括沿着方向x在彼此的顶部堆叠的层。从顶部开始,然后沿着方向x向底部继续,绝缘体上硅基底200包括有源层(下文称为器件层202)、埋置氧化物层(下文称为箱层204)、支撑层(下文称为处理层206)和背氧化物层208。器件层202和处理层206由单晶硅制成,而箱层204和背氧化物层208由电绝缘二氧化硅制成。

69.根据本公开的该实施例,选择沿着方向x的器件层202的厚度,以对应于(例如基本上等于)pmut器件100的膜元件125的所需的厚度(参见图1),诸如1.5μm。

70.根据本公开的示例性实施例,箱层204具有沿着方向x的厚度,该厚度小于器件层202的厚度,诸如0.5μm。

71.根据本公开的示例性实施例,处理层206沿着方向x的厚度可以在1000μm至400μm的范围内,并且在一些实施例中为725μm。

72.根据图2b中所示的本公开的实施例,制造工艺的下一阶段包括例如借助低压化学气相沉积(使用正硅酸乙酯作为前体的lpcvd)或借助热氧化技术,在器件层202的暴露表面上沉积氧化物层210。

73.根据图2c中所示的本公开的实施例,制造工艺的下一阶段包括通过湿蚀刻或干蚀刻(基于所使用的氧化物厚度)移除以下层的侧部分:氧化物层210、器件层202、以及箱层204,以这种方式留下器件层202的中心部分212(在氧化物层210与箱层204的对应的部分之间),同时横向暴露底部处理层206的部分。

74.如将在下文中更好理解的,未被移除的器件层202的所述中心部分212将形成成品pmut器件100的膜元件125(参见图1)。

75.如图2d中所示,根据本公开的实施例,制造工艺的以下阶段提供了通过外延生长工艺而从处理层206的横向暴露部分以及从覆盖器件层202的中心部分212的氧化物层210生长硅。以这种方式,单晶硅部分214在处理层206的横向暴露部分的上方形成,并且多晶层216在覆盖器件层202的中心部分212的氧化物层210的上方形成。

76.如将在下文中更好地理解的,部分单晶硅部分214将形成将膜元件125连接到成品pmut器件100的硅基底110的锚定部分135(参见图1)。

77.根据图2e中所示的本公开的实施例,制造工艺的下一阶段提供执行蚀刻和平面化过程,旨在完全移除多晶硅层216以暴露下方氧化物层210并且移除单晶硅部分214的上部。例如,可以使用化学机械抛光(cmp)技术来执行平面化。

78.如图2f中所示,根据本公开的实施例,制造工艺的以下阶段提供例如借助蚀刻过程移除暴露的氧化物层210,以便获得由单晶硅制成的基本平坦的顶表面,如附图标记220所标识。

79.如将在下文中更好理解的,表面220的横向部分将对应于成品pmut器件100的硅基底110的前操作表面112,而表面220的中心部分将对应于悬臂式膜元件125的顶表面128(参见图1)。

80.根据图2g中所示的本公开的实施例,制造工艺的下一阶段提供在表面220上沉积第一层导电材料230(诸如钼),在第一层导电材料200上沉积一层压电材料232(诸如,包括氮化铝),然后在压电材料232层上沉积第二层导电材料234(诸如钼)。

81.根据图2h中所示的本公开的实施例,制造工艺的下一阶段提供(例如,通过蚀刻)移除层230、232、234的堆叠的图案部分,直到暴露下方表面220的区域为止,以便限定压电元件150(参见图1)。如已经参考图1所述,所得到的压电元件150包括压电材料层155(从层232获得),位于由导电材料161、162制成的两层(分别从层230和234获得)之间,形成压电元件150的电极。

82.根据本公开的实施例,该阶段进一步提供利用钝化层170(诸如包括氮化铝)覆盖压电元件150(参见图1),并且移除背氧化物层208,以便暴露处理层206的底表面238。

83.在不提供与本公开的理解无关、并且本领域技术人员熟知的细节的情况下,形成接触元件180以电接触导电材料的第一层160,并且形成接触元件182以电接触导电材料的第二层162。根据本公开的实施例,接触元件180、182由高导电材料(诸如金、铝或铝铜)制成。

84.根据图2i中所示的本公开的实施例,制造工艺的下一阶段提供在器件层202的中心部分212中创建开口240,直到暴露下方箱层204为止。根据本公开的实施例,通过应用沟槽掩模然后通过执行硅干蚀刻过程来获得开口240。

85.如将在下文中更好理解的,开口240将限定在成品pmut器件100的膜元件125的中心部分中提供的通气孔140(参见图1)。

86.如图2j中所示,根据本公开的实施例的制造工艺的以下阶段提供了执行背侧研磨操作,旨在从底表面238移除处理层206的部分,以使处理层206本身沿着方向x的厚度位于期望值处,诸如在300μm至400μm的范围内,例如350μm。一旦处理层206达到所需的厚度,处理层206的暴露的底表面对应于完成的pmut器件100的半导体基底110的后操作表面114(参见图1)。

87.根据图2k中所示的本公开的实施例,制造工艺的下一阶段提供了通过硅干蚀刻过程从背操作表面114沿着方向x生成凹部120(参见图1)。

88.一旦已经(例如通过应用氢氟酸)移除箱层204的剩余部分,则获得pmut器件100(参见图1)。

89.根据图2a至图2k中所示的本公开的实施例,使用单晶硅器件层202的中心部分212形成成品pmut器件100的膜元件125,膜元件125通过锚定部分135连接到成品pmut器件100的硅基底100,锚定部分135从在处理层206的横向暴露部分之上外延生长的单晶硅部分214获得。

90.通过图2a至图2k中所示的制造工艺获得的pmut器件100具有以下优点。

91.膜元件125和锚定部分135二者都在相同的材料(即,单晶硅)中形成。

92.由于锚定部分135已经通过同质外延生长工艺形成,其中锚定部分135的单晶硅从处理层206的单晶硅部分生长,因此硅基底不承受机械应力,因此改善了pmut器件100的机械和电气性能。不同地,已知的解决方案提供通过沉积二氧化硅层然后进行选择性蚀刻或通过将多晶硅沉积到在基底中实现的沟槽中来形成锚定部分,因此在形成锚定部分期间在半导体基底上引起不可忽略的应力(并且因此对器件本身的可靠性和效率产生负面影响)。

93.此外,由于图2a至图2k中所示的制造工艺从绝缘体上硅基底200开始,绝缘体上硅基底200具有沿着方向x的厚度(该厚度已经对应于膜元件125的所需的厚度)的器件层202,因此在完成的pmut器件100中得到的膜元件125的厚度非常精确,并且较少受到工艺失配的影响。因此,pmut器件100的谐振频率更精确。

94.本解决方案的其它优点是,所提出的制造工艺不需要在其末端进行修整,并且不需要双电晶片排序(在生产线上对成品膜进行修整和/或器件钝化仍然是可能的)。

95.图3a至图3f示出了根据本公开的第二实施例的用于制造图1的pmut器件100的方法的一些主要步骤。

96.参考图3a,根据本公开的该实施例的制造工艺通过提供绝缘体上硅基底300作为起始基底开始,该绝缘体上硅基底300沿着方向x从顶部向底部相继包括:单晶硅器件层302、二氧化硅箱层304、处理层306以及二氧化硅背氧化物层308。

97.与本公开的先前实施例(对应于图2a至图2k)不同,根据本公开的该实施例,沿着方向x的器件层302的厚度低于pmut器件100的膜元件125的期望厚度(参见图1)。例如,器件层302的厚度可以小于1.5μm。

98.根据本公开的示例性实施例,箱层304具有沿着方向x的厚度,该厚度小于器件层302的厚度,例如小于0.5μm。

99.根据本公开的示例性实施例,处理层306沿着方向x的厚度可以在1000μm至400μm的范围内,并且在一些实施例中,在650μm至750μm之间。

100.根据图3b中所示的本公开的实施例,制造工艺的下一阶段包括例如借助氧化工艺或低压化学气相沉积,在器件层302的暴露表面上生长氧化物层310。

101.根据图3c中所示的本公开的实施例,制造工艺的下一阶段包括通过湿蚀刻或干蚀刻移除以下层的侧部:氧化物层310、器件层302、以及箱层304,以这种方式留下器件层302的中心部分312(在氧化物层310和箱层304的对应的部分之间),同时横向暴露下方处理层306的部分。

102.与本公开的先前的实施例不同(对应于图2a至图2k),未被移除的器件层302的中心部分312不能直接用于形成完成的pmut器件100的膜元件125(参见图1),这是因为其厚度不同于(即,低于)膜元件125所需的厚度。

103.如图3d中所示,根据本公开的实施例的制造工艺的下一阶段提供了通过选择性外延生长工艺,从处理层306的横向暴露部分生长硅。根据本公开的实施例,选择性外延生长工艺被配置为以这种方式生长:仅从处理层306的横向暴露部分生长硅,从而防止在氧化物层310上的任何硅生长。例如,选择性外延生长工艺可以利用硅烷或二氯硅烷作为硅前驱体并且利用盐酸作为选择剂(根据文献中报道的已知方法)。这样,单晶硅部分314仅形成在处理层306的横向暴露部分的上方。

104.根据本公开的实施例,继续选择性外延生长过程,直到生长的单晶硅部分314与氧化物层310基本平齐为止。

105.由于取决于工艺温度和气体分压,在选择性外延生长过程中不可避免地移除了氧化物层310的一小部分,因此应以足够大的厚度生成氧化物层310,以避免氧化物层310在该阶段器件被完全移除。例如,对于使用800℃至1100℃温度范围的选择性外延生长工艺,在一些实施例中,氧化物层310的厚度应该设置在0.1μm至1μm的范围内。

106.根据在图3e中所示的本公开的实施例,制造工艺的下一阶段包括移除氧化物层310以暴露器件层302的中心部分312,然后通过外延生长工艺在单晶硅部分314和现在暴露的单晶硅中心部分312上生长单晶硅。执行外延生长过程,直到单晶中心部分312(沿着方向x)的厚度达到完成的pmut器件100的膜元件125的所需的厚度(参见图1)为止。

107.根据图3f中所示的本公开的实施例,制造工艺的下一阶段提供了执行平滑过程,旨在从生长的单晶硅获得由单晶硅制成的基本平坦的顶表面(在附图中由附图标记320标识)。根据本公开的示例性实施例,使用化学机械抛光(cmp)技术和/或高温氢退火技术来执行所述平滑过程。

108.根据本公开的实施例,(加厚的)单晶中心部分312将形成成品pmut器件100的膜元件125(参见图1)。

109.根据本公开的实施例,(加厚的)单晶硅部分314的部分将形成锚定部分135,锚定部分135将膜元件125连接到成品pmut器件100的硅基底110(参见图1)。

110.根据本公开的实施例,表面320的侧面横向部分将对应于成品pmut器件100的硅基底110的前操作表面112,而表面320的中心部分将对应于悬臂式膜元件125的顶表面128(参见图1)。

111.从现在起,制造工艺将以与图2a至图2k中所示的本公开的实施例中相同的方式进行,因此为了简洁起见,将不提供细节。

112.简而言之,形成了压电元件150和接触元件180、182。然后,打开用于限定通气孔140的开口,并且执行用于移除处理层306的部分的背面研磨操作。此时,生成凹部120,移除箱层304的剩余部分,并且获得pmut器件100(参见图1)。

113.根据图3a至图3f中所示的本公开的实施例,成品pmut器件100的膜元件125已经通过在单晶硅器件层302的中心部分312上外延生长单晶硅形成,膜元件通过锚定部分135连接到成品pmut器件100的硅基底100,锚定部分135从在处理层306的横向暴露部分上方外延生长单晶硅部分314获得。

114.利用图3a至图3f中所示的制造工艺获得的pmut器件100具有以下优点。

115.膜元件125和锚定部分135二者都在相同的材料(即,单晶硅)中形成。

116.由于锚定部分135已经通过同质外延生长工艺形成,其中锚定部分135的单晶硅从处理层306的单晶硅部分生长,因此硅基底不经受机械应力,从而改善了pmut器件100的机械和电气性能。

117.此外,在图3a至图3f中所示的制造工艺始于绝缘体上硅基底300,具有沿着方向x的厚度小于膜元件125的所需厚度的器件层302,并且在完成的pmut器件100中通过外延生长达到所得到的膜元件125的厚度。因此,由于工艺失配导致的可能扩散被强力地减少,这是因为工艺失配只与膜元件的(相对较小的)外延生长部分有关。因此,在这种情况下,pmut器件100的谐振频率也更精确。

118.图4以简化块的形式示出了电子系统400(或其一部分),包括根据上述公开的实施例制造的至少一个pmut器件100。

119.根据本公开的实施例,电子系统400适用于在电子器件中使用,诸如个人数字助理、计算机、平板计算机和智能电话。

120.根据本公开的实施例,除了pmut器件100之外,电子系统400还可以包括控制器

405,诸如一个或多个微处理器和/或一个或多个微控制器。

121.根据本公开的实施例,除了pmut器件100之外,电子系统400还可以包括用于生成/接收消息/命令/数据和/或用于接收/发送数字和/或模拟信号的输入/输出器件410(诸如键盘和/或触摸屏和/或可视显示器)。

122.根据本公开的实施例,除了pmut器件100之外,电子系统400还可以包括用于例如利用射频信号与无线通信网络(未示出)交换消息的无线接口415。无线接口415的示例可以包括天线和无线收发器。

123.根据本公开的实施例,除了pmut器件100之外,电子系统400还可以包括存储器件420,诸如易失性和/或非易失性存储器器件。

124.根据本公开的实施例,除了pmut器件100之外,电子系统400还可以包括用于向电子系统400供电的供电器件,例如电池425。

125.根据本公开的实施例,电子系统400可以包括一个或多个通信通道(总线),用于允许在pmut器件100与控制器405、和/或输入/输出器件410、和/或无线接口415、和/或存储器件420和/或电池425之间的数据交换(当它们存在时)。

126.自然地,为了满足本地和具体要求,本领域技术人员可以对上述解决方案应用许多逻辑和/或物理修改和改变。更具体地说,尽管已经参考本公开的优选实施例以一定程度的特殊性描述了本公开,但是应当理解,在形式和细节以及其他实施例中的各种省略、替换和改变是可能的。特别地,本公开的不同实施例甚至可以在没有前述说明书中阐述的具体细节的情况下实现,以提供对其更透彻的理解;相反,可以省略或简化众所周知的特征,以便不必要的细节不会妨碍说明书。此外,明确的意图是,结合本公开的任何公开实施例所描述的具体元件和/或方法步骤可以并入其他实施例中。

127.可以组合上述各种实施例以提供进一步的实施例。根据上述详细描述,可以对实施例进行这些和其他改变。通常,在以下权利要求中,所使用的术语不应该被解释为将权利要求限制于说明书和权利要求中公开的具体实施例,而应该被解释为包括所有可能的实施例以及这些权利要求有权获得的等效物的全部范围。因此,权利要求不受本公开的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1