芯片托盘套件及芯片测试设备的制作方法

1.本发明涉及一种芯片托盘套件及芯片测试设备,尤其涉及一种适合用以对芯片进行高频测试的芯片托盘套件及芯片测试设备。

背景技术:

2.现有常见的ic芯片测试设备,特别是用来对ic芯片进行高频测试的测试设备,在安装ic芯片的过程中,可能因为各种因素,而发生部分ic芯片没有正确地与测试设备的相关探针电性连接,借此,未正确安装的ic芯片将无法正确地被测试。

3.由于现有的ic芯片测试设备,将ic芯片安装于测试设备中后,基本上不会再次检查ic芯片是否已经正确地安装于测试设备中,因此,相关人员往往要等到整批ic芯片完成测试后,才会发现部分的ic芯片因为没有正确地被安装而没有正确地被检测。

4.另外,现有用来承载多个ic芯片的料盘,在被相关设备移载的过程中,容易因为各种因素脱离料盘,为此造成相关人员的困扰。

技术实现要素:

5.本发明公开一种芯片托盘套件及芯片测试设备,主要用以改善现有的ic芯片测试设备,容易发生ic芯片未正确地安装于测试设备中,而导致该ic芯片没有被正确地进行检测的问题。

6.本发明的其中一个实施例公开一种芯片托盘套件,其包含:一托盘,其具有多个托盘穿孔,各个托盘穿孔贯穿托盘设置;多个芯片固定件,其可拆卸地固定于托盘,且各个芯片固定件位于各个托盘穿孔中;各个芯片固定件包含多个固定穿孔、多个容置凹槽及多个芯片容槽,各个固定穿孔贯穿芯片固定件设置,各个容置凹槽、各个芯片容槽及各个固定穿孔相互连通,各个芯片容槽用以容置一个芯片,各个芯片固定件于各个芯片容槽中还形成有至少一个限位结构,限位结构用以限制设置于芯片容槽中的芯片相对于芯片固定件的活动范围;多个辅助插入件,其可拆卸地固定设置于多个芯片固定件的一侧,各个辅助插入件包含:一本体、多个凸出部及多个插入穿孔,多个凸出部由本体的一侧向外凸出形成,各个插入穿孔贯穿本体及一个凸出部;各个凸出部的外径小于各个容置凹槽的孔径,且各个凸出部的外径大于各个芯片容槽的孔径,而各个插入穿孔的孔径小于各个芯片容槽的孔径;其中,各个辅助插入件固定设置于芯片固定件的一侧时,各个凸出部对应位于容置凹槽中,且各个凸出部与设置于芯片容槽中的芯片之间形成有一间隙;其中,芯片托盘套件用以固定设置于一测试机台,而芯片托盘套件所承载的多个芯片则能与测试机台电性连接,测试机台则能对多个芯片进行测试;各个插入穿孔用以提供一个抵压件穿设,穿过插入穿孔的抵压件的一部分是用来抵压设置于芯片容槽中的芯片的表面,以使各个芯片能与测试机台稳定地相连接。

7.优选地,芯片托盘套件还包含多个辅助固定件,各个辅助固定件可拆卸地固定设置于托盘,且个托盘穿孔的周围设置有多个辅助固定件,多个辅助固定件用以限制位于多

个托盘穿孔中的芯片固定件相对于托盘的活动范围。

8.优选地,芯片托盘套件还包含多个弹性件,各个芯片固定件与形成各个托盘穿孔的侧壁之间设置有多个弹性件。

9.优选地,芯片托盘套件还包含多个快拆组件,各个辅助插入件能通过至少一组快拆组件可拆卸地与各个芯片固定件相互连接。

10.优选地,各个芯片固定件具有至少一凹槽,各个凹槽用以设置一组快拆组件,设置于凹槽中的快拆组件包含:两个限位件及两个弹性件,各个弹性件的一端固定于形成凹槽的侧壁,各个弹性件的另一端与一个限位件相互固定,两个限位件彼此间形成有一间隙;各个辅助插入件的一侧设置有至少两个卡合件;各个辅助插入件的两个卡合件能与各个芯片固定件的两个限位件相互卡合。

11.优选地,各个辅助插入件具有至少一穿孔,各个辅助插入件固定设置于各个芯片固定件的一侧时,穿孔与间隙相互连通;各个间隙用以提供一推杆通过,通过穿孔的推杆能推抵两个限位件,据以使两个限位件不再与两个卡合件相互卡合。

12.优选地,各个限位件具有一卡槽,各个限位件被卡槽区隔为一推抵部及一卡合部,卡合部具有一卡合斜面;各个卡合件具有一卡合斜面;当各个卡合件的卡合斜面与各个限位件的卡合斜面相互接触时,各个卡合件相对于限位件的活动范围将被限制。

13.本发明的其中一个实施例公开一种芯片测试设备,其包含:一芯片托盘套件,其包含:一托盘,其具有多个托盘穿孔,各个托盘穿孔贯穿托盘设置;多个芯片固定件,其可拆卸地固定于托盘,且各个芯片固定件位于各个托盘穿孔中;各个芯片固定件包含多个固定穿孔、多个容置凹槽及多个芯片容槽,各个固定穿孔贯穿芯片固定件设置,各个容置凹槽、各个芯片容槽及各个固定穿孔相互连通,各个芯片容槽用以容置一个芯片,各个芯片固定件于各个芯片容槽中还形成有至少一个限位结构,限位结构用以限制设置于芯片容槽中的芯片相对于芯片固定件的活动范围;多个辅助插入件,其可拆卸地固定设置于多个芯片固定件的一侧,各个辅助插入件包含:一本体、多个凸出部及多个插入穿孔,多个凸出部由本体的一侧向外凸出形成,各个插入穿孔贯穿本体及一个凸出部;各个凸出部的外径小于各个容置凹槽的孔径,且各个凸出部的外径大于各个芯片容槽的孔径,而各个插入穿孔的孔径小于各个芯片容槽的孔径;其中,各个辅助插入件固定设置于芯片固定件的一侧时,各个凸出部对应位于容置凹槽中,且各个凸出部与设置于芯片容槽中的芯片之间形成有一间隙;其中,芯片托盘套件用以固定设置于一测试机台,而芯片托盘套件所承载的多个芯片则能与测试机台电性连接,测试机台则能对多个芯片进行测试;各个插入穿孔用以提供一个抵压件穿设,穿过插入穿孔的抵压件的一部分是用来抵压设置于芯片容槽中的芯片的表面,以使各个芯片能与测试机台稳定地相连接;一盖体,其一侧内凹形成有一容槽,盖体用以盖设于托盘的一侧;多个抵压组件,其设置于盖体,且各个抵压组件位于盖体的容槽中,多个抵压组件用以抵压芯片托盘套件的多个芯片固定件所承载的多个芯片;一测试机台,其用以与芯片托盘套件相连接,测试机台用以与芯片托盘套件所承载的多个芯片电性连接,且测试机台用以对设置于多个芯片容槽中的多个芯片进行测试;一温度调节装置,其与多个抵压组件相连接,温度调节装置用以使各个抵压件的温度到达一预定温度。

14.优选地,各个抵压组件包含:一底座,其用以固定设置于盖体;一抵压件,其包含一接触部,接触部具有一接触面,接触部的一部分能伸入其中一个固定穿孔,而接触面用以抵

压设置于其中一个芯片容槽中的芯片的一表面;至少一弹性件,其两端固定于底座及抵压件;当抵压件抵压芯片的表面时,弹性件将弹性变形,且抵压件不再抵压芯片的表面时,弹性件受压产生的弹性回复力,将使抵压件回复至未抵压芯片的状态。

15.优选地,盖体盖设于托盘的一侧时,盖体、托盘、多个芯片固定件及多个芯片共同形成一封闭空间;芯片测试设备还包含一抽真空装置,抽真空装置用以抽取封闭空间内的空气,以使封闭空间呈负压状态。

16.优选地,盖体包含一本体及一传导结构,温度调节装置与传导结构相连接,温度调节装置用以使传导结构的温度上升或下降,各个底座可拆卸地固定于传导结构,传导结构能通过多个底座及多个弹性件,而与多个抵压件相互传递热能,以使各个抵压件的温度到达预定温度。

17.优选地,各个抵压组件还包含一导热件,导热件与抵压件相连接,且导热件与底座相连接,而导热件位于抵压件与底座之间,导热件用以辅助抵压件与底座彼此间的热能相互传递。

18.优选地,各个抵压件还包含一抵靠部,各个抵压组件还包含至少一固定结构及至少一限位件,固定结构固定于底座,限位件可拆卸地与固定结构相互固定,限位件的一部分用以抵靠于抵压件的抵靠部,而限位件及固定结构能共同限制抵压件相对于底座的活动范围;各个限位件包含一容置缺口,容置缺口用以容置接触部的一部分。

19.优选地,盖体盖设于托盘的一侧时,盖体、托盘、多个芯片固定件、多个辅助插入件及多个芯片共同形成一封闭空间;芯片测试设备还包含一抽真空装置,抽真空装置用以抽取封闭空间内的空气,以使封闭空间呈负压状态。

20.优选地,芯片托盘套件还包含多个辅助固定件,各个辅助固定件可拆卸地固定设置于托盘,且个托盘穿孔的周围设置有多个辅助固定件,多个辅助固定件用以限制位于多个托盘穿孔中的芯片固定件相对于托盘的活动范围。

21.优选地,芯片托盘套件还包含多个弹性件,各个芯片固定件与形成各个托盘穿孔的侧壁之间设置有多个弹性件。

22.优选地,芯片托盘套件还包含多个快拆组件,各个辅助插入件能通过至少一组快拆组件可拆卸地与各个芯片固定件相互连接。

23.优选地,各个芯片固定件具有至少一凹槽,各个凹槽用以设置一组快拆组件,设置于凹槽中的快拆组件包含:两个限位件及两个弹性件,各个弹性件的一端固定于形成凹槽的侧壁,各个弹性件的另一端与一个限位件相互固定,两个限位件彼此间形成有一间隙;各个辅助插入件的一侧设置有至少两个卡合件;各个辅助插入件的两个卡合件能与各个芯片固定件的两个限位件相互卡合。

24.优选地,各个辅助插入件具有至少一穿孔,各个辅助插入件固定设置于各个芯片固定件的一侧时,穿孔与间隙相互连通;各个间隙用以提供一推杆通过,通过穿孔的推杆能推抵两个限位件,据以使两个限位件不再与两个卡合件相互卡合。

25.优选地,各个限位件具有一卡槽,各个限位件被卡槽区隔为一推抵部及一卡合部,卡合部具有一卡合斜面;各个卡合件具有一卡合斜面;当各个卡合件的卡合斜面与各个限位件的卡合斜面相互接触时,各个卡合件相对于限位件的活动范围将被限制。

26.综上所述,本发明的芯片托盘套件及本发明的芯片测试设备所包含的芯片托盘套

件,主要是用来承载多个芯片,而通过辅助插入件的设置,设置于芯片固定件中的芯片,于芯片托盘套件被移载的过程中,将不容易离开芯片固定件。

附图说明

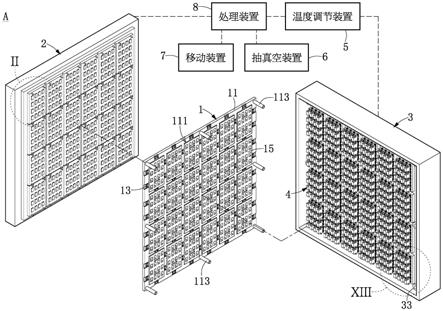

27.图1为本发明的芯片测试设备的示意图。

28.图2为图1的局部放大示意图。

29.图3及图4为本发明的芯片托盘套件的不同视角的局部放大示意图。

30.图5及图6为本发明的芯片托盘套件的不同视角的局部分解示意图。

31.图7为本发明的芯片托盘套件的局部剖面分解示意图。

32.图8为本发明的芯片托盘套件设置有芯片的局部剖面示意图。

33.图9为本发明的芯片托盘套件的局部分解示意图。

34.图10~图12为本发明的芯片托盘套件的辅助插入件与芯片固定件相互固定的作动示意图。

35.图13为图1的局部放大示意图。

36.图14为本发明的抵压组件的局部分解示意图。

37.图15为本发明的抵压组件的局部剖面示意图。

38.图16为本发明的盖体与芯片托盘套件相互分离的剖面示意图。

39.图17为本发明的盖体与芯片托盘套件相互组合的剖面示意图。

40.图18为图17的局部放大示意图。

41.图19为本发明的抵压组件的不同实施例的剖面示意图。

具体实施方式

42.于以下说明中,如有指出请参阅特定附图或是如特定附图所示,其仅是用以强调于后续说明中,所述及的相关内容大部分出现于该特定附图中,但不限制该后续说明中仅可参考所述特定附图。

43.请一并参阅图1至图8,本发明的芯片测试设备a用以对一芯片托盘套件1所承载的多个芯片c(如图8所示)进行测试。于指所指的芯片c可以是任何ic芯片、内存等。芯片测试设备a包含:一测试机台2、一盖体3、多个抵压组件4及一温度调节装置5。测试机台2及盖体3用以共同固持一芯片托盘套件1。

44.如图1及图2所示,测试机台2能与芯片托盘套件1相连接,且测试机台2用以与芯片托盘套件1所承载的多个芯片c(如图8所示)电性连接,并对多个芯片c进行测试,测试机台2对各个芯片c所进行的测试内容可以是依据实际芯片c的种类及需求进行设计,于此不加以限制。在实际应用中,测试机台2可以包含有一机台本体21、一控制模块22及多个探针座23,控制模块22设置于机台本体21,各个探针座23包含多个探针(图未示),而各个探针座23的多个探针用来与待测试的芯片c电性连接,控制模块22能执行相关的测试程序,以通过多个探针座23对多个待测试的芯片c(如图8所示)进行相关测试。在实际应用中,机台本体21可以是具有用来与芯片托盘套件1相互固定的结构或是机构(图未示),且机台本体21或是各个探针座23可以是具有用来辅助限制芯片c的结构或是机构(图未示),于此不加以限制。控制模块22例如可以是包含有电路板、微处理器、控制电路等。

45.如图1、图3至图8所示,芯片托盘套件1可以包含一托盘11及24个芯片固定件12。托盘11包含24个托盘穿孔111,各个托盘穿孔111贯穿托盘11。托盘11所具有的托盘穿孔111的数量、多个托盘穿孔111的外型、排列方式等,皆不以图中所示为限。芯片固定件12的数量是对应于托盘穿孔111的数量。各个芯片固定件12可拆卸地固定设置于托盘11,且各个芯片固定件12对应固定设置于所述托盘穿孔111中。

46.在实际应用中,芯片托盘套件1还可以是包含有多个辅助固定件13,一部分的辅助固定件13可拆卸地(例如是配合至少一个螺丝)固定设置于托盘11的其中一侧面,另一部分的辅助固定件13可拆卸地固定设置于托盘11的另一侧面。在本实施例的附图中,每一个芯片固定件12可以是通过10个辅助固定件13固定于托盘11,而托盘11彼此相反的两侧面是分别设置有4个辅助固定件13及6个辅助固定件13,通过10个辅助固定件13的设置,芯片固定件12将被固定设置于托盘穿孔111中。关于辅助固定件13的外型及单一个芯片固定件12是通过多少个辅助固定件13固定于托盘11,皆不以图中所示为限。

47.如图5至图8所示,各个芯片固定件12包含16个固定穿孔121、16个芯片容槽122及多个限位结构123。各个芯片固定件12所包含的固定穿孔121、芯片容槽122及限位结构123的数量,皆不以图中所示为限。各个固定穿孔121贯穿芯片固定件12设置,芯片容槽122与固定穿孔121相连通,且各个芯片容槽122用以承载一个待测试的芯片c,设置于芯片容槽122中的芯片c的多个电连接部(图未示,例如是各式接脚)外露于芯片固定件12,而多个电连接部则能与测试机台2的多个探针座23相连接,借此,测试机台2(如图1所示)则能与芯片c电性连接。

48.形成芯片容槽122的侧壁向芯片容槽122的方向延伸形成各个限位结构123,位于同一芯片容槽122中的限位结构123,用来共同限制位于芯片容槽122中的芯片c的活动范围,以限制设置于芯片容槽122中的芯片c离开芯片容槽122。于本实施例中,是以设置于芯片容槽122中的芯片c会被4个限位结构123限制为例,但关于限位结构123的数量、形成位置、外型等皆不以图中所示为限。当然限位结构123不能阻挡设置于芯片容槽122中的芯片c的电连接部与测试机台2的探针座23相连接。

49.如图7所示,在实际应用中,芯片固定件12内部还可以是包含有一导引结构124,导引结构124例如可以是向芯片容槽122的方向倾斜的斜面。通过导引结构124的设计,芯片c通过固定穿孔121而设置于芯片容槽122的过程中,即使芯片c的置放位置有些微偏差,芯片c仍会被导引结构124导正,而顺利地设置于芯片容槽122中。

50.依上所述,通过使芯片固定件12可拆卸地固定设置于托盘11的设计,使用者将可以依据待测试的芯片c的种类、外型、尺寸的不同,而选择性地更换具有不同外型、尺寸的芯片容槽122、固定穿孔121的芯片固定件12。

51.如图5及图6所示,在较佳的应用中,芯片托盘套件1还可以是包含有多个弹性件14,各个弹性件14的一端固定设置于形成各个托盘穿孔111的侧壁112的一第一容槽1121,而各个弹性件14的另一端则是对应设置于芯片固定件12的侧壁125的一第二容槽1251。在芯片固定件12的外型大致呈现为矩形的实施例中,芯片固定件12的每一个侧壁125与形成托盘穿孔111的侧壁125之间可以是设置有至少一个所述弹性件14。

52.当芯片固定件12固定设置于托盘穿孔111中时,多个弹性件14将是呈现为受压的状态,而各个弹性件14受压产生的弹性力将推抵芯片固定件12,如此,芯片固定件12将可以

稳固地设置于托盘穿孔111中。由于多个弹性件14是设置于芯片固定件12的侧壁125与形成托盘穿孔111的侧壁112之间,且多个辅助固定件13是固定于托盘11彼此相反的两个宽侧面,因此,当使用者将多个辅助固定件13由托盘11上卸下时,芯片固定件12会因为多个弹性件14的推抵,仍持续设置于托盘11上,如此,将可避免芯片固定件12在多个辅助固定件13被拆离托盘11时发生落地的问题。另外,通过多个弹性件14的设置,当芯片托盘套件1固定于测试机台2(如图1所示)的一侧时,芯片固定件12能相对于托盘11微幅地移动,借此,可以使芯片固定件12所承载的多个芯片c,可以更容易地与测试机台2的多个探针座23(如图2所示)相连接。

53.如图1、图5至图9所示,芯片托盘套件1还可以是包含有24个辅助插入件15。辅助插入件15的数量是对应于芯片固定件12的数量,且辅助插入件15的数量不以图中所示为限。各个辅助插入件15可拆卸地设置于各个芯片固定件12的一侧。

54.各个辅助插入件15包含一本体151及多个凸出部152,凸出部152由本体151的一侧向外凸出形成,凸出部152的数量是对应于各个芯片固定件12所具有的固定穿孔121的数量。芯片固定件12还可以是形成有多个容置凹槽126,各个容置凹槽126与各个芯片容槽122相连通,容置凹槽126的孔径w1大于芯片容槽122的孔径w2,而容置凹槽126用来容置辅助插入件15的凸出部152。

55.辅助插入件15具有一插入穿孔153,插入穿孔153贯穿本体151及凸出部152,插入穿孔153的孔径w3大于抵压件42的接触部421(如图18所示,于后详述)的外径w4,而接触部421的一部分能穿过插入穿孔153并露出于辅助插入件15的一侧(如图18所示)。插入穿孔153的孔径w3小于芯片容槽122的孔径w2。凸出部152的高度可以是大致等于容置凹槽126的深度,而凸出部152位于容置凹槽126中时,辅助插入件15的本体151是对应抵靠于芯片固定件12的顶面128(如图8所示)。

56.如图7及图8所示,为利使凸出部152能够快速且正确地进入固定穿孔121中,凸出部152还可以是包含有多个导引斜面1521,多个导引斜面1521用以使凸出部152更容易地进入固定穿孔121中。如图8所示,在实际应用中,当芯片容槽122设置有芯片c,且凸出部152位于容置凹槽126中时,凸出部152与芯片c的表面c1之间是形成有一间隙g,而凸出部152不会接触芯片c的表面c1。当芯片固定件12及辅助插入件15固定设置于托盘11时,设置于芯片固定件12的芯片容槽122中的芯片c,将同时被芯片固定件12及辅助插入件15共同限制,而各个芯片c基本上难以脱离芯片固定件12。

57.关于各个辅助插入件15可拆卸地设置于各个芯片固定件12的一侧的方式,于此不加以限制,任何可以使各个辅助插入件15可拆卸地设置于各个芯片固定件12的方式,皆属于本实施例可实施的范围。举例来说,在其中一个实施例中,各个辅助插入件15及各个芯片固定件12可以是一同设置于托盘11的托盘穿孔111中,而前述的多个辅助固定件13则可以是用来限制各个辅助插入件15及各个芯片固定件12相对于托盘11的活动范围,也就是说,各个辅助插入件15及各个芯片固定件12是通过多个辅助固定件13固定设置于托盘11的托盘穿孔111中。

58.承上,如图1、图5、图6、图9至图12所示,在其中一个较佳的实施例中,芯片托盘套件1还可以是包含多个快拆组件16,各个辅助插入件15及各个芯片固定件12之间设置有至少一个快拆组件16,而各个辅助插入件15能通过至少一个快拆组件16,快速地安装于芯片

固定件12的一侧,或是,快速地由芯片固定件12的一侧卸下。举例来说,各个芯片固定件12可以是设置有两个快拆组件16,各个快拆组件16可以是包含有:两个限位件161及两个弹性件162。芯片固定件12还可以是具有一凹槽127,两个弹性件162的一端固定设置于形成凹槽127的侧壁,各个弹性件162的另一端与其中一个限位件161相互固定,且各个快拆组件16的两个限位件161设置于其中一个凹槽127中。

59.各个限位件161能被推抵而于凹槽127中活动,并对应挤压其所连接的弹性件162,受挤压的弹性件162则能对应产生弹性回复力;当限位件161不再被推抵时,弹性件162受压所产生的弹性回复力将使限位件161恢复至未被推抵的位置。两个限位件161设置于凹槽127中时,两个限位件161之间是形成有一间隙p。

60.各个限位件161可以是具有一卡槽1611,各个卡槽1611将限位件161区隔为一推抵部16a及一卡合部16b,推抵部16a相反于弹性件162的一端形成有一导引斜面16a1,卡合部16b面对推抵部16a的一端形成有一卡合斜面16b1。

61.如图10所示,各个辅助插入件15可以是形成有一穿孔155,且各个辅助插入件15设置有两个卡合件154,两个卡合件154位于穿孔155的两端,各个卡合件154相反于穿孔155的一端形成有一卡合斜面1541。辅助插入件15的穿孔155用以提供一插入件r伸入。插入件r用来推抵设置于芯片固定件12的两个限位件161。在实际应用中,插入件r可以固定于用来将辅助插入件15固定于芯片固定件12上的相关机械手臂等设备上。

62.如图10至图11所示,辅助插入件15与插入件r相互配合,而固定于芯片固定件12的流程可以是:首先,插入件r穿过辅助插入件15的穿孔155,而进入两个限位件161之间形成的间隙p中,由于插入件r的外径大于间隙p的宽度,因此,插入件r进入凹槽127时,插入件r将推抵两个限位件161的推抵部16a,而各个限位件161将据以向弹性件162的方向移动,各个弹性件162则受压而弹性变形。

63.承上,如图11所示,当插入件r的末端抵靠于形成凹槽127的底部时,各个卡合件154将对应设置于各个限位件161的卡槽1611中,各个卡合件154的卡合斜面1541,则是与相邻的限位件161的卡合部16b的卡合斜面16b1彼此相面对地设置,且各卡合斜面1541与相邻的卡合斜面16b1未相互接触。接着,如图12所示,当插入件r被移出凹槽127时,位于凹槽127中的两个弹性件162受压所产生的弹性回复力,将使两个限位件161向彼此相互靠近的方向移动,最后,各个限位件161的卡合部16b的卡合斜面16b1,将与相邻的卡合件154的卡合斜面1541相互抵靠,而辅助插入件15则据以卡合固定于芯片固定件12。

64.如图12所示,在辅助插入件15通过卡合件154及快拆组件16,与芯片固定件12相互固定的情况下,相关机械手臂等机构,可以将插入件r穿过辅助插入件15的穿孔155,并进入两个限位件161之间的间隙p,以推抵两个限位件161,此时,两个限位件161将由图12的状态转变为图11的状态,在图11的状态下,各限位件161的卡合斜面16b1将不再与相邻的卡合件154的卡合斜面1541相接触,而相关机械手臂等机构,则可以固持辅助插入件15,并将辅助插入件15向远离芯片固定件12的方向拉出,而使辅助插入件15与芯片固定件12相互分离。

65.如图3及图5所示,值得一提的是,在各个辅助插入件15是通过快拆组件16固定于芯片固定件12的一侧的实施例中,各个辅助插入件15可以是形成有多个避让孔156,各个避让孔156是用以避开辅助固定件13,而使辅助固定件13不会限制辅助插入件15的活动范围。

66.请一并参阅图1、图13及图16,盖体3可以是具有一本体31及一传导结构32,本体31

的一侧内凹形成有一容槽311,传导结构32形成于本体31的一侧,且传导结构32位于容槽311中。多个抵压组件4设置于盖体3,且各个抵压组件4位于盖体3的容槽311中。需说明的是,于本实施例的图16中,是以多个抵压组件4凸出于盖体3的一端为例,但不以此为限,在不同的实施例中,多个抵压组件4也可以是不凸出于盖体3,而各个抵压组件4是完全位于盖体3的容槽311中。换句话说,传导结构32的厚度及各个抵压组件4的高度的总和,可以大于、等于或是小于盖体3的容槽311的深度。

67.盖体3用以盖设于托盘11的一侧。当盖体3盖设于托盘11的一侧时,设置于盖体3的多个抵压组件4将对应抵压设置于托盘11的芯片固定件12内的芯片c的表面c1(如图18所示)。在不同的实施例中,盖体3盖设于托盘11的一侧时,多个抵压组件4可以是未与多个芯片c相接触,直到盖体3与托盘11所共同形成的封闭空间被抽真空,多个抵压组件4才抵压于多个芯片c的表面c1。关于盖体3的尺寸、外型及盖体3的传导结构32设置的抵压组件4的数量,皆不以图中所示为限。

68.在实际应用中,盖体3及托盘11可以是分别具有能相互卡合的导引结构33、113,举例来说,盖体3的各个导引结构33可以是具有盲孔,托盘11的各个导引结构113可以是柱状结构,而盖体3盖设于托盘11的一侧时,托盘11的柱状结构则会对应卡合于盖体3的盲孔中。通过盖体3的导引结构33及托盘11的导引结构113的设计,可以让盖体3快速且正确地盖设于托盘11的一侧,并据以使各个抵压组件4能够快速且正确地位于芯片容槽122中的芯片c的一侧。盖体3的导引结构33及托盘11的导引结构113的数量及外型等皆不以图中所示为限。

69.如图13至图18所示,各个抵压组件4包含:一底座41、一抵压件42及两个弹性件43。于本实施例中,是以16个抵压组件4共用同一个底座41为例,但不以此为限,在不同的实施例中,也可以是多个抵压组件4不共用同一个底座41。底座41可以是可拆卸地固定设置于盖体3的传导结构32。在不同的实施例中,底座41也可以是与传导结构32一体成型地设置。在底座41是可拆卸地固定设置于盖体3的实施例中,相关人员将可以轻易地进行抵压组件4的更换及维修。

70.各个抵压件42包含一接触部421及一抵靠部422。接触部421具有一接触面4211,接触部421的外径w4小于插入穿孔153的孔径w3(如图8所示),而接触部421的一部分能伸入插入穿孔153(如图18所示),且接触面4211能抵压芯片c的表面c1。接触部421主要是用来抵压芯片c的表面c1,以使芯片c可以稳定地与测试机台2(如图1所示)相连接,借此,避免芯片c在被测试机台2测试的过程中与探针座23(如图2所示)的探针相互分离。

71.抵靠部422与接触部421相连接,抵靠部422用来限制抵压件42相对于辅助插入件15的移动范围,从而避免接触部421过度地抵压芯片c。如图18所示,当盖体3盖设于托盘11的一侧时,各个抵压件42的抵靠部422将会位于辅助插入件15的一侧,而抵压件42的接触部421则会对应位于插入穿孔153中,且接触面4211则是对应位于芯片c的表面c1的一侧。

72.各个弹性件43的两端固定于底座41及抵压件42。当抵压件42的接触面4211接触于不平坦的芯片c的表面c1时,至少一个弹性件43将呈现为受压的状态,而弹性件43受压所产生的弹性回复力,可以使接触面4211仍紧密地接触于芯片c的表面c1。各个抵压组件4所包含的弹性件43的数量,不以两个为限,在不同的实施例中,单一个抵压组件4也可以是仅包含一个弹性件43或是3个以上的弹性件43。

73.如图14及图15所示,在实际应用中,弹性件43例如可以是压缩弹簧。抵压组件4可以是包含两个压缩弹簧(弹性件43),且抵压组件4还可以包含两个导引件44及两个固定套件45。抵压件42的抵靠部422可以是具有两个第一凹槽4221,底座41则是具有两个第二凹槽411,各个第一凹槽4221面对一个第二凹槽411设置,各个压缩弹簧的两端分别卡合于第一凹槽4221及第二凹槽411。

74.抵压件42的抵靠部422还可以具有两个贯穿孔4222,各个贯穿孔4222与各个第一凹槽4221相互连通,两个固定套件45固定设置于两个贯穿孔4222中,各个固定套件45具有一贯穿孔451,各个导引件44的一端固定于底座41,各个导引件44的另一端穿过各个固定套件45的贯穿孔451。抵压件42相对于底座41移动活动时,各个固定套件45能相对于各个导引件44活动,而两个导引件44及两个固定套件45能共同限制抵压件42相对于底座41的移动方向。通过两个导引件44及固定套件45的设计,可以有效地限制抵压件42是大致沿着垂直于底座41的表面的轴线l(如图18所示)移动,如此,抵压件42抵压于芯片c的表面c1时,抵压件42的接触部421将会是整个接触面4211与芯片c的表面c1相接触。

75.请复参图14,各个抵压组件4还可以包含至少一固定结构46及至少一限位件47,限位件47可拆卸地与固定结构46相互固定,限位件47的一部分抵靠于抵压件42的抵靠部422,而限位件47及固定结构46能共同限制抵压件42相对于底座41的活动范围。举例来说,底座41可以是具有24个固定结构46,每4个固定结构46排列成一排地设置于底座41,每6个固定结构46与2个限位件47共同限制4个抵压件42,而24个固定结构46则是与8个限位件47相互配合,而使16个抵压件42设置于底座41。其中,各个固定结构46可以是具有一锁孔461,各个限位件47则是具有3个穿孔471,而3个螺丝s能与3个固定结构46及一个限位件47的3个穿孔471相互配合,而使单一个限位件47与3个固定结构46相互固定,且单一个限位件47是对应抵压于4个抵压件42的抵靠部422。

76.在实际应用中,限位件47还可以包含一容置缺口472,容置缺口472用以容置接触部421的一部分。在本实施例的附图中,因此,单一个限位件47同时抵靠于4个限位件47的抵靠部422,因此,限位件47可以是对应具有4个容置缺口472,而4个容置缺口472则是对应容置4个限位件47的接触部421的一部分。通过容置缺口472的设计,可以辅助限制抵压件42相对于底座41的活动方向,而使抵压件42大致是沿着垂直于底座41的轴线l(如图18所示)的方向移动。

77.在各个抵压组件4具有导引件44的实施例中,限位件47则是对应具有至少一避让穿孔473,各个避让穿孔473用以提供导引件44穿出,也就是说,抵压件42向底座41的方向移动时,导引件44的一部分将穿出于避让穿孔473。关于避让穿孔473的外型不以图中所示为限。

78.请一并参阅图1、图13、图16至图18,温度调节装置5可以是通过盖体3,而与多个抵压组件4相连接,温度调节装置5用以使各个抵压件42的温度到达一预定温度。通过温度调节装置5的设置,当设置于芯片固定件12的芯片c与测试机台2相连接,而被测试机台2进行测试时,到达预定温度的抵压件42将抵压于芯片c(如图8所示)的表面c1(如图8所示),如此,将可以使芯片c是在预定温度的环境下进行测试。在较佳的实施例中,抵压件42例如可以是由具有高导热系数的金属材质所制成。

79.在现有常见的芯片测试作业中,多个芯片是被设置于大型的冷冻腔室或是烤箱中

进行测试,由于冷冻腔室或是烤箱的各区域的温度难以完全相同,因此,多个芯片并无法在相同的温度下进行测试作业,如此,导致测试结果不可靠。反观,本发明的芯片测试设备a是在芯片c被测试机台2进行测试的过程中,使到达预定温度的各个抵压件42的接触面4211,抵压于各个芯片c的表面c1,如此,多个芯片c将是位在大致相同的温度下被测试。

80.在实际应用中,温度调节装置5可以是依据需求,以任何方式使各个抵压件42的温度到达预定温度,于此不加以限制。举例来说,温度调节装置5可以是与盖体3的传导结构32相连接,且各个底座41固定于传导结构32,温度调节装置5能使传导结构32的温度上升或下降,而传导结构32能通过多个底座41及多个弹性件43与多个抵压件42相互传递热能,以使各个抵压件42的温度到达预定温度。于此所指的传导结构32是指利用具有高导热系数的材质所制成的结构。在盖体3的本体31与传导结构32为一体成型的实施例中,温度调节装置5即是通过盖体3与多个抵压组件4相互传递热能。在传导结构32与盖体3的本体31非为一体成型的实施例中,温度调节装置5则可以是直接与传导结构32相连接。

81.在其中一个实施例中,传导结构32内可以是包含有至少一流道(图未示),而温度调节装置5则能提供一流体至流道中,以使传导结构32的温度上升或下降。所述流体例如是各式高温流体或是低温流体。在其中一个实施例中,温度调节装置5可以是包含一温度控制器(图未示)及一加热线圈(图未示),温度控制器与加热线圈电性连接,加热线圈设置于传导结构32中,温度控制器能使加热线圈作动,以使传导结构32的温度上升。在温度调节装置5包含温度控制器的实施例中,温度调节装置5还可以是包含有一致冷芯片(图未示),温度控制器与致冷芯片电性连接,致冷芯片设置于传导结构32中,温度控制器能使致冷芯片作动,以使传导结构32的温度下降。在实际应用中,传导结构32内也可以是同时设置有致冷芯片及加热线圈,于此不加以限制。

82.如图14所示,为了使抵压件42的温度更容易到达所述预定温度,各个抵压组件4还可以包含一导热件48。导热件48位于抵压件42与底座41之间,且导热件48与抵压件42及底座41相连接,而导热件48用以辅助抵压件42与底座41彼此间的热能相互传递。导热件48例如可以是包含有两个弹性臂481,两个弹性臂481的一端相互连接。当抵压件42向底座41的方向移动时,两个弹性臂481将受抵压件42抵压而弹性变形,而抵压件42向远离底座41的方向移动时,弹性臂481受压所产生的弹性回复力,将使弹性臂481恢复至未受压的状态,如此,无论在抵压件42静止或是相对于底座41活动的过程中,抵压件42与传导结构32彼此间的热能皆可以通过导热件48良好地相互传递。值得一提的是,前述导引件44及固定套件45也可以选用高导热系数的材料,而导引件44及固定套件45也可以是用来进行抵压件42、底座41及传导结构32彼此间的热能传导。

83.请一并参阅图1、图16至图19,在实际应用中,芯片测试设备a还可以是包含有一抽真空装置6、一移动装置7及一处理装置8。处理装置8电性连接测试机台2、抽真空装置6及移动装置7,而处理装置8可以控制测试机台2、抽真空装置6及移动装置7作动。处理装置8例如是各式计算机、各式服务器等。

84.移动装置7与盖体3相连接,而移动装置7能带动盖体3向靠近或远离托盘11的方向移动。于此所指的移动装置7主要是用来使盖体3及托盘11彼此相互靠近或彼此相互远离,因此,在不同的实施例中,移动装置7也可以是与托盘11相连接,而移动装置7则是带动托盘11向靠近或远离盖体3的方向移动。

85.当移动装置7带动盖体3向托盘11的方向移动,并使盖体3盖设于托盘11的一侧,且托盘11相反于盖体3的一侧固定于测试机台2时,各抵压件42的接触面4211将抵靠于芯片c的表面c1,芯片c的一侧则是与测试机台2的探针座23相连接,且盖体3、芯片固定件12、托盘11及多个芯片c将共同形成一封闭空间sp。此时,处理装置8将控制抽真空装置6作动,而使抽真空装置6抽取该封闭空间sp内的空气,据以使该封闭空间sp呈现为负压状态。

86.值得一提的是,芯片测试设备a还可以是包含有至少一检测器(图未示),检测器电性连接处理装置8,检测器用来检测盖体3是否盖设于托盘11的一侧,而处理装置8通过检测器的检测结果,判断盖体3已经盖设于托盘11的一侧时,处理装置8将控制抽真空装置6作动。

87.通过抽真空装置6将封闭空间sp内的气体向外抽出,而使封闭空间sp呈现为负压状态的设计,还可以有效地避免封闭空间sp内的温度受到封闭空间sp外的环境影响外,据以有效地控制封闭空间sp的湿度,从而可以大幅将低芯片c的表面c1发生结露的问题。

88.请一并参阅图8及图18,由于各个辅助插入件15的插入穿孔153的孔径w3是小于芯片容槽122的孔径w2,因此,当封闭空间sp由负压状态转换回常压状态,且移动装置7向远离托盘11的方向移动的过程中,若芯片c与抵压件42发生沾黏的问题,在接触部421沿着插入穿孔153离开辅助插入件15的过程中,芯片c将被辅助插入件15的凸出部152靠近芯片容槽122的一端推抵而与接触部421分离。也就是说,通过于托盘11设置辅助插入件15,以及使插入穿孔153的孔径w3是小于芯片容槽122的孔径w2的设计,将可以确保盖体3及多个抵压组件4向远离托盘11的方向移动时,发生芯片c沾黏于接触部421的问题。

89.上述本发明的芯片测试设备a于制造及贩卖时,可以是包含有测试机台2、盖体3、多个抵压组件4、温度调节装置5及处理装置8,但不以此为限,在不同实施例中,本发明的芯片测试设备a于制造及贩卖时,还可以是包含有芯片托盘套件1、抽真空装置6及移动装置7中的至少一个。另外,上述本发明的芯片托盘套件1也可以是单独地被制造及贩卖。

90.请参阅图19,其显示为本发明的抵压组件的不同实施例的剖面示意图。本实施例的抵压组件与前述实施例最大不同之处在于:导热件48可以是柱体结构,导热件48的一端固定于抵压件42的一凹槽423中,且导热件48的一端是可活动地设置于底座41的一容槽412中,导热件48的另一端则是与抵压件42相互固定。抵压件42相对于底座41活动时,导热件48则对应于底座41的容槽412中活动,且导热件48是随时与形成容槽412的侧壁相接触,而温度调节装置5则是通过底座41及呈现为柱体结构的导热件48,与抵压件42相互传递热能。

91.综上所述,本发明的抵压组件可以应用于芯片测试设备中,而抵压组件能够抵压正在被测试的芯片的表面,据以使芯片在被测试的过程中,能够稳固地与相关的电连接座相连接;本发明的抵压组件还可以与温度调节装置相连接,而抵压件的温度将可以到达预定温度,借此,抵压在正被测试的芯片的表面的抵压件,将可以使芯片处在预定温度的状态下被测试。本发明的芯片测试设备,通过抵压组件及温度调节装置的设计,可以让芯片在被测试机台进行测试的过程中,被抵压件抵压而稳固地与测试机台相连接,且到达预定温度的抵压件还可以使芯片处在预定温度的情况下被测试机台进行测试;本发明的芯片测试设备还可以具有抽真空装置,通过抽真空装置的设置,可以使芯片及到达预定温度的抵压件,不易受到外在环境影响。

92.以上所述仅为本发明的较佳可行实施例,非因此局限本发明的专利范围,故凡运

用本发明说明书及附图内容所做的等效技术变化,均包含于本发明的保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1