一种微波着陆设备和精密测距设备通用的监测器平台的制作方法

1.本发明涉及微波着陆设备和精密测距设备通用的监测数字处理技术领域,特别涉及一种微波着陆设备和精密测距设备通用的监测器平台。

背景技术:

2.mls着陆系统和精密dme系统已经成为先进飞机精密着陆引导的必备设备,两个系统常常一起安装,在保障飞机安全着陆方面起着十分重要的作用。监测器在这两种设备中有着监测设备的功能,参数是否告警能直接反映设备是否处于正常工作状态。

技术实现要素:

3.本发明的目的旨在至少解决所述技术缺陷之一。

4.为此,本发明的目的在于提出一种微波着陆设备和精密测距设备通用的监测器平台。

5.为了实现上述目的,本发明的实施例提供一种微波着陆设备和精密测距设备通用的监测器平台,包括:

6.模拟输入通道、双通道a/d模数转换器、数据处理模块、参数存储调用模块、can通信模块、电平转换电路、时间模块和电源供电电路,其中,

7.所述模拟输入通道与双通道a/d模数转换器连接,双通道a/d模数转换器与数据处理模块中的fpga芯片连接,所述数据处理模块中的fpga芯片、dsp芯片与存储调用模块和时间模块通过总线连接,所述数据处理模块中的fpga的芯片与电平转换电路连接;所述dsp芯片与can通信模块连接;

8.所述双通道a/d模数转换器包括:a/d芯片、外围电阻器、电容器和电阻排组,其中,所述a/d芯片与所述电阻排组连接,所述外围电阻器用于对所述a/d芯片进行功能配置,所述电容器用于对所述a/d芯片进行供电和参考电压滤波;

9.所述数据处理模块包括:fpga芯片、第一晶振、复位芯片、第一下载接口、第二下载接口、dsp芯片、第二晶振和第二下载接口,其中,所述fpga芯片与所述dsp芯片之间的总线采用电阻排连接,所述第一晶振、复位芯片、第一下载接口、第二下载接口分别与fpga芯片连接,所述第二晶振和第二下载接口与dsp芯片连接;

10.所述参数存储调用模块包括:e2prom芯片、flash芯片和铁电,其中,e2prom芯片与fpga芯片连接,所述flash芯片和铁电通过数据总线分别与dsp芯片连接;

11.所述can通信模块包括:第一晶体、can扩展芯片、can通信芯片,其中,所述第一晶体与所述can扩展芯片连接,所述can扩展芯片与所述can通信芯片连接;

12.所述电平转换电路包括:电平转换芯片和电阻排,其中,所述电平转换芯片与所述电阻排和fpga芯片连接;

13.所述时间模块包括:第二晶体、电池、三级管和时间芯片,其中,所述第二晶体和电池分别与所述时间芯片连接,所述电池与所述三极管连接;

14.所述电源供电电路包括:可熔断保险丝组件和电源芯片组件,其中,所述电源芯片组件与所述可熔断保险丝组件连接,由所述电源芯片组件对来自所述可熔断保险丝组件接入的电压进行电源转换,然后将转换后的电压向监测器相应的芯片供电。

15.进一步,所述模拟输入通道包括:7个运算放大器、多路模拟开关、第一差分运算放大器、多路模拟开关、第二差分运算放大器,其中,所述多路模拟开关与第一差分运算放大器和第二差分运算放大器连接,并且所述第一差分运算放大器和第二差分运算放大器输出的差分信号分别送入双通道a/d模数转换器。

16.进一步,a/d芯片的采样数据通过数据总线达到dsp芯片,由所述dsp芯片判断并进行相应的处理,在通过can接口发送至到显示平台。

17.进一步,所述可熔断保险丝组件包括:第一可熔断保险丝、第二可熔断保险丝、第三可熔断保险丝;所电源芯片组件包括:第一电源芯片、第二电源芯片、第三电源芯片和第四电源芯片;其中,所述第一可熔断保险丝、第二可熔断保险丝、第三可熔断保险丝分别是输入+5v电压、+15v电压和-15v电压;所述第一电源芯片将+5v电压转为3.3v、所述第二电源芯片将+5v电压转为1.2v、所述第三电源芯片将+5v电压转为2.5v,所述第四电源芯片将-15v电压转为-5v,转换后的电压给监测器相应的芯片供电。

18.进一步,所述dsp芯片执行以下功能:上电初始化、自检测功能、通信功能、数据采集分析和数据处理功能,其中,

19.所述上电初始化包括:对外部硬件和dsp内部资源进行上电初始化;

20.所述自检测功能包括:上电自检;

21.所述通信功能包括:can总线收发和i/o总线收发;

22.所述数据采集分析包括:高速数据采集、数据传输及预处理、数据计算和判断;

23.所述数据处理功能包括:告警存储和调用、协议的解析打包。

24.进一步,所述fpga芯片包括:分频模块、ad接口、双口ram、主状态机、脉冲计算状态机和dsp总线接口,其中,所述分频模块的输入端接入20mhz信号,所述分频模块的输出端与所述ad接口的输入端连接,所述ad接口的输出端与所述双口ram的输入端连接,所述主状态机与所述dsp总线接口双向连接,所述主状态机的输出端与所述双口ram的输入端连接,所述双口ram与所述dsp总线接口双向连接;所述脉冲计算状态机的输出端与所述dsp总线接口的输入端连接。

25.进一步,所述电平转换电路接入频率信号、dpsk信号、自检扫描信号、自检dpsk信号和周期同步信号。

26.进一步,所述监测器对来自内场、外场、数据、oci各路检波信号进行测量,得到各种信号功率值和角度信息;测量来自频合的dpsk检波信号,监测前导码、基本/辅助数据字信息、测量帧率和数据字正确性;测量失效移相器数量;测量方位/仰角同步叠加时间;测量扫描完整周期时间;接收来自通信接口的自检信号进行周期自检,确保监测器自身的完好性。

27.进一步,所述dsp总线接口接入dsp地址和数据总线,所述主状态机接收dpsk信号,并向外发送模拟开关信号;所述脉冲计算状态机接收20mhz信号、移相器脉冲、同步周期脉冲和频率信号,并向所述dsp总线接口发送中断信号和数据信号。

28.进一步,所述dsp总线接口向所述双口ram发送双口ram地址信号,并接收所述双口

ram返回的数据信号。

29.根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台,监测器的主要功能是监视设备辐射信号是否正常,即将所有测量与预置在板上存储器内的相应告警门限进行比较,若超出告警门限,则向控制单元发出告警指示信号,通知相应控制单元进行主、备机切换或关机。同时保存此时告警记录。其技术先进、工作稳定、性能可靠,满足微波着陆设备和精密测距设备的监测需求。该数字处理单元监测器在微波着陆设备和精密测距设备中实现了采样数字处理技术,将硬件功能软件化,可操作性好。同时实现了内、外场信号的角度等参数实时监视,角度的测量速度和精度均比上一代产品有所提高。技术效果是其技术先进、工作稳定、性能可靠,满足微波着陆设备和精密测距设备的监测需求。本发明的数字处理单元监测器在微波着陆设备和精密测距设备中实现了采样数字处理技术,将硬件功能软件化,可操作性好。同时实现了内、外场信号的角度等参数实时监视,角度的测量速度和精度均比上一代产品有所提高。

30.本发明附加的方面和优点将在下面的描述中部分给出,部分将从下面的描述中变得明显,或通过本发明的实践了解到。

附图说明

31.本发明的上述和/或附加的方面和优点从结合下面附图对实施例的描述中将变得明显和容易理解,其中:

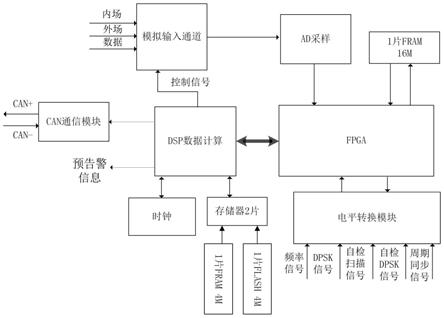

32.图1为根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台的硬件组成框图;

33.图2为根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台的dsp功能模块结构图;

34.图3为根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台的fpga功能模块结构图;

35.图4a和图4b为根据本发明实施例的7个运算放大器的电路图;

36.图5为根据本发明实施例的一组的多路模拟开关和差分运算放大器的电路图;

37.图6为根据本发明实施例的另一组的多路模拟开关和差分运算放大器的电路图;

38.图7为根据本发明实施例的a/d芯片的电路图;

39.图8为根据本发明实施例的fpga芯片的电路图;

40.图9为根据本发明实施例的dsp芯片的电路图;

41.图10为根据本发明实施例的flash芯片的电路图;

42.图11为根据本发明实施例的铁电的电路图;

43.图12a和图12b为根据本发明实施例的电平转换芯片的电路图;

44.图13为根据本发明实施例的时间芯片的电路图;

45.图14为根据本发明实施例的can扩展芯片的电路图;

46.图15为根据本发明实施例的电源芯片的电路图。

具体实施方式

47.下面详细描述本发明的实施例,所述实施例的示例在附图中示出,其中自始至终

相同或类似的标号表示相同或类似的元件或具有相同或类似功能的元件。下面通过参考附图描述的实施例是示例性的,旨在用于解释本发明,而不能理解为对本发明的限制。

48.本应用涉及微波着陆设备和精密测距设备通用的监测数字处理技术。此监测平台在不仅可应用于以上两种设备,由于具有冗余设计,还可应用在如塔康等其他设备具有监测功能的数字处理电路中。

49.如图1所示,本发明实施例的微波着陆设备和精密测距设备通用的监测器平台,包括:模拟输入通道、双通道a/d模数转换器、数据处理模块、参数存储调用模块、can通信模块、电平转换电路、时间模块和电源供电电路。采用fpga+dsp双cpu的架构,其中fpga主要负责数字信号处理任务,dsp主要负责控制、通信、存储等任务,采用可编程逻辑器件,将硬件功能软件化。

50.模拟输入通道与双通道a/d模数转换器连接,双通道a/d模数转换器与数据处理模块中的fpga芯片连接,数据处理模块中fpga芯片、dsp芯片与存储调用模块和时间模块用总线连接,数据处理模块中fpga芯片与电平转换电路连接。监测器同时监测设备中的控制器、发射机组件和天线反馈信号,同时监测器具备自检功能,可接收来自通信接口的自检信号进行周期自检功能,验证监测器自身测量功率和角精度的准确性,以确保监测器自身的完好性。

51.监视设备的辐射信号是否正常,即将所有测量的参数与预置在监测器上存储器内的相应告警门限进行比较,若超出告警门限,则向主控单元发出告警指示信号,通知相应控制单元进行主、备机切换或关机。同时保存此时告警记录。

52.具体的,模拟输入通道与双通道a/d模数转换器连接,双通道a/d模数转换器与数据处理模块中的fpga芯片连接,数据处理模块中的fpga芯片、dsp芯片与存储调用模块和时间模块通过总线连接,数据处理模块中的fpga的芯片与电平转换电路连接;dsp芯片与can通信模块连接。

53.模拟输入通道包括:7个运算放大器、多路模拟开关、第一差分运算放大器、多路模拟开关、第二差分运算放大器,其中,三路通道用于微波设备监测的模拟信号输入,两路通道用于精密测距设备监测的模拟信号输入。运算放大器与多路模拟开关连接,多路模拟开关与第一差分运算放大器和第二差分运算放大器连接,并且第一差分运算放大器和第二差分运算放大器输出的差分信号分别送入双通道a/d模数转换器。

54.如图4a和图4b所示,模拟输入通道包括n301~n307等7个运算放大器、多路模拟开关d302、差分运算放大器d303和多路模拟开关d304、差分运算放大器d305。其中:三路通道用于微波设备监测的模拟信号输入,两路通道用于精密测距设备监测的模拟信号输入。n301与n302连接,n303与n304连接,n302、n305和n307与d302连接,n304、n306与d304连接,多路模拟开关d302与差分运算放大器d303连接,多路模拟开关d304与差分运算放大器d305连接,参考图5和图6所示。两个差分运算放大器输出的差分信号分别送入a/d模数转换器进行采样。

55.双通道a/d模数转换器包括:a/d芯片、外围电阻器、电容器和电阻排组,其中,a/d芯片与电阻排组连接,外围电阻器用于对a/d芯片进行功能配置,电容器用于对a/d芯片进行供电和参考电压滤波。

56.参考图7,双通道a/d模数转换器包括a/d芯片d301和其外围电阻器、电容器及电阻

排组。其中:a/d模数转换器d301与电阻排连接,外围电阻器用于d301的功能配置,电容器分别用于芯片供电和参考电压滤波。

57.数据处理模块包括:fpga芯片、第一晶振、复位芯片、第一下载接口、第二下载接口、dsp芯片、第二晶振和第二下载接口,其中,fpga芯片与dsp芯片之间的总线采用电阻排连接,第一晶振20mhz晶振、复位芯片、第一下载接口config下载接口、第二下载接口jtag下载接口分别与fpga芯片连接,第二晶振37.5mhz晶振和第二下载接口jtag下载接口与dsp芯片连接。a/d的采样数据通过数据总线进入fpga进行计算,计算后的数据再通过总线送到dsp,由dsp判断并进行相应的处理,再通过can口送到显示平台。

58.图8为根据本发明实施例的fpga芯片的电路图。图3为根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台的fpga功能模块结构图。数据处理模块包括fpga芯片d101、晶振g1、复位芯片d103、下载接口xp11、下载接口xp12、dsp芯片d201、晶振g21和下载接口xp2。其中:fpga芯片d101与dsp芯片d201之间的总线用电阻排连接,晶振g1、复位芯片d103、下载接口xp11、下载接口xp12与fpga芯片d101连接,晶振g21和下载接口xp2与dsp芯片d201连接。a/d的采样数据通过数据总线进入fpga进行计算,计算后的数据再通过总线送到dsp,由dsp判断并进行相应的处理,再通过can口送到显示平台。

59.参考图3,dsp总线接口接入dsp地址和数据总线,主状态机接收dpsk信号,并向外发送模拟开关信号;脉冲计算状态机接收20mhz信号、移相器脉冲、同步周期脉冲和频率信号,并向dsp总线接口发送中断信号和数据信号。dsp总线接口向双口ram发送双口ram地址信号,并接收双口ram返回的数据信号。

60.图2为根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台的dsp功能模块结构图。图9为根据本发明实施例的dsp芯片的电路图。

61.dsp芯片执行以下功能:上电初始化、自检测功能、通信功能、数据采集分析和数据处理功能,其中,

62.上电初始化包括:对外部硬件和dsp内部资源进行上电初始化;

63.自检测功能包括:上电自检;

64.通信功能包括:can总线收发和i/o总线收发;

65.数据采集分析包括:高速数据采集、数据传输及预处理、数据计算和判断;

66.数据处理功能包括:告警存储和调用、协议的解析打包。

67.参考图3,fpga芯片包括:分频模块、ad接口、双口ram、主状态机、脉冲计算状态机和dsp总线接口,其中,分频模块的输入端接入20mhz信号,分频模块的输出端与ad接口的输入端连接,ad接口的输出端与双口ram的输入端连接,主状态机与dsp总线接口双向连接,主状态机的输出端与双口ram的输入端连接,双口ram与dsp总线接口双向连接;脉冲计算状态机的输出端与dsp总线接口的输入端连接。

68.参数存储调用模块包括:e2prom芯片、flash芯片和铁电,其中,e2prom芯片与fpga芯片连接,flash芯片和铁电通过数据总线分别与dsp芯片连接。

69.图10为根据本发明实施例的flash芯片的电路图;图11为根据本发明实施例的铁电的电路图。具体的,参数存储调用模块包括e2prom芯片d102、flash芯片d203和铁电d204。其中:e2prom芯片d102与d101连接,flash芯片d203和铁电d204通过数据总线分别与d201连接。

70.can通信模块包括:第一晶体、can扩展芯片、can通信芯片,其中,第一晶体与can扩展芯片连接,can扩展芯片与can通信芯片连接。图14为根据本发明实施例的can扩展芯片的电路图。can接口包括第一晶体g24、can扩展芯片d208、can通信芯片d209。其中:第一晶体g24与can扩展芯片d208连接,can扩展芯片d208与can通信芯片d209连接。

71.电平转换电路包括:电平转换芯片和电阻排,其中,电平转换芯片与电阻排和fpga芯片连接。具体的,电平转换电路包括4片电平转换芯片和电阻排。其中:3片电平转换芯片与fpga的i/o连接,1片电平转换芯片与电阻排连接。3片作为输入信号转换用,1片作为输出信号转换用。

72.电平转换电路接入频率信号、dpsk信号、自检扫描信号、自检dpsk信号和周期同步信号。

73.如图12a和图12b所示,电平转换电路包括电平转换芯片d601、d602、d603、d604和电阻排rn61~rn68。其中:d601与d604部分管脚连接,d601、d602、d603与fpga的i/o连接,d604其余管脚与电阻排rn61~rn68。d601、d602和d603作为输入信号转换用,d604作为输出信号转换用。

74.时间模块包括:第二晶体、电池、三级管和时间芯片,其中,第二晶体和电池分别与时间芯片连接,电池与三极管v23连接。图13为根据本发明实施例的时间芯片的电路图。电池为时钟芯片供电,即使设备关机,时钟芯片仍然能工作。三极管的输出提供电池测试电压,保证低电压时能及时更换。

75.具体的,时间模块包括晶体g22、电池gb1、三极管v23和时间芯片d202。其中:晶体g22、电池gb1与d202连接,gb1与三极管v23连接。电池为时钟芯片供电,即使设备关机,时钟芯片仍然能工作。三极管v23的输出提供电池测试电压,保证低电压时能及时更换。

76.电源供电电路包括:可熔断保险丝组件和电源芯片组件,其中,电源芯片组件与可熔断保险丝组件连接,由电源芯片组件对来自可熔断保险丝组件接入的电压进行电源转换,然后将转换后的电压向监测器相应的芯片供电。图15为根据本发明实施例的电源芯片的电路图。

77.其中:可熔断保险丝分别是输入+5v电压、+15v电压和-15v电压。电源芯片根据配置的电阻将+5v电压转为3.3v、1.2v、2.5v,电源芯片将-15v电压转为-5v,转换后的电压给监测器相应的芯片供电。

78.具体的,可熔断保险丝组件包括:第一可熔断保险丝、第二可熔断保险丝、第三可熔断保险丝;所电源芯片组件包括:第一电源芯片、第二电源芯片、第三电源芯片和第四电源芯片;其中,第一可熔断保险丝、第二可熔断保险丝、第三可熔断保险丝分别是输入+5v电压、+15v电压和-15v电压;第一电源芯片将+5v电压转为3.3v、第二电源芯片将+5v电压转为1.2v、第三电源芯片将+5v电压转为2.5v,第四电源芯片将-15v电压转为-5v,转换后的电压给监测器相应的芯片供电。

79.电源供电电路包括可熔断保险丝f501~f503、电源芯片d501~d504。其中:可熔断保险丝f501~f503分别是输入+5v电压、+15v电压和-15v电压。d501将+5v电压转为3.3v、d502将+5v电压转为1.2v、d503将+5v电压转为2.5v和d504将-15v电压转为-5v,转换后的电压给监测器相应的芯片供电。

80.监视分系统采用双监测器,由监测器1、监测器2组成。

81.监视器分系统的主要功能是监视设备辐射信号是否正常,即将所有测量与预置在板上存储器内的相应告警门限进行比较,若超出告警门限,则向主控单元发出告警指示信号,通知相应控制单元进行主、备机切换或关机。同时保存此时告警记录。

82.监测器监视的信号包括:

83.(1)对来自内场、外场、数据、oci各路检波信号进行测量,得到各种信号功率值,角度信息。对其角精度、功率幅度、pfe、cmn等信息进行实时处理和判断;

84.(2)测量来自频合的dpsk检波信号,监测前导码、基本/辅助数据字信息,测量帧率和数据字正确性;

85.(3)测量失效移相器数量;

86.(4)测量方位/仰角同步叠加时间;

87.(5)测量扫描完整周期时间;

88.(6)接收来自通信接口的自检信号进行周期自检,确保监测器自身的完好性。

89.技术指标如下:

90.(1)硬件技术指标

91.a)can口通讯速率:500kbps;

92.b)电源功耗:≤7.5w;

93.c)a/d转换:输入电压:0.0v~2v;

94.d)转换位数:14位;

95.e)转换速度:40mhz;

96.f)输入io数:54;

97.g)输出io数:5。

98.(2)系统参数技术指标

99.a)测量角精度:

±

0.002

°

;

100.b)测量电平精度:

±

0.01v;

101.c)测量频率精度:

±

1khz;

102.d)功率幅度精度:0.01v;

103.e)功率百分比精度:1%;

104.f)内场电平精度:1db;

105.g)同步完整周期精度:0.1ms;

106.h)同步叠加测量:1us。

107.根据本发明实施例的微波着陆设备和精密测距设备通用的监测器平台,监测器的主要功能是监视设备辐射信号是否正常,即将所有测量与预置在板上存储器内的相应告警门限进行比较,若超出告警门限,则向控制单元发出告警指示信号,通知相应控制单元进行主、备机切换或关机。同时保存此时告警记录。其技术先进、工作稳定、性能可靠,满足微波着陆设备和精密测距设备的监测需求。该数字处理单元监测器在微波着陆设备和精密测距设备中实现了采样数字处理技术,将硬件功能软件化,可操作性好。同时实现了内、外场信号的角度等参数实时监视,角度的测量速度和精度均比上一代产品有所提高。技术效果是其技术先进、工作稳定、性能可靠,满足微波着陆设备和精密测距设备的监测需求。本发明的数字处理单元监测器在微波着陆设备和精密测距设备中实现了采样数字处理技术,将硬

件功能软件化,可操作性好。同时实现了内、外场信号的角度等参数实时监视,角度的测量速度和精度均比上一代产品有所提高。

108.在本说明书的描述中,参考术语“一个实施例”、“一些实施例”、“示例”、“具体示例”、或“一些示例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特点包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性表述不一定指的是相同的实施例或示例。而且,描述的具体特征、结构、材料或者特点可以在任何的一个或多个实施例或示例中以合适的方式结合。

109.尽管上面已经示出和描述了本发明的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本发明的限制,本领域的普通技术人员在不脱离本发明的原理和宗旨的情况下在本发明的范围内可以对上述实施例进行变化、修改、替换和变型。本发明的范围由所附权利要求及其等同限定。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1