一种航空发动机的振动监测系统的制作方法

1.本发明涉及航空发动机监测技术领域,特别地,涉及一种航空发动机的振动监测系统。

背景技术:

2.航空发动机的结构复杂,工作条件严苛,为了保证其能够稳定、可靠地工作,其性能参数监测为重中之重,其中,振动作为航空发动机的动态参数之一,对于发动机工作的可靠性起到关键性的决定作用。而目前关于发动机的振动监测,通常都是采取在地面模拟发动机的各种工作状态实现振动模拟测试,但是,发动机的振动情况受实际工作环境的影响较大,而实际工作环境变化多端,因此,地面的振动模拟测试结果无法准确表征发动机实际工作的振动情况,无法准确地对发动机的振动超限状态进行监测。

技术实现要素:

3.本发明提供了一种航空发动机的振动监测系统,以解决现有技术无法准确地对发动机的振动超限状态进行监测的技术问题。

4.根据本发明的一个方面,提供一种航空发动机的振动监测系统,包括:

5.两个振动传感器,用于采集航空发动机的振动数据;

6.两路电荷放大电路,用于对两个振动传感器的振动信号分别进行放大处理,并将振动传感器输出的电荷信号转换为电压信号后输出;

7.adc采样芯片,用于采集两路电荷放大电路输出的两路电压信号,并将电压信号转换为数字信号;

8.fpga芯片,用于控制所述adc采样芯片进行连续采样,将adc采样芯片输出的两路数字信号分开存储后进行并行处理,并将两路振动信号时域数据分别转换为两路振动信号频域数据后输出;

9.dsp处理器,用于获取发动机转速,根据发动机转速和两路振动信号频域数据计算得到每路振动信号的振动分量速度幅值和振动总量速度幅值,并基于振动分量速度幅值和振动总量速度幅值进行发动机振动超限判断。

10.进一步地,所述fpga芯片包括采集数据缓存模块和两路信号处理通道,所述采集数据缓存模块用于对两个所述adc采样芯片采集的两个通道的振动传感器数据进行分区存储,两路信号处理通道用于对两个通道的振动传感器数据进行并行处理。

11.进一步地,所述采集数据缓存模块的数量为两个,采用交替缓存的方式存储adc采样数据。

12.进一步地,每路信号处理通道包括依次顺序连接的滤波处理模块、重采样模块、量纲转换模块、加窗处理模块、fft变换模块、幅值谱计算模块和加窗修正模块,其中所述滤波处理模块用于对adc采样的振动信号的时域数据序列进行滤波处理,并对时域数据序列进行数据截取,所述重采样模块用于对所述滤波处理模块输出的时域数据序列进行重采样,

所述量纲转换模块用于将所述重采样模块输出的时域数据序列中的每个采样点数据的电压值转换为振动加速度值,所述加窗处理模块用于将所述量纲转换模块输出的时域数据序列与窗函数系数序列逐项相乘,输出加窗时域数据序列,所述fft变换模块用于将所述加窗时域数据序列转换为频域数据序列,所述幅值谱计算模块用于计算出频域数据序列中每个频率点的加速度幅值,得到加速度幅值序列,所述加窗修正模块用于将所述加速度幅值序列与加窗修正系数相乘,得到加窗修正后的振动加速度在频域的幅值序列。

13.进一步地,所述滤波处理模块包括滤波单元、趋势项去除单元和数据截取单元,所述滤波单元用于采用加权平均滤波算法对振动信号的时域数据序列进行平滑处理,滤除噪声和干扰,所述趋势项去除单元用于去除掉经过平滑处理后的时域数据序列中的趋势项,所述数据截取单元用于对时域数据序列进行数据截取,截取出的数据点形成新的时域数据序列。

14.进一步地,所述趋势项去除单元首先计算振动信号的均值,然后将振动信号的时域数据序列中的每个点数据减去均值,从而得到去趋势项后的时域数据序列。

15.进一步地,所述加窗处理模块采用窗函数法设计的fir数字滤波器。

16.进一步地,所述fpga芯片还包括时延消除模块,用于在确定滤波器类型后,基于滤波器的阶数和采样频率计算得到时延大小,然后基于时延大小将滤波后的信号波形进行平移变换,从而完全消除fir数字滤波器时延的影响。

17.进一步地,所述fir数字滤波器采用低通滤波器或者高通滤波器时,窗函数选择布莱克曼窗;所述fir数字滤波器采用带通滤波器或者带阻滤波器时,窗函数选择布拉克曼-哈里斯窗。

18.进一步地,所述dsp处理器包括:

19.检波模块,用于采用检波算法识别出加窗修正后的加速度幅值序列中的所有峰值点;

20.发动机转速获取模块,用于通过串口通信获得发动机的转速;

21.第一计算模块,用于根据发动机转速计算得到本次采样周期内的基频和二倍频,并结合加窗修正后的加速度幅值序列获得基频、二倍频对应的振动分量速度幅值;

22.第二计算模块,用于根据所述检波模块识别出的一个采样周期内的所有峰值点来计算每个峰值点的振动分量速度幅值和振动总量速度幅值;

23.振动超限判断模块,用于根据计算得到的所有峰值点的振动分量速度幅值、振动总量速度幅值、基频和二倍频的振动分量速度幅值进行振动超限情况判断,识别出振动超限状态并进行记录。

24.本发明具有以下效果:

25.本发明的航空发动机的振动监测系统,通过两个振动传感器来采集航空发动机的振动数据,并利用两路电荷放大电路对两个振动传感器的振动信号分别进行放大处理,再通过fpga芯片控制adc采样芯片对两路振动信号进行采集,并将两路振动信号分开存储后进行并行处理,两路振动信号的处理过程互不干预,防止两路信号之间出现信号干扰问题,保证了计算结果的准确度,并有效降低了计算时间。然后,通过dsp处理器获取发动机转速,并根据发动机转速和两路振动信号频域数据计算得到每路振动信号的振动分量速度幅值和振动总量速度幅值,最后基于两路振动信号对应的振动分量速度幅值和振动总量速度幅

值进行发动机振动超限判断,一旦某一路振动信号的振动分量速度幅值或振动总量速度幅值超过预设阈值时,则记录下振动超限状态,必要时还可以进行告警,从而实现对发动机振动情况的智能化监测。

26.除了上面所描述的目的、特征和优点之外,本发明还有其它的目的、特征和优点。下面将参照图,对本发明作进一步详细的说明。

附图说明

27.构成本技术的一部分的附图用来提供对本发明的进一步理解,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。在附图中:

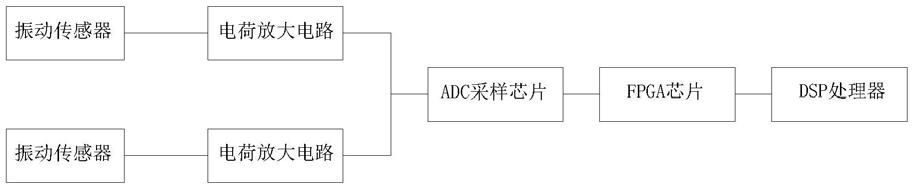

28.图1是本发明优选实施例的航空发动机的振动监测系统的模块结构示意图。

29.图2是本发明优选实施例的fpga芯片的模块结构示意图。

30.图3是本发明优选实施例的滤波处理模块的单元结构示意图。

31.图4是本发明优选实施例的dsp处理器的模块结构示意图。

具体实施方式

32.以下结合附图对本发明的实施例进行详细说明,但是本发明可以由下述所限定和覆盖的多种不同方式实施。

33.如图1所示,本发明的优选实施例提供一种航空发动机的振动监测系统,包括:

34.两个振动传感器,用于采集航空发动机的振动数据;

35.两路电荷放大电路,用于对两个振动传感器的振动信号分别进行放大处理,并将振动传感器输出的电荷信号转换为电压信号后输出;

36.adc采样芯片,用于采集两路电荷放大电路输出的两路电压信号,并将电压信号转换为数字信号;

37.fpga芯片,用于控制所述adc采样芯片进行连续采样,将adc采样芯片输出的两路数字信号分开存储后进行并行处理,并将两路振动信号时域数据分别转换为两路振动信号频域数据后输出;

38.dsp处理器,用于获取发动机转速,根据发动机转速和两路振动信号频域数据计算得到每路振动信号的振动分量速度幅值和振动总量速度幅值,并基于振动分量速度幅值和振动总量速度幅值进行发动机振动超限判断。

39.其中,所述电荷放大电路分别与振动传感器、adc采样芯片连接,所述fpga芯片分别与所述adc采样芯片和dsp处理器连接,具体地,所述fpga芯片通过spi总线与adc采样芯片连接,通过外部总线与dsp处理器连接。所述振动传感器采用压电式加速度传感器,所述电荷放大电路可以采用基于双路放大器lmc6082构成的一级放大电路和可编程变量增益放大器pga11构成的二级放大电路。adc采样芯片采用ads8684,为4通道16位逐次逼近(sar)模数转换器(adc),采样速率可达500ksps,本发明中的采样频率为40000hz,具有spi兼容接口,可通过spi接口控制采样并读取采样结果。fpga芯片采用xilinx公司的xc6slx100,属于spartan-6系列,资源丰富,包含101261个逻辑单元,180个dsp48乘法器,976kb可配置clb模块,4824kb大小block ram,可以满足大量数据的乘法、加法运算需求。dsp处理器采用ti公司的tms320f2812,f2812属于tms320c2000系列,面向数字控制、运动控制领域,具有较强的

数字信号处理能力和事件管理能力,是目前性价比较高的dsp,tms320f2812最高可工作在150mhz主频,f2812芯片内部具有18k

×

16bit的ram空间,需要外扩ram来满足程序运行空间和数据缓存要求。

40.可以理解,本实施例的航空发动机的振动监测系统,通过两个振动传感器来采集航空发动机的振动数据,并利用两路电荷放大电路对两个振动传感器的振动信号分别进行放大处理,再通过fpga芯片控制adc采样芯片对两路振动信号进行采集,并将两路振动信号分开存储后进行并行处理,两路振动信号的处理过程互不干预,防止两路信号之间出现信号干扰问题,保证了计算结果的准确度,并有效降低了计算时间。然后,通过dsp处理器获取发动机转速,并根据发动机转速和两路振动信号频域数据计算得到每路振动信号的振动分量速度幅值和振动总量速度幅值,最后基于两路振动信号对应的振动分量速度幅值和振动总量速度幅值进行发动机振动超限判断,一旦某一路振动信号的振动分量速度幅值或振动总量速度幅值超过预设阈值时,则记录下振动超限状态,必要时还可以进行告警,从而实现对发动机振动情况的智能化监测。

41.可以理解,如图2所示,所述fpga芯片包括采集数据缓存模块、滤波处理模块、重采样模块、量纲转换模块、加窗处理模块、fft变换模块、幅值谱计算模块和加窗修正模块,其中,所述采集数据缓存模块通过spi接口与adc采样芯片连接,所述采集数据缓存模块、滤波处理模块、重采样模块、量纲转换模块、加窗处理模块、fft变换模块、幅值谱计算模块和加窗修正模块依次顺序连接,所述加窗修正模块还与dsp处理器连接。其中,所述采集数据缓存模块的数量为两个,采用交替缓存的方式缓存adc采样数据,从而可以避免正在采样的数据影响上一采样周期的采集数据,并且,在每个采集数据缓存模块中分区域存储两个通道的振动传感器数据,后续的滤波处理模块、重采样模块等功能模块同样设置有两个,从而形成两条相互并行的信号处理通道。即所述fpga芯片内配置有两条信号处理通道,每条信号处理通道包括依次连接的滤波处理模块、重采样模块、量纲转换模块、加窗处理模块、fft变换模块、幅值谱计算模块和加窗修正模块,所述采集数据缓存模块中分区存储的两个通道的振动传感器数据各自通过一条信号处理通道进行并行处理。

42.其中,如图3所示,所述滤波处理模块包括滤波单元和趋势项去除单元,所述滤波单元采用加权平均滤波算法对振动信号进行滤波处理,以平滑振动信号的时域波形,滤除噪声和干扰,所述趋势项去除单元可以判断振动时序数据中是否存在趋势项,若有随时间累加的线性趋势项,则可以消除趋势项。

43.具体地,趋势项是在测试信号中存在线性项或缓变的非线性项成分,工程实际测量的信号大部分是复杂周期信号与随机信号的混合,而且周期信号往往是研究对象,趋势项的存在会使数值积分的结果产生很大的误差,严重地背离真实情况,因此,在测试信号(积分求速度、位移时)中要先消除趋势项,这是积分中的一个重要的中间步骤。产生趋势项的原因主要有以下几种:

44.①

采样时未对原始信号进行适当处理,如高通滤波,使得信号中含有周期大于采样时间的极低频信号;

45.②

由于外界原因,包括传感器或仪器的零点漂移、基础运动等引起的信号波形偏移;

46.③

在截取记录时,样本长度选择不当;

47.④

由于操作不当,信号经过积分放大后产生趋势项,如零点未调准产生的常数,经积分后成为一条斜直线,低频噪声经积分放大后成为缓慢变化的趋势项。

48.可见产生趋势项的原因是很复杂的,要在实际采集的数据中完全避免趋势项十分困难,在环境激励法测试时,外界影响大,常会有基础运动,而冲击激励又易产生加速度传感器的零点漂移,这是振动传感器的数据中产生趋势项的主要原因。

49.在本发明中,所述趋势项去除单元采用去均值的方式来去除趋势项,具体地,首先计算振动信号的均值,然后将振动信号的时域数据序列中的每个点数据减去均值,从而得到去趋势项后的时域数据序列。可选地,所述趋势项去除单元还可以采用高通滤波的方式对振动信号进行滤波处理,滤除低频成分,也可以在一定程度上提高积分后计算振动有效值的准确性。

50.因此,所述滤波处理模块先对振动信号进行滤波处理,一定程度上滤除噪声信号,防止噪声对振动总量的叠加导致振动总量比实际的高,然后,对滤波后的振动信号进行去趋势处理,可以防止被积函数产生常数值而导致积分后的振动速度信号有趋势项,影响振动有效值。

51.另外,考虑到所述adc采样芯片采集每个单通道振动信号时按40000hz采样频率,根据机载发动机健康监视单元的技术要求s100-jb-0738,振动监测系统应在720ms内完成2路振动传感器信号的采集和处理,频率采集分析范围为100hz~9khz,240hz~3000hz内幅值误差不超过3%,频率误差《1.2hz,其它范围内误差不超过5%,振动信号速度最大测量范围为200mm/s,振动加速度的最大测量范围为500g,因此所述adc采样芯片在720ms内可连续采样数据28800个。而fft变换处理的数据点数理论上应选择以2为基数的整数次方来降低运算时间并提高结果准确性,接近28800的两个可选值分别是32768和16384,分别对应实际采样时间周期819.2ms和409.6ms,而对应819.2ms和409.6ms的频域波形分辨率分别是1.2207hz和2.4414hz。所述滤波处理模块还包括数据截取单元,用于对采样获得的振动时域数据序列进行数据截取,具体地,所述数据截取单元在720ms采集周期的限定下从28800个采样点数据中截取16384个采样点进行后续的快速傅里叶变换,实际频率分辨率为2.4414hz,频率范围为0~20000hz,有效降低了后续数据处理量,提高了计算速度。

52.而即使通过滤波处理模块截取16384个采样点数据,后续处理的数据量仍然较大,计算效率较低。因此,所述重采样模块对经过滤波处理、去除趋势项处理和数据序列截断处理后的振动时域数据序列进行重采样,考虑到需要满足的频率采集分析范围为100hz~9khz,对16384个采样点进行间隔采样获得8192个采样点,频率分辨率为2.4414hz,频率范围为0~10000hz。通过重采样可以降低采样频率,进一步减少了后续处理的数据量,并且有利于进一步消除干扰。

53.所述量纲转换模块通过将每个采样点数据乘以一个转换系数,将电压值转换为振动加速度值,实现从电压信号到物理量的转换。

54.所述加窗处理模块对经过所述量纲转换模块输出的长度为8192的时域数据序列进行加窗处理,具体将长度为8192的时域数据序列与长度为8192的窗函数系数序列逐项相乘,得到长度为8192的加窗时域数据序列。通过在进行fft变换之前对时域数据序列进行加窗处理,可以降低傅里叶变换时信号截断引入的频谱泄露。

55.具体地,所述加窗处理模块采用窗函数法设计的fir数字滤波器,窗函数法具有算

法原理简单、计算速度快、容易实现的优点,fir数字滤波器具有良好的线性特性,采用窗函数法设计的fir数字滤波器的目标是在时域上将设计出的滤波器单位脉冲响应函数尽可能接近理想滤波器单位脉冲响应函数,从而可以有效降低后续fft变换时的频谱泄露。

56.但是在利用fir数字滤波器进行实际振动信号的加窗滤波处理时,滤波后信号将会不可避免地产生明显的时延,因此,为了消除fir数字滤波器的时延问题,本发明进行了优化处理。

57.具体地,fir数字滤波器具有线性相位的充要条件为单位冲激响应序列h(n)必须满足特定的对称性,其相位延迟应等于h(n)长度的一半,即:其中,τ表示相位延迟,n

′

表示滤波器长度,而n=n

′‑

1,n为滤波器的阶数,因此,fir数字滤波器的相位延迟是其滤波器阶数的一半,即:而相位延迟是fir数字滤波器产生时延的最根本原因,二者关系为:δt=τ/fs,其中,δt表示时延,fs表示采样频率。故fir数字滤波器的时延δt与滤波阶数n存在如下关系:δt=n/(2fs)。所述fpga芯片还包括时延消除模块,用于在确定滤波器类型后,基于滤波器的阶数n和采样频率fs计算得到时延大小后,将滤波后的信号波形进行平移变换,从而完全消除滤波器时延的影响。例如,以低通滤波器为例,该滤波器参数设置为截止频率f

stop

=2000hz,采样频率fs=10000hz,滤波器的阶数n设置为500,根据以上公式,即可算出振动信号经过滤波器滤波后所产生的时延大小:δt=n/(2fs)=0.025s,通过舍弃前250个数据点的手段,即可实现滤波信号的波形平移,完全消除的滤波后时延的影响。

58.可选地,所述fir数字滤波器可以采用低通滤波器、高通滤波器、带通滤波器和带阻滤波器中的任一种。但是不同的滤波器需要选用适配的窗函数,窗函数的选择原则是一是主瓣应尽量窄,能量尽可能集中在主瓣内,从而在谱分析时获得较高的频率分辨力,在数字滤波器设计中获得较小的过渡带;二是尽量减少窗谱最大旁瓣的相对幅度,也就是使能量尽量集中在主瓣,这样可使肩峰和波纹减小,增大阻带的衰减,而在实际应用中,上述两项要求是不能同时满足的,例如常通过增加主瓣宽度以换取对旁瓣的抑制。而选用不同形状的窗函数都是为了得到平坦的幅度响应和较小的阻带波纹(也就是加大阻带衰减),因此不同的滤波器需要选用相适配的窗函数。常用的窗函数有矩形窗、三角窗、巴特利特窗、帕曾窗、汉宁窗、海明窗、布莱克曼窗、布拉克曼-哈里斯窗、余弦坡度窗、指数窗、高斯窗等。当所述fir数字滤波器采用低通滤波器时,需要其阻带截止频率f

stop

处的衰减小于阻带衰耗,并选择过渡带较窄(越接近理想频响)的窗函数,而布莱克曼窗的衰减最大,旁瓣峰值最低,所以干扰抑制性能最为稳定,可以充分抑制干扰频谱的旁瓣泄露,布莱克曼窗较宽的过渡带可以通过增加窗口的长度(即滤波器的阶数)来得到改进。当所述fir数字滤波器采用高通滤波器时,同低通滤波器一样也采用布莱克曼窗。当所述fir数字滤波器采用带通滤波器或者带阻滤波器时,考虑到带通滤波器或者带阻滤波器受泄露的影响较大,故采用布拉克曼-哈里斯窗,布拉克曼-哈里斯窗是在布莱克曼窗的基础上进行改进的一种窗函数,不仅具有布莱克曼窗的特性,还可以进一步抑制了旁瓣电平与邻近泄露。

59.可以理解,所述fft变换模块将长度为8192的加窗时域数据序列转换为长度为8192的频域数据序列,而在频域数据序列中只有前4096个点对应实际频谱线,前4096个点

对应转换后的频率有效范围为0~10000hz,频率分辨率为2.4414hz,每个频率点都对应一个复数,后4096个点位实际频谱线的镜像副本,对应于信号的负频率,可忽略不计。

60.所述幅值谱计算模块对频域数据序列中的前4096个频率点复数的实部和虚部的数值进行计算,得到每个频率点的加速度幅值和相位,从而可以得到长度为4096的加速度幅值序列。

61.所述加窗修正模块将长度为4096的加速度幅值序列乘以一个加窗修正系数,从而得到加窗修正后的振动加速度在频域的幅值序列。其中,所述加窗修正系数为一个常系数,由所述加窗处理模块选定的窗函数决定,通过加窗修正模块对振动加速度幅值序列进行加窗修正可以有效降低加窗对振动信号幅值准确性的影响。

62.可以理解,所述dsp处理器上电初始化后周期性读取fpga芯片输出的振动信号频域数据并进行处理,读取周期由fpga芯片决定,fpga芯片处理完振动数据后通过一个与dsp处理器互联的gpio触发dsp处理器的外部硬件中断来通知dsp处理器实现同步,dsp处理器则分别对两个通道加窗修正后的加速度幅值序列进行处理。

63.具体地,如图4所示,所述dsp处理器包括检波模块、发动机转速获取模块、第一计算模块、第二计算模块和振动超限判断模块,所述检波模块与fpga芯片连接,所述发动机转速获取模块与发动机电子控制器连接,所述第一计算模块分别与所述检波模块、发动机转速获取模块连接,所述第二计算模块与所述检波模块连接,所述振动超限判断模块分别与所述第一计算模块、第二计算模块连接。

64.所述检波模块用于采用检波算法识别出加窗修正后的加速度幅值序列中的所有峰值点,即4096个峰值点。根据傅里叶变换的频谱特点可知,每个频率突起中只有峰值点才是真实的频率分量值,其他部分均是频谱泄露的结果,因此只关注峰值点可以起到有效监测振动信号中真实频率成分的作用。可选地,为了降低频谱数据中噪声干扰对信号处理结果的影响,所述检波模块中设定了检波阈值,只有超过阈值的幅值数据才会被检波处理,该检波阈值由振动监测系统无外部振动激励时频域数据中的噪声峰值决定。

65.所述发动机转速获取模块通过串口通信获得发动机的转速,所述第一计算模块根据发动机转速计算得到本次采样周期内的基频和二倍频,并结合加窗修正后的加速度幅值序列获得基频、二倍频对应的振动分量速度幅值。具体地,考虑到频域分辨率为2.4414hz,基频、二倍频正好对应频域幅值谱中的某个频率点的概率很小,因此,所述第一计算模块根据基频、二倍频在加窗修正后的加速度幅值序列中寻找对应的频率点,当基频、二倍频落在两个频率点之间时,取两个频率点的幅值较大者作为该基频/二倍频对应的振动加速度幅值,然后,利用振动加速度幅值计算得到转速对应的基频和二倍频的振动分量速度幅值。

66.所述第二计算模块根据所述检波模块识别出的一个采样周期内的所有峰值点来计算每个峰值点的振动分量速度幅值和振动总量速度幅值,具体先将每个峰值点的振动加速度峰值转换为振动分量速度幅值,然后求所有峰值点的振动分量速度幅值的均方根值,从而得到振动总量速度幅值。

67.所述振动超限判断模块根据计算得到的所有峰值点的振动分量速度幅值、振动总量速度幅值、基频和二倍频的振动分量速度幅值进行振动超限情况判断,识别出振动超限状态并进行记录,需要时还可以进行告警。具体地,所述振动超限判断模块将所有峰值点的振动分量速度幅值、基频和二倍频的振动分量速度幅值、振动总量速度幅值分别与预设阈

值进行比对,其中,振动总量速度幅值的预设阈值为72mm/s,振动分量速度幅值的预设阈值为50mm/s,若某个通道的所有峰值点的振动分量速度幅值、基频和二倍频的振动分量速度幅值和振动总量速度幅值中的任一者超过预设阈值,则判定为振动超限状态,并进行记录。其中,所有峰值点的振动分量速度幅值只要有一个点的振动分量速度幅值超过预设阈值,则判定为振动超限,并记录振动超限对应的振动信号原始时域数据和频域数据。

68.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1