一种PET探测器读出电子学系统

一种pet探测器读出电子学系统

技术领域

1.本技术属于核医学电子学领域,具体涉及一种pet探测器读出电子学系统。

背景技术:

2.目前在pet探测器研发中,使用最广的是闪烁探测器(bgo、lfs、lyso等)和光电探测器。伽马光子在闪烁探测器内所产生的闪烁光无法被电子学系统探测到,因此在闪烁探测器上都会耦合光电探测器,如光电倍增管pmt。由于半导体工艺的发展,近年来pmt渐渐被硅光电倍增管sipm所替代。与pmt相比,sipm具有更小的偏压、对磁场不灵敏、能量分辨高等特点。电子学读出系统是pet系统的另一个核心部分。传统的pet电子学读出系统,电路结构不仅复杂而且庞大,给高端医疗设备的集成带来了巨大挑战。虽然芯片技术的快速发展,使得pet电子学读出系统渐渐转向专用集成电路asic,使其朝着低功耗、低噪声、小型化、高通道密度的方向发展,但是研发周期过长和投入资金量大限制了这种技术大面积的应用。

技术实现要素:

3.基于上述问题,本技术提供一种高通道密度、小型化的pet探测器读出电子学系统,其技术方案为,

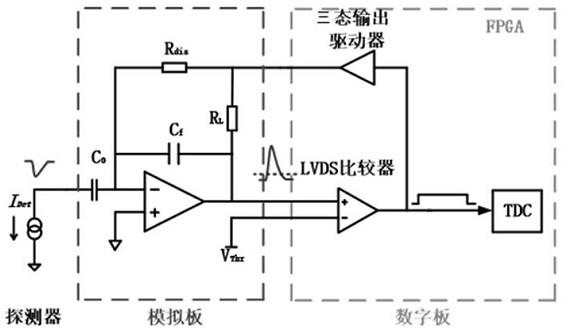

4.一种pet探测器读出电子学系统,包括放电系统和比较系统,所述放电系统包括放大器、放电电阻r

dis

、电容cf和电阻r

l

,所述放大器负输入端分别接电容c0、电阻r

dis

和电容cf,放大器输出端分别接电容cf、电阻r

l

和比较系统的lvds比较器的正输入端,所述电阻r

l

分别与电容cf、放电电阻r

dis

和比较系统的三态输出驱动器连接;

5.所述比较系统包括lvds比较器和三态输出驱动器,lvds比较器的负输入端接v

thr

,lvds比较器的输出端接三态输出驱动器,所述放大器正输入端接地或接v

stage

。

6.优选的,所述放电系统至少一组,通过对应的电容c0阵列接外部探测器,所述放电系统和电容c0阵列安装在模拟板上,所述模拟板上还设有fh12系列接插件和st4系列接插件。

7.优选的,所述比较系统数量与放电系统匹配,比较系统安装在数字板上,所述数字板上还设置io引脚、ss4系列接插件、fpga、串口芯片、mini-display接口、线性电源模块和高精度时钟芯片,所述fpga分别与三态输出驱动器、线性电源模块、ss4系列接插件连接,模拟板和数字板通过st4系列插件、ss4系列插件进行相连。

8.优选的,lvds比较器负向输入端与lt3080芯片的输出连接, lt3080芯片设置在数字板上。

9.有益效果

10.本实用新型提出了一种小型化、低成本、可快速定制的多通道pet探测器读出电子学解决方案,该设计方案集成度高,可同时实现对多路sipm输出信号的测量,同时兼备正、负双极性信号的提取功能,可以极大地加快pet探测器地研发速度、降低读出电子学地研发成本。

附图说明

11.图1为基于fpga的电荷数字转换器qdc负电荷测量原理图。

12.图2为基于fpga的电荷数字转换器qdc正电荷测量原理图。

13.图3为在负电流脉冲输入情况下的fpga-qdc各点的波形图。

14.图4双层交叠式设计中的模拟板。

15.图5双层交叠式设计中的数字板。

16.图6单个8x8像素型sipm探测器配置成行列互连型的原理图。

17.图7 2x2个8x8像素型sipm探测器配置成行列互连型的原理图。

具体实施方式

18.本实用新型所采用的技术方案是使用两套pcb电路板来实现64路fpga-qdc电子学测量通道,分为模拟板和数字板,以实现小型化、低成本、低功耗的pet探测器读出电子学设计。模拟板上设置放电系统、数字板上设有比较系统和fpga。

19.模拟板包括fpga-qdc技术的放电系统和接插件,包括hirose公司的高密度fh12系列接插件、ad公司的高性能4通道放大器ada4891-4、samtec公司的板级高密度st4系列接插件、耦合电容c0阵列、放电电阻r

dis

、积分电容cf、负载电阻r

l

。板级布局如图4所示。 所述放电系统包括放大器、电阻r

dis

、电容cf和电阻r

l

,所述放大器负输入端分别接电容c0、电阻r

dis

和电容cf,放大器输出端分别接电容cf、电阻r

l

和比较系统的lvds比较器的正输入端,所述电阻r

l

分别与电容cf、电阻r

dis

和比较系统的三态输出驱动器连接。

20.所述fh12高密度接插件用于电子学与外部sipm探测器输出的弱电信号连接;

21.所述放大器对来自探测器的电流脉冲信号进行积分和恒流放电,完成了总电荷向放大器输出电压脉宽的转换;

22.所述的st4系列接插件实现了与数字板的信号互联;

23.所述的电容c0阵列实现了对探测器电流脉冲的交流耦合(此电容c0阵列可以称为交流耦合电容c0阵列),防止sipm的偏置电压加到读出电子学系统中,实现了对前端电路的保护;

24.所述的放电电阻r

dis

用于实现恒流放电功能;

25.所述的电容cf用于实现对探测器电流信号的积分功能,实现对弱电流信号的放大。

26.数字板采用10层设计,数字板包括fpga-qdc技术的比较系统、接插件以及供电电源,有samtec公司的板级高密度接插件ss4系列接插件、cyclone v fpga、串口芯片、mini-display接口、若干线性电源模块、高精度时钟芯片。板级布局如图5所示。

27.所述比较系统包括lvds比较器和三态输出驱动器,lvds比较器的负输入端接v

thr

,lvds比较器的输出端接三态输出驱动器,所述放大器正输入端接地或接v

stage

。

28.板级ss4接插件用于连接放大器积分后的电压信号,所有的信号均连接到lvds比较器差分引脚的正向端;

29.所述的fpga完成的功能有:用lvds比较器接口实现电压比较器的功能;用计数器对lvds比较器输出的数字信号脉宽进行计数;实现uart波特率产生、串口收发数据、数据分组的功能;实现sipm探测器通道和电子学通道的通道重映射;实现sipm探测器数据的缓存

功能。

30.串口芯片用于完成uart到usb数据的转换,用于配置以及调试信息的输出,串口芯片采用8250。

31.所述的mini-display接口包含4对高速收发lvds比较器的电压信号和1对lvds比较器的时钟信号,用于实现时钟同步和高速数据传输,其中,时钟信号连接到fpga专用的差分时钟输入引脚,所有lvds比较器没有额外的外部电阻网络;

32.所述的若干线性电源模块用于实现fpga供电所需的电源1.1v、1.8v、2.5v、3.3v和0v,以及放大器所需要的比较电压(低阈值和高阈值),fpga所有的供电电源由4个tps74401芯片实现,阈值由两个lt3080芯片实现。

33.所述的高精度时钟芯片与fpga的差分时钟输入引脚相连,用于提供fpga的200m全局时钟。

34.本技术双层交叠式设计,使得板级尺寸小于70 x 70 mm2。板级的供电电源为+5v和-1v,其余所需的低压电源均由电源芯片降压得到。数字板和模拟板的供电电源通过st4系列接插件/ss4系列接插件进行互联。fpga配置芯片采用epcs64系列专用配置芯片,同时引出jtag调试接口和as烧写接口。在数字板上的fpga-qdc方法中,所有的阈值电平均连接到lvds比较器差分引脚的负向端,实现输入信号与阈值电平的比较。对于lvds比较器,其动态范围是0v~2.5v,设置的放电电压等于fpga的bank电压,即2.5v。

35.本实用新型采用最新的fpga-qdc技术,采用最少的分立元件和放大器实现了小型化、低噪声、低成本的信号测量电子学。本实用新型可以同时实现对正/负电荷进行测量,以负电荷测量为例,如图1所示,当没有入射的511kev伽马光子的时候,闪烁体没有产生闪烁光,因此sipm探测器也没有产生电流脉冲信号;放大器的输出基线为地电平(理论上是0 v),由于v

thr

略大于地电平,因此,此时lvds比较器输出为逻辑

‘0’

;而当lvds比较器输出为逻辑

‘0’

的时候,三态输出驱动器输出为高阻

‘

hz’态,相当于断开;因此在没有输入电流脉冲的情况下,放大器、电容cf、电阻r

dis

和电阻r

l

构成了泄放时间常数τ为(r

dis

+r

l

)cf的电荷灵敏放大器;当有伽马光子击中闪烁体,耦合的sipm探测器将会产生电流脉冲(假设总电荷量为q),sipm探测器的输出电荷信号q首先在电容cf上进行积分,积分后的电压信号和指定的直流阈值电平v

thr

一起送入lvds比较器,当放大器输出的电压信号大于阈值电平时,lvds比较器输出逻辑

‘1’

;而当lvds比较器输出逻辑为

‘1’

的时候,三态输出驱动器此时由高阻态变为高电平,通过fpga对应的i/o bank供电电压v

io

(此例中是2.5v)和放电电阻r

dis

对电容cf上积分的电荷进行恒流放电,放电电流i

dis = v

io

/r

dis

,为恒定值,而放电总时间t=q/i

dis

,因此,放电脉冲的宽度t正比于输入的电荷量q;而在恒流放电阶段,电阻r

l

只作为放大器的负载。

36.放电脉冲的前沿其实也代表了电荷的到达时间。图3显示了典型的放电波形,在图3中,波形1表示了在没有恒流放电情况下,即模拟电路工作在电荷灵敏放大模式下的波形;波形2表示的是在fpga-qdc原理下放大器输出的模拟放电波形;波形3表示的是三态输出驱动器输出的放电脉冲信号。由于放大器输出的模拟放电波形有一段线性区,所以也把这种电荷测量方法称为“线性放电qdc”。

37.图2,就正电荷测量原理简述如下:在sipm探测器没有输出信号的情况下,由于在放大器的正向端引入了v

stage

电压,本例中是2.5v,因此放大器的输出基线为v

stage

;阈值v

thr

略小于v

stage

,lvds比较器在没有输入电流信号的情况下输出逻辑

‘1’

;而在lvds比较器输出逻辑是

‘1’

的情况下,三态输出驱动器输出为高阻

‘

hz’态;而当sipm探测器有输出电流脉冲信号的时候,放大器输出负向的电压脉冲波形,当此负向波形电压值小于v

thr

时,lvds比较器输出由逻辑

‘1’

变为逻辑

‘0’

,而三态输出驱动器的输出则由高阻态变为地电平(理论上为0v),此时开始恒流放电。

38.无论是正电荷测量还是负电荷测量,fpga-qdc技术需要一片低端的fpga,只要其包括足够的lvds比较器和io引脚,即可以实现高密度、低花费、低噪声的电子学系统。为了实现小型化的设计,本实用新型采用了双层交叠结构的硬件设计,将模拟部分和数字部分在两套pcb板上进行设计,降低板级尺寸。

39.本实用新型共有64个电子学读出通道,用于接收pet探测器的正/负电流脉冲信号。输入的64路信号在模拟板上首先经过4个fh12接插件进行分组,每组16个信号。每个fh12连接器的16路信号接着进入fpga-qdc的16个模拟放大器分别进行积分。

40.模拟板和数字板通过高密度st4系列接插件/ss4系列接插件进行相连。放大器积分后的信号通过此接插件送入fpga的lvds接收器,此时lvds接收器作为电压比较器使用。积分后的电压信号与指定的阈值电压v

thr

进行比较,每路的lvds接收器输出对应的逻辑值:正电荷测量电路输出逻辑

‘1’

,负电荷测量电路输出逻辑

‘0’

,以此驱动三态输出驱动器。此后得到的数字脉冲用时间数字转换器tdc进行测量其宽度和前沿信息。

41.如果只要电荷信息,则tdc使用粗时间计数器进行测量;如要得到信号的到达时间,使用基于进位链的高精度tdc进行测量。

42.在供电设计中,模拟板上的电源由数字板提供,因此整套64通道电子学只需要+5v和-1v外部电源。数字板上fpga所需要的io引脚电压、pll供电电压、内核电压均由tps74401线性电源通过降压得到。正/负电荷测量所需要的两个阈值(0或2.5v)分别由lt3080通过降压得到。

43.在模拟板上放大器的正向输入端通过st4系列接插件/ss4系列接插件连接到数字板上fpga的io引脚上,由于fpga的io引脚是可配置的,其中两个引脚配置为0v和2.5v,所以每一路读出电子学通道都可以通过fpga的io引脚来将fpga-qdc电路配置成正电荷测量或者负电荷测量,以此增加了电子学系统的灵活性。当所有放大器正向端接通到fpga的io引脚0v时, 对应图1的负电荷测量原理;当所有放大器正向端接通到fpga的io引脚2.5v时,对应图2的正电荷测量原理。

44.以单个8x8像素型sipm探测器为例,探测器的行列互联结构如图6所示。每行的阴极信号连在一起,相当于对每一行的电流信号求和;每一列的阳极信号连接在一起,相当于对每一列的电流信号进行求和。由于sipm探测器工作在反偏的条件下,因此阳极输出的是正向电流脉冲,而阴极输出的是负向电流脉冲。在行列互联求和的配置下,64个像素的探测器只需要8个负电荷测量通道和8个正电荷测量通道。对于本实用新型64通道fpga-qdc电子学来说,只需要一个fh12接口进行连接即可,将对应的通道设置成正或者负电荷测量通道。

45.再者,可以对图6的连接结构进行扩展,以2x2个8x8 sipm探测器为例,优化的行列互联结构如图7所示,每行sipm的阴极连接在一起,形成16个阴极行信号;每列sipm的阳极连接在一起,形成16个阳极信号。在2x2个sipm探测器的行列互联配置下,256个像素只需要16个负电荷测量通道和16个正电荷测量通道,本实用新型的2个fh12接口进行连接测量即

可。如要构成紧凑型pet探测器,采用2x2个闪烁体阵列和双端读出,本实用新型的64个通道全部连接,可以获得pet探测的晶体鉴别图、能量分辨率、作用深度。同时利用参考探测器可测量pet探测器的定时功能。因此,本实用新型具有很强的灵活性,对于不同配置的pet探测器均可测量。

46.基于同样原理可实现128通道、256通道、512通道等的扩展。

47.以上所述仅为本技术的优选实施例而已,并不用于限制本技术,对于本领域的技术人员来说,本技术可以有各种更改和变化。凡在本技术的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1