一种基于FPGA的贴片机控制装置的制作方法

一种基于fpga的贴片机控制装置

技术领域

1.本实用新型涉及贴片机控制技术领域,特别涉及一种基于fpga的贴片机控制装置。

背景技术:

2.贴片机是工业生产自动化领域一个重要的工业机器,贴片机需要多个相对独立的子模块协同工作完成贴片功能。为了提高贴片机的工作效率、可靠性,同时保持一定的灵活性,要求控制系统具有并行化工作,可靠性高,灵活性高等特点。

3.集成电路的焊接是现代工业体系最基础的工艺之一,传统的手工焊接存在焊接时间长、精度低、可靠性差、成本高等一系列缺点。为了克服这些困难,专用的自动化焊接技术已经在焊接领域得到了大规模的应用。贴片机就是自动化焊接技术中最重要的机器之一。贴片机通常需要供料模块、xy轴移动模块、z轴移动模块、pcb传送模块、机器视觉模块、吸嘴交换站等多个子模块协同工作才能完成一个完整的贴片流程,因此利用一个中央控制系统来协调各个模块的工作是十分必要的。

4.现有的贴片机控制系统设计中,通常采用基于cpu的工控机完成系统控制。操作系统工作于工控机中,完成系统控制的主控软件工作于操作系统之上。主控软件通过操作系统调用工控机的硬件完成子模块指令下发以及状态查询,根据整机状态完成整机动作。

5.但是,cpu的工作方式为串行工作,采用时间分片的技术完成对不同子模块状态的轮询,状态检测,并根据状态完成整机动作。主控软件运行在操作系统之上,存在系统调用的时间,以及操作系统不稳定等潜在风险点。

技术实现要素:

6.本实用新型的目的在于克服现有技术存在的缺陷,实现并行化同时与贴片机所有子模块进行信息交互。

7.为实现以上目的,本实用新型采用一种基于fpga的贴片机控制装置,包括fpga处理器、rs485控制芯片、pcie传输模块和存储模块,rs485控制芯片、pcie传输模块和存储模块均与fpga处理器连接进行双向通信,rs485控制芯片与贴片机各子模块连接,pcie传输模块与 cpu连接。

8.进一步地,所述存储模块包括用于存储所述贴片机机器参数的flash 存储单元和用于存储动作流程的ddr3单元。

9.进一步地,所述rs485控制芯片包括8路结构相同的串行数据传输通道。

10.进一步地,所述rs485控制芯片包括电平转换芯片,电平转换芯片的485_txd1、485_rxd1及485_en引脚连接至所述fpga处理器的 i/o引脚,电平转换芯片的引脚a端和b端之间连接有共模滤波电感,上拉电阻与一滤波电容并联后连接在引脚a端和共模滤波电感之间,下拉电阻与另一滤波电容并联后连接在引脚b端和共模滤波电感之间,共模滤波电感与所述各子模块连接进行信息交互。

11.进一步地,所述pcie传输模块包括用于通知计算机贴片机控制系统的状态发生变化的msi中断通道和用于下发命令并回读执行状态的基于基地址寄存器的控制通道。

12.进一步地,所述pcie传输模块采用pcie 3.0lane

×

4接口,refclk 引脚为所述cpu向所述fpga处理器提供pcie接口的差分参考时钟; perst_n引脚为所述cpu向所述fpga处理器提供pcie接口的复位信号;rx_p/n[3:0]引脚为所述cpu向所述fpga处理器传输差分数据信号;tx_p/n[3:0]引脚为所述fpga处理器向所述cpu传输差分数据信号。

[0013]

与现有技术相比,本实用新型存在以下技术效果:采用fpga硬件实现的方式完成贴片机整机状态查询与动作控制,可并行化同时与贴片机所有的子模块进行指令、状态交互,状态判断以及贴片机实时状态记录,响应快,且控制逻辑基于fpga硬件电路实现,可靠性高。

附图说明

[0014]

下面结合附图,对本实用新型的具体实施方式进行详细描述:

[0015]

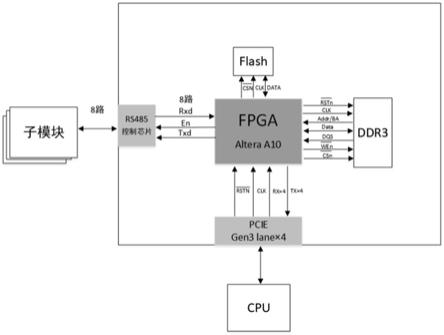

图1是一种基于fpga的贴片机控制装置的结构图;

[0016]

图2是rs485接口电路图;

[0017]

图3是pcie插槽的引脚图;

[0018]

图4是动作流程控制结构框图。

具体实施方式

[0019]

为了更进一步说明本实用新型的特征,请参阅以下有关本实用新型的详细说明与附图。所附图仅供参考与说明之用,并非用来对本实用新型的保护范围加以限制。

[0020]

如图1所示,本实施例公开了一种基于fpga的贴片机控制装置,包括:fpga处理器、rs485控制芯片、pcie传输模块和存储模块,rs485控制芯片、pcie传输模块和存储模块均与fpga处理器连接进行双向通信,rs485控制芯片与贴片机各子模块连接,pcie传输模块与cpu连接。

[0021]

其中,多通道rs485控制芯片包含8路结构相同的串行数据传输通道,每路485的工作速率为10mbps,用于和贴片机各子模块之间完成指令交互与状态交互,485工作模式为主从模式,贴片机控制装置工作在主模式,子模块工作在从模式。pcie传输模块用于通过基地址寄存器 (bar)完成贴片机控制装置与运行在cpu中的主控软件之间的数据交互,该主控软件可采用现有软件实现。现有技术通常采用cpu直接控制子模块的方式进行;本实施例通过cpu将动作流程下发给贴片机控制装置,由控制装置中的fpga处理器完成整机状态检测、动作流程控制。在子模块查询过程中,现有技术通常采用cpu分时进行轮询,速度慢, cpu占用率高;本实施例采用fpga进行并行轮询,效率高速度快。

[0022]

作为进一步优选的技术方案,所述存储模块包括用于存储所述贴片机机器参数的flash存储单元和用于存储动作流程的ddr3单元。

[0023]

作为进一步优选的技术方案,如图2所示,所述rs485控制芯片包括电平转换芯片thvd2450dr,电平转换芯片的485_txd1、485_rxd1 及485_en引脚连接至所述fpga处理器的i/o引脚,电平转换芯片的引脚a端和b端之间连接有共模滤波电感,上拉电阻与一滤波电容并联后连接在引脚a端和共模滤波电感之间,下拉电阻与另一滤波电容并联后连接在引脚b

端和共模滤波电感之间,共模滤波电感与所述各子模块连接进行信息交互。

[0024]

本实施例通过在接口处,集成了dr33a

‑

105be共模滤波电感,120 欧匹配电阻,上/下拉电阻,以及滤波电容,可以有效的过滤掉空间电磁波干扰,提高通信稳定性。

[0025]

作为进一步优选的技术方案,如图3所示,所述pcie传输模块的refclk引脚为所述cpu向所述fpga处理器提供pcie接口的 100mhz差分参考时钟;perst_n引脚为所述cpu向所述fpga处理器提供pcie接口的复位信号;rx_p/n[3:0]引脚为所述cpu向所述 fpga处理器传输差分数据信号;tx_p/n[3:0]引脚为所述fpga处理器向所述cpu传输差分数据信号,链路速率为8gbps;12v与gnd 为贴片机控制装置提供电源,链路速率为8gbps。

[0026]

作为进一步优选的技术方案,pcie传输模块使用pcie 3.0lane

×

4 接口,最大传输带宽3.94gb/s。该模块包含两条通信地址,第一条为 msi中断通道,用于通知计算机贴片机控制系统的状态发生变化,第二条为基于基地址寄存器(bar)的控制通道,通过寄存器的方式下发命令并回读执行状态。

[0027]

如图4所示,本实施例中基于fpga的贴片机控制装置的工作流程为:

[0028]

(1)cpu通过pcie接口模块将贴片机动作指令下发给fpga处理器,由fpga处理器在本地完成缓存,包括cpu将贴片机机器参数(如机台长宽、速度限制、位置限制、电流限制等)通过pcie接口基地址寄存器通道下发给fpga处理器,由fpga处理器将参数存储在flash 存储模块中;cpu将需要完成的动作流程通过pcie链路基地址寄存器控制通道下发到fpga处理器,fpga处理器将动作流程缓存在ddr3 存储模块中。

[0029]

(2)fpga处理器通过485接口模块并行地完成各个子模块的状态查询。

[0030]

(3)fpga处理器根据查询到的整机状态,将整机动作指令下发到子模块,控制子模块完成响应的动作。

[0031]

(4)fpga处理器记录子模块的执行状态,例如传感器状态、电流、电压、电机位置、动作时间等参数,记录在贴片机控制装置缓存中,并通知cpu读取参数。

[0032]

以上所述仅为本实用新型的较佳实施例,并不用以限制本实用新型,凡在本实用新型的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本实用新型的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1