一种基于ZYNQ的捷变频多功能通用基带处理装置的制作方法

一种基于zynq的捷变频多功能通用基带处理装置

技术领域

1.本发明涉及测控通信技术领域,尤其涉及一种基于zynq的捷变频多功能通用基带处理装置,可用于运载火箭测控单机的地面测试。

背景技术:

2.近年来随着我国运载火箭发射任务的密集化以常态化,传统的外安系统地面测试设备缺点日益显现,主要有通用化程度差、系统构成复杂、成本高、笨重等缺陷,因此作为新型通用化地面测试设备的一部分,一种基于zynq的捷变频多功能通用基带处理装置应运而生。

3.专利号:201821180718.3,发明人:杨松楠、张鹏泉、范玉进、张晶、禄姗姗,专利名称:一种基于zynq的多通道无线信号采集设备,提出了一种基于zynq的多通道无线信号采集设备,该专利采用fpga+zynq协同工作的架构对多路adc进行无线信号采集,其采样率为112mhz,且不具备产生调制信号的功能,其功能单一不具备一定的通用性,与本发明有较大区别。

4.专利号:202023068307.5,发明人:张勇军、蔡朝锋、黎明林、朱英柏、高红丽、杨立,专利名称:一种小型化低功耗多通道软件无线电平台,提出了基于一种小型化低功耗多通道软件无线电平台,该软件无线电平台也属于基于zynq的发明,其工作频段为100khz~3800mhz,与本发明相比频率范围较窄,且其不支持网口通信及cpci通信,与本发明相比其使用场景上也有所区分,同时本发明还支持高速adc采集及ttl输出及多种串口通信功能,可插入支持3u卡槽cpci通信规范的工控机箱。

5.专利号:201920277064.4,发明人:张更新,专利名称:一种基于ad9361多路频谱分析嵌入式硬件平台,提出了一种基于ad9361多路频谱分析嵌入式硬件平台,该发明实现了三组基于ad9361的收发通道,而本发明是基于ad9364实现的两组收发通道与本方案有所区分,其次ad9361由于通道集成度较高,其通道间隔离度较低,此外其方案架构采用fpga+zynq协同工作的架构,与本方案相比工作场景有所区别,系统构成有一定的差异。

6.综上所述,现有的外安系统地面测试设备缺点日益显现,主要有通用化程度差、系统构成复杂、成本高、笨重等缺陷。

技术实现要素:

7.本发明的目的是提供一种基于zynq的捷变频多功能通用基带处理装置。

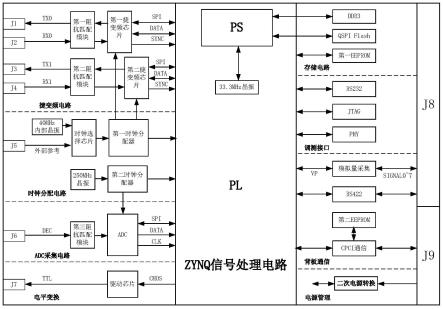

8.本发明所提供的一种基于zynq的捷变频多功能通用基带处理装置,包括:与zynq信号处理电路分别电连接的捷变频电路、时钟分配电路、adc采集电路、电平变换电路、存储电路、调测接口、背板通信电路、电源管理电路、面板连接器,其中:

9.所述捷变频电路包括第一捷变频芯片、第二捷变频芯片、第一阻抗匹配模块及第二阻抗匹配模块;所述第一阻抗匹配模块一端与所述第一捷变频芯片的一端双向连接,所述第一阻抗匹配模块的另一端产生收发信号,并分别与所述面板连接器对应端口连接,所

述第一捷变频芯片的另一端与所述zynq信号处理电路电连接;所述第二阻抗匹配模块一端与所述第二捷变频芯片的一端双向连接,所述第二阻抗匹配模块的另一端产生收发信号,并分别与所述面板连接器对应端口连接,所述第二捷变频芯片的另一端与所述zynq信号处理电路电连接;

10.所述时钟分配电路包括40mhz内部晶振、250mhz晶振、时钟选择芯片、第一时钟分配器和第二时钟分配器;所述40mhz晶振和通过所述面板连接器输入的40mhz外部参考信号通过所述时钟选择芯片进行2选1电路输出1路信号,将输出的1路信号与所述第一时钟分配器的输入端电连接,所述第一时钟分配器的输出端输出第一分路信号,所述第一分路信号分别分配至所述捷变频电路和所述zynq信号处理电路;所述250mhz晶振与所述第二时钟分配器电连接,通过所述第二时钟分配器进行分路并输出第二分路信号,所述第二分路信号分别输出至所述adc采集电路和所述zynq信号处理电路;

11.所述adc采集电路包括第三阻抗匹配模块及adc模数转换器;模拟信号经过所述面板连接器对应端口与所述第三阻抗匹配模块电连接,并经过所述第三阻抗匹配模块将所述模拟信号送给所述adc模数转换器进行数据采集,所述adc模数转换器采集的数据通过所述zynq信号处理电路进行接收和处理;

12.所述电平变换电路包括驱动芯片,所述驱动芯片两端分别与所述面板连接器对应端口和所述zynq信号处理电路电连接;

13.所述zynq信号处理电路包括zynq芯片和33.3mhz晶振,所述zynq芯片包括pl端和ps端,所述33.3mhz晶振与所述ps端连接;

14.所述存储电路包括ddr3、qspi flash、第一eeprom,所述ddr3和所述qspi flash与所述zynq信号处理电路ps端连接,所述第一eeprom与所述zynq信号处理电路pl端连接;

15.所述调测接口包括rs232串口、jtag调试接口、phy千兆以太网接口,所述rs232串口、所述jtag调试接口、所述phy千兆以太网接口与所述zynq信号处理电路ps端连接;

16.所述背板通信电路包括模拟量采集电路、rs422串口、cpci通信电路、第二eeprom,所述模拟量采集电路、rs422串口、cpci通信电路均与所述面板连接器对应端口及zynq信号处理电路pl端连接,所述第二eeprom与cpci通信电连接;

17.所述电源管理电路包括二次电源转换器,所述二次电源转换器两端分别与所述zynq信号处理电路和所述面板连接器对应端口连接。

18.优选地,所述装置为板卡结构,通过cpci总线接口与上位机进行通信,完成模块的高效数据传输和控制,所述cpci总线接口的外形尺寸与单槽3u板卡相适配。

19.优选地,所述捷变频芯片采用ad9364。

20.优选地,所述第一时钟分配器、第二时钟分配器均采用芯片为adclk846bcpz。

21.优选地,所述adc芯片采用ad9434。

22.优选地,所述驱动芯片为sn74ahc1g04。

23.优选地,所述zynq芯片为xc7z100-2ffg900i。

24.优选地,所述面板连接器包括第一端口、第二端口、第三端口、第四端口、第五端口、第六端口、第七端口、第八端口、第九端口,所述第一端口、所述第二端口、所述第三端口、所述第四端口分别设置在所述捷变频电路中并位于板卡前面板,所述第五端口设置在所述时钟分配电路中并位于板卡前面板,所述第六端口设置在所述adc采集电路中并位于

板卡前面板,所述第七端口设置在所述电平变换电路中并位于板卡前面板;所述第八端口和所述第九端口位于板卡后面板。

25.优选地,所述面板连接器的第一端口、第二端口、第三端口、第四端口、第五端口、第六端口、第七端口均为smp-jwhd半擒纵型射频连接器。

26.优选地,所述面板连接器的第九端口为j15022101型连接器。

27.与现有技术相比,本发明具有如下的有益效果:

28.本发明所述的一种以zynq芯片为核心处理器的捷变频通用基带处理装置,集成了传统地面测试设备中多种板卡,如示波器卡、串口卡、信号源卡等,实现了设备的重量缩减,配合射频模块可实现p/l/s/c/x等多种波段测控单机的地面测试功能,具备一定的通用化组合化优势,该装置可通过cpci接口与上位机进行通信,完成模块的高效数据传输和控制。基于其通用化优势可大大缩减设备的开发时间,简化了设备的复杂度。该基带处理装置可通过cpci总线接口按照cpci规范与上位机通信,且总线接口模块的外形尺寸符合标准的单槽3u板卡要求。

附图说明

29.图1为本发明实施例中所述基于zynq的捷变频多功能通用基带处理装置的原理框图。

具体实施方式

30.为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

31.本发明所提供的一种基于zynq的捷变频多功能通用基带处理装置,包括:与zynq信号处理电路分别电连接的捷变频电路、时钟分配电路、adc采集电路、电平变换电路、存储电路、调测接口、背板通信电路、电源管理电路、面板连接器,本实施例中,本装置为一种以zynq芯片为核心处理器的捷变频通用基带处理卡,集成了传统地面测试设备中多种板卡,如示波器卡、串口卡、信号源卡等,实现了设备的重量缩减,配合射频模块可实现p/l/s/c/x等多种波段测控单机的地面测试功能,具备一定的通用化组合化优势,该板卡可通过cpci接口与上位机进行通信,完成模块的高效数据传输和控制。基于其通用化优势可大大缩减设备的开发时间,简化了设备的复杂度。该基带处理卡可通过cpci总线接口按照cpci规范与上位机通信,且总线接口模块的外形尺寸符合标准的单槽3u板卡要求。本实施例中采用的一种基于zynq的捷变频多功能通用基带处理卡可插于工控机箱中,占用空间大小为3u单槽,上位机可配合驱动软件与zynq片上软件进行通信,实现板卡功能的配置及操作。

32.其中:

33.所述捷变频电路包括第一捷变频芯片、第二捷变频芯片、第一阻抗匹配模块及第二阻抗匹配模块;所述第一阻抗匹配模块一端与所述第一捷变频芯片的一端双向连接,所述第一阻抗匹配模块的另一端产生收发信号,并分别与所述面板连接器对应端口连接,所述第一捷变频芯片的另一端与所述zynq信号处理电路电连接;所述第二阻抗匹配模块一端

与所述第二捷变频芯片的一端双向连接,所述第二阻抗匹配模块的另一端产生收发信号,并分别与所述面板连接器对应端口连接,所述第二捷变频芯片的另一端与所述zynq信号处理电路电连接;所述第一捷变频芯片、第二捷变频芯片与所述第一阻抗匹配模块、第二阻抗匹配模块链接,产生两收两发信号连接面板连接器(j1~j4),所述第一捷变频芯片、第二捷变频芯片通过与所述zynq信号处理电路连接,并通过其进行配置及信号处理;所述捷变频芯片采用ad9364。

34.本领域技术人员可以理解,所述捷变频电路与zynq信号处理电路连接,并通过进行zynq信号处理电路配置;所述捷变频电路采用adi公司的ad9364捷变频芯片,工作频率为70mhz至6ghz,支持200khz至56mhz的通道带宽,芯片采用零中频架构,将整个射频以及中频信号电路集成在一个芯片中,包括射频放大器、模拟滤波器、混频器、解调器、12位adc和dac的rf2

×

2收发器,具有较高的可编程能力,且可实现较高的调制精度和较低的噪声。所述捷变频电路通过zynq信号处理电路的ps端进行参数配置,并通过所述zynq信号处理电路的pl端实现捷变频电路两路收发信号的调制及解调,两路收发信号经阻抗匹配网络阻抗匹配到50ω与前面板smp-jwhd型射频连接器连接。

35.所述时钟分配电路包括40mhz内部晶振、250mhz晶振、时钟选择芯片、第一时钟分配器和第二时钟分配器;所述40mhz晶振和通过所述面板连接器j5输入的40mhz外部参考信号通过所述时钟选择芯片进行2选1电路输出1路信号,将输出的1路信号与所述第一时钟分配器的输入端电连接,所述第一时钟分配器的输出端输出第一分路信号,所述第一分路信号分别分配至所述捷变频电路和所述zynq信号处理电路;所述250mhz晶振与所述第二时钟分配器电连接,通过所述第二时钟分配器进行分路并输出第二分路信号,所述第二分路信号分别输出至所述adc采集电路和所述zynq信号处理电路;所述第一时钟分配器、第二时钟分配器均采用芯片adclk846bcpz。

36.本领域技术人员可以理解,所述时钟分配电路,一方面完成内外参考时钟的选择功能,即通过时钟选择电路在需要外部参考的情况下由上位机控制zynq信号处理电路进行外时钟切换,在切换至外时钟的同时控制内部40mhz晶振使能引脚使之处于无效状态,这样一来避免了板卡工作时的同频时钟干扰。内外时钟通过二选一之后将给到时钟分配器,由时钟分配器分成三路:分别提供给两个ad9364模块及zynq信号处理电路,所述二选一芯片为adg772bcpz;另一方面,电路中250mhz参考晶振通过时钟分配器分成两路分别提供给adc采集电路及zynq信号处理电路,adc采集电路的250mhz的采样率可以使采集电路每4ns得到一个采样点,其优势是可以得到较高的信号处理精度,例如:可达效果是有利于提高对脉冲信号上升沿时间及下降沿时间的测量精度。

37.所述adc采集电路包括第三阻抗匹配模块及adc模数转换器;模拟信号经过所述面板连接器对应端口j6与所述第三阻抗匹配模块电连接,并经过所述第三阻抗匹配模块将所述模拟信号送给所述adc模数转换器进行数据采集,所述adc模数转换器采集的数据通过所述zynq信号处理电路进行接收和处理;所述adc芯片为ad9434。

38.所述电平变换电路包括驱动芯片,所述驱动芯片两端分别与所述面板连接器对应端口j7和所述zynq信号处理电路电连接;所述驱动芯片为sn74ahc1 g04。本领域技术人员可以理解,所述电平变换用于实现将zynq信号处理电路pl端的一路i/o口由cmos电平转换为ttl电平,其主要作用为产生高低电平信号或脉冲信号,可达效果是上升沿时间不超过

80ns,下降沿时间不超过100ns,可用作开关或产生pwm信号。

39.所述zynq信号处理电路包括zynq芯片及33.3mhz晶振,所述zynq芯片包括pl端(fpga)和ps端(arm),支持在ps端运行嵌入式linux操作系统,所述33.3mhz晶振与ps端连接;所述zynq芯片为xc7z100-2ffg900i。

40.本领域技术人员可以理解,所述zynq信号处理电路包括zynq芯片及33.3mhz晶振,所述zynq芯片包括pl端(fpga)和ps端(arm),其中ps端在软件开发模式上与标准的arm开发一样,可以运行linux操作系统,pl端的快速高效的并行处理能力,可以实现信号高速并行处理,同时pl具备强大的接口扩展能力,能实现多种普通及高速接口设计。所述33.3mhz晶振与ps端连接,为ps端提供全局参考时钟。

41.所述存储电路包括ddr3、qspi flash、第一eeprom,所述ddr3和所述qspi flash与所述zynq信号处理电路ps端连接,所述第一eeprom与所述zynq信号处理电路pl端连接;其中所述ddr3芯片容量为4gb、所述qspi flash存储器容量128mb、所述第一eeprom容量为16kb,所述ddr3为zynq信号处理电路的ps端提供4gb数据缓存能力,所述qspi flash为zynq信号处理电路的ps端提供128mb软件运行内存,所述第一eeprom用于存储系统配置文件,启动时加载存储配置。

42.所述调测接口包括rs232串口、jtag调试接口、phy千兆以太网接口,以上接口均通过jl24-20zjb直插式连接器引出,可用于板卡的软件调试及软件固化。所述rs232串口、所述jtag调试接口、所述phy千兆以太网接口与所述zynq信号处理电路ps端连接;其中所述串口芯片为max3232eue+,所述phy芯片为88e1518-a0-nnb2c000。

43.所述背板通信电路包括模拟量采集电路、rs422串口、cpci通信电路、第二eeprom,所述模拟量采集电路、rs422串口、cpci通信电路均与所述面板连接器对应端口j8及zynq信号处理电路pl端连接,所述第二eeprom与cpci通信电连接;其中所述第二eeprom容量为2kb。其中所述模拟量采集电路可实现8路模拟信号通过背板连接器端口j8输入,开关分时采集一路模拟量,采集电压范围为0~5v,采集芯片为adg1608bcpz;所述rs422串口同时可实现上位机通过背板连接器端口j8与zynq信号处理电路进行串口通信,rs422串口芯片为max3490esa;所述cpci通信与zynq信号处理电路pl端连接并连接到背板连接器端口j9,cpci背板通信可通过背板连接器端口j9与上位机进行cpci通信,所述cpci通信桥片为pci9054;所述第二eeprom与cpci通信电路连接,为通信桥片提供参数配置的存储空间。

44.所述电源管理电路包括二次电源转换器,所述二次电源转换器两端分别与所述zynq信号处理电路和所述面板连接器对应端口j9连接。所述电源管理部分从背板接口获取+12v直流电源,并通过二次电源转换变换成包括包括捷变频电路、时钟分配电路、adc采集电路、电平变换电路、zynq信号处理电路、存储电路、调测接口、背板通信等的工作电压,通过芯片ltm4620将+12v变换为1v/8.8a,通过芯片ltm4644将+12v变换成1.5v/4a、2.5v/4a、1.8v/4a、3.3v/4a,其中1.5v又通过tps5200芯片变换为0.75v/0.25a,2.5v又通过adp1755芯片变换为1.2v/1.2a,1.8v又通过两片adp1755芯片变换为1.3v/1.2a,变换后的电源可满足整个板卡低纹波稳定的工作。

45.进一步,所述面板连接器包括第一端口j1、第二端口j2、第三端口j3、第四端口j4、第五端口j5、第六端口j6、第七端口j7、第八端口j8、第九端口j9,所述第一端口j1、所述第二端口j2、所述第三端口j3、所述第四端口j4分别设置在所述捷变频电路中并位于板卡前

面板,所述第五端口j5设置在所述时钟分配电路中并位于板卡前面板,所述第六端口j6设置在所述adc采集电路中并位于板卡前面板,所述第七端口j7设置在所述电平变换电路中并位于板卡前面板;所述第八端口j8和所述第九端口j9位于板卡后面板。

46.进一步,所述面板连接器的第一端口j1、第二端口j2、第三端口j3、第四端口j4、第五端口j5、第六端口j6、第七端口j7均为smp-jwhd半擒纵型射频连接器。

47.进一步,所述面板连接器的第九端j9口为j15022101型连接器。

48.最后应说明的是:以上实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1