用于降低串行连接的电子装置之间的延迟的计算系统的制作方法

用于降低串行连接的电子装置之间的延迟的计算系统

[0001]

本申请要求于2019年8月14日在韩国知识产权局提交的第10-2019-0099851号韩国专利申请的优先权,该韩国专利申请的公开内容通过引用全部包含于此。

技术领域

[0002]

在此描述的发明构思的实施例涉及一种计算系统,更具体地,一种用于降低串行连接的电子装置之间的延迟的计算系统。

背景技术:

[0003]

在计算系统中,多个电子装置彼此连接以进行通信。多个电子装置可以串行地或顺序地连接。串行连接的电子装置可以与计算系统的主机通信。

[0004]

与多个电子装置之中的端点装置或终端装置对应的电子装置可以通过至少一个或更多个串行连接的电子装置与主机通信。端点装置与主机之间的通信速度会由于在端点装置与主机之间插入的至少一个或更多个中间电子装置的延迟而变慢。特别地,在端点装置是高速电子装置的配置中,经由中间电子装置的高速电子装置与主机之间的通信速度会显著降低。

技术实现要素:

[0005]

发明构思的实施例提供了一种用于降低串行连接的电子装置之间的延迟的计算系统。

[0006]

根据实施例,提供了一种计算系统,所述计算系统包括:主机;第一电子装置,结合到主机;以及第二电子装置,结合到第一电子装置,第二电子装置被配置为通过第一电子装置与主机通信。第一电子装置被配置为基于从主机接收到的门铃请求主机发送写入主机的提交队列中的写入命令,存储从主机接收到的写入命令,请求主机发送存储在主机的数据缓冲器中的写入命令的写入数据,以及存储从主机接收到的写入数据。

[0007]

根据实施例,提供了一种计算系统,所述计算系统包括:主机;第一电子装置,结合到主机;以及第二电子装置,结合到第一电子装置,第二电子装置被配置为通过第一电子装置与主机通信。第一电子装置被配置为从主机接收用于第二电子装置的写入命令并将写入命令发送到第二电子装置,从主机接收与其中写入有写入命令的提交队列相关联的门铃,将门铃发送到第二电子装置,请求存储在主机的数据缓冲器中的写入命令的写入数据,以及存储从主机接收到的写入数据。

[0008]

根据实施例,提供了一种计算系统,所述计算系统包括:主机;第一电子装置,结合到主机,第一电子装置包括提交队列控制器存储器缓冲器(cmb)和写入cmb;以及第二电子装置,结合到第一电子装置,第二电子装置被配置为通过第一电子装置与主机通信。第一电子装置被配置为从主机接收写入主机的提交队列中的写入命令并将写入命令存储在提交队列cmb中,从主机接收存储在主机的数据缓冲器中的写入命令的写入数据,将写入数据存储在写入cmb中,接收从主机发送的关于提交队列的门铃,以及将门铃发送到第二电子装

置。

附图说明

[0009]

通过参照附图详细地描述发明构思的实施例,发明构思的以上和其他目的和特征将变得明显。

[0010]

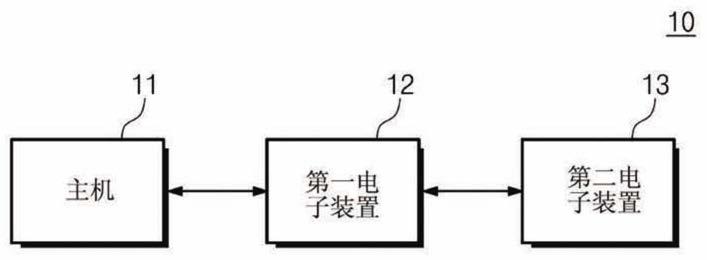

图1示出了根据实施例的计算系统的框图;

[0011]

图2示出了图1的计算系统的详细框图;

[0012]

图3示出了图1的计算系统的框图;

[0013]

图4示出了图3的计算系统的时序图;

[0014]

图5示出了图1的计算系统的框图;

[0015]

图6示出了图5的计算系统的时序图;

[0016]

图7示出了操作图5的计算系统的方法;

[0017]

图8示出了图1的计算系统的框图;

[0018]

图9示出了图8的计算系统的时序图;

[0019]

图10示出了操作图8的计算系统的方法;

[0020]

图11示出了图1的计算系统的框图;

[0021]

图12示出了图11的计算系统的时序图;

[0022]

图13示出了操作图11的计算系统的方法;

[0023]

图14示出了图1的计算系统的框图;

[0024]

图15示出了图14的计算系统的时序图;

[0025]

图16示出了图1的计算系统的框图;

[0026]

图17示出了图16的计算系统的时序图;

[0027]

图18示出了操作图16的计算系统的方法;

[0028]

图19示出了根据实施例的存储装置的框图;以及

[0029]

图20示出了根据实施例的计算装置的框图。

具体实施方式

[0030]

图1示出了根据实施例的计算系统的框图。

[0031]

如图1中所示,计算系统10可以包括主机11、第一电子装置12和第二电子装置13。计算系统10的主机11、第一电子装置12和第二电子装置13可以是各种电子装置(诸如,台式计算机、膝上型计算机、平板计算机、视频游戏控制台、工作站、服务器,计算装置和电动车辆)中的任一种,或者可以是位于电子装置的主板上的各种电子装置中的任一种。

[0032]

主机11可以用片上系统(soc)、专用集成电路(asic)或现场可编程门阵列(fpga)来实现。主机11的控制电路还可以包括通用处理器、中央处理器、专用处理器或应用处理器。主机11可以被实现为处理器本身,或者主机11可以是包括处理器的电子装置或系统。主机11可以控制计算系统10的包括主机11、第一电子装置12和第二电子装置13之间的通信的全部通信。

[0033]

第一电子装置12可以直接地或串行地(或顺序地)连接到主机11。第二电子装置13可以直接地或串行地连接到第一电子装置12。因此,主机11、第一电子装置12和第二电子装

置13可以以顺序方式连接。换言之,第二电子装置13可以通过第一电子装置12连接到主机11。例如,主机11可以与第一电子装置12直接通信,并且可以通过第一电子装置12与第二电子装置13通信。因此,第二电子装置13可以与端点装置对应,第一电子装置12可以是将端点电子装置(即,第二电子装置)13连接到主机11的中间装置。

[0034]

与图1中示出的示例不同,附加电子装置可以在主机11与第一电子装置12之间和第一电子装置12与第二电子装置13之间的任何地方进一步连接在计算系统10中。当然,附加电子装置可以仅连接到第二电子装置13,使得附加电子装置可以是计算系统10的端点装置。

[0035]

第一电子装置12和第二电子装置13可以被实现为相同的电子装置或不同的电子装置。又例如,第一电子装置12可以对应于将第二电子装置13连接到主机11的交换机或交换机装置,第二电子装置13可以对应于与交换机装置不同的端点装置。

[0036]

图2示出了图1的计算系统的详细框图。可与图1的计算系统10对应的计算系统100可以包括处理器110、根复合体120、存储器130以及电子装置141、142、151至154和161至163。这里,电子装置也可以被称为“输入/输出(i/o)装置”,并且电子装置141、142、151至154和161至163可以与图1中示出的第一电子装置12和第二电子装置13对应。处理器110、根复合体120和存储器130可以是图1中示出的主机11的组件。

[0037]

处理器110可以执行各种类型的算术运算或逻辑运算。例如,处理器110可以包括内部高速缓冲存储器和对操作进行控制的至少一个或更多个核(例如,同构多核或异构多核)。处理器110可以执行从存储器130加载的程序代码、软件、应用程序等。

[0038]

根复合体120可以调解处理器110、存储器130以及电子装置141、142、151至154和161至163之间的通信。例如,根复合体120可以管理处理器110、存储器130以及电子装置141、142、151至154和161至163之间的通信时序、通信序列、通信环境等。根复合体120可以以硬件配置、软件配置或者硬件和软件的组合来实现,并且可以被实现在计算系统100的主板上。根复合体120可以是将处理器110和存储器130通信地连接到包括电子装置141、142、151至154和161至163的i/o层次结构的根。根复合体120可以包括一个或更多个下游端口dp。电子装置141和142可以连接到根复合体120的下游端口dp。电子装置151至154可以连接到根复合体120的下游端口dp。此外,电子装置161至163可以连接到根复合体120的下游端口dp。下游端口dp的数量不限于图2中示出的配置。连接到每个下游端口dp的电子装置的数量可以是一个或更多个。

[0039]

在一个实施例中,根复合体120与电子装置141、142、151至154和161至163之间的通信可以按照各种通信接口协议(诸如,外围组件互连快速(pcie)协议、移动pcie(m-pcie)协议、非易失性存储器快速(nvme)协议、通用串行总线(usb)协议、小型计算机系统接口(scsi)协议、高级技术附件(ata)协议、并行ata(pata)、串行ata(sata)、串行连接scsi(sas)协议、电子集成驱动器(ide)协议、通用闪存(ufs)协议和火线协议)来执行。

[0040]

存储器130可以存储用于计算系统100的操作的数据。存储器130可以存储由处理器110处理后的或将由处理器110处理的数据。例如,存储器130可以包括易失性存储器(诸如,静态随机存取存储器(sram)或动态ram(dram))或非易失性存储器(nvm))。可以将可由处理器110执行的应用程序、文件系统或装置驱动程序加载到存储器130上。可以在处理器110的控制下执行加载到存储器130上的程序和软件层,而加载到存储器130中的信息不限

于图2中示出的示例。存储器130可以包括主机存储器缓冲器(hmb)。可以将存储器130的整个存储区域的一部分分配给主机存储器缓冲器hmb。

[0041]

处理器110可以与图1的主机11的处理器对应。处理器110和根复合体120可以与图1的主机11的组件对应。此外,处理器110、根复合体120和存储器130都可以与图1的主机11的组件对应。可以用片上系统(soc)来实现处理器110、根复合体120和存储器130,以构成主机11。可选地,可以用一个或更多个单独的组件来实现处理器110、根复合体120和存储器130,以构成主机11。

[0042]

电子装置142、152、154和163中的每个可以被配置为端点装置。电子装置142、152、154和163中的每个可以包括端点端口ep。剩余的电子装置141、151、153、161和162中的每个可以与中间装置对应。中间装置可以连接到端点装置、另一中间装置或根复合体120。电子装置141、151、153、161和162中的每个可以包括上游端口up和下游端口dp。例如,电子装置141、151、153、161和162的上游端口up可以设置在电子装置141、151、153、161和162的朝向根复合体120的上游侧。电子装置141、151、153、161和162的下游端口dp可以设置在电子装置141、151、153、161和162的朝向端点的下游侧。端点装置的端点端口ep可以连接到中间装置或根复合体120的下游端口dp。端点接口ep也可以被称为“上游端口up”。在图2的配置中,电子装置141、151、153、161和162中的每个可以与图1的第一电子装置12对应,电子装置142、152、154和163中的每个可以与图1的第二电子装置13对应。

[0043]

在一个实施例中,与图1的第一电子装置12对应的电子装置141、151、153、161和162可以是pcie交换机、pcie装置、nvme装置、存储装置或固态驱动器(ssd)。与图1的第二电子装置13对应的电子装置142、152、154和163可以是pcie交换机、pcie装置、nvme交换机、nvme装置、存储装置或ssd。如上所述,连接到电子装置142、152、154和163的任何其他端点装置也可以被包括在计算系统100中。

[0044]

图3示出了图1的计算系统的框图。图4示出了图3的计算系统的时序图。

[0045]

如图3中所示,计算系统200可以包括主机210、交换机220和存储装置230。例如,计算系统200、主机210、交换机220和存储装置230可以分别与图1的计算系统10、主机11、第一电子装置12和第二电子装置13对应。

[0046]

主机210可以包括提交队列(sq)211、完成队列(cq)212和数据缓冲器213。提交队列211、完成队列212和数据缓冲器213可以被实现在图2的主机存储器缓冲器hmb上,并且可以占用主机存储器缓冲器hmb的部分。主机210可以基于提交队列211和完成队列212而通过交换机220对存储装置230执行输入/输出(i/o)操作。

[0047]

交换机220可以设置在主机210与存储装置230之间,并且可以将电信号从主机210(或存储装置230)发送到存储装置230(或主机210)。因此,交换机220充当了主机210与存储装置230之间的中间装置。存储装置230可以接收主机210的命令,可以处理接收到的命令,并且可以经由交换机220将处理结果发送到主机210。存储装置230可以包括非易失性存储器239和控制非易失性存储器239的控制器231。非易失性存储器239可以包括nand闪存、nor闪存、相变ram(pram)、磁性ram(mram)、电阻式ram(rram)、铁电ram(feram)等。

[0048]

主机210可以在提交队列211的条目(或槽)中输入或写入用于存储装置230的命令,并且可以更新提交队列211的尾指针(即,提交队列211的门铃)。例如,门铃可以包括指示提交队列211的地址。提交队列211和完成队列212的对可被提供给处理器110的每个核,

并且所述对的数量可以是一个或更多个。关于图3和图4,主机210可以通过交换机220将提交队列211的门铃提交或发送到存储装置230(

①

)。当门铃从主机210被发送(

①

)之后交换机220的交换机延迟过去时,存储装置230可以从交换机220接收到门铃(

①

)。延迟可以被称为“时间”。例如,交换机220的整个(总)延迟可以被划分为主机侧交换机延迟和存储装置侧交换机延迟。详细地,交换机220可以包括用于发送门铃的一个或更多个发送电路以及包含交换机220中的物理路径的发送路径。例如,门铃经过交换机220的发送路径的一部分所花费的时间可以与主机侧交换机延迟对应,并且门铃经过交换机220的发送路径的剩余部分所花费的时间可以与存储装置侧交换机延迟对应。

[0049]

主机210可以通过发送门铃(

①

)来更新存储装置230的控制器231的门铃寄存器(sqtdbl)232。存储装置230可以读取存储在门铃寄存器232中的门铃,并且可以确认(核实)命令由主机210输入或写入提交队列211中。存储装置230可以基于门铃提取或读取主机210的提交队列211的命令(

②

、

③

)。例如,存储装置230可以请求主机210的提交队列211的命令,并且可以通过交换机220将请求发送到主机210(

②

)。然后,存储装置230可以通过交换机220从主机210读取或接收提交队列211的命令(

③

)。当对命令的请求从存储装置230向交换机220被发送(

②

)之后交换机延迟过去时,请求可以到达主机210(

②

)。此外,当命令从主机210向交换机220被发送(

③

)之后交换机延迟过去时,提交队列211的命令可以到达存储装置230(

③

)。如同在门铃的发送中一样,在发送对命令的请求(

②

)和发送命令(

③

)的情况下会分别发生交换机延迟。

[0050]

存储装置230的控制器231可以包括被配置为将请求或数据直接发送到交换机220或主机210的直接存储器存取(dma)引擎233。dma引擎233可以从交换机220接收命令,并且可以将接收到的命令存储在控制器231的提交队列缓冲器234中。

[0051]

存储装置230可以处理存储在提交队列缓冲器234中的命令。例如,命令可以是写入命令。存储装置230可以对命令进行解码,并且可以基于命令(例如,解码的命令)读取存储在主机210的数据缓冲器213中的写入数据(

④

、

⑤

)。例如,存储装置230可以请求主机210的数据缓冲器213的写入数据,并且可以通过交换机220将请求发送到主机210(

④

)。然后,存储装置230可以通过交换机220从主机210接收数据缓冲器213的写入数据(

⑤

)。当对写入数据的请求从存储装置230向交换机220被发送(

④

)之后交换机延迟过去时,请求可以到达主机210(

④

)。此外,当写入数据从数据缓冲器213向交换机220被发送(

⑤

)之后交换机延迟过去时,写入数据可以到达存储装置230(

⑤

)。如同在门铃的发送中一样,在发送对写入数据的请求(

④

)和发送写入数据(

⑤

)的情况下会分别发生交换机延迟。

[0052]

dma引擎233可以请求写入数据,可以接收写入数据,并且可以将接收到的写入数据存储在控制器231的写入缓冲器235中。尽管已经在命令是写入命令的假设下在请求并发送写入数据的背景中描述了以上操作,但是当命令不是写入命令(例如,是读取命令)时,可以不执行写入数据的发送。

[0053]

存储装置230可以处理主机210的命令,并且可以通过交换机220将关于命令的完成信息发送到主机210(

⑥

)。例如,完成信息可以包括命令是成功地完成还是未成功地完成、处理命令的结果等。当完成信息从存储装置230向交换机220被发送(

⑥

)之后交换机延迟过去时,完成信息可以到达主机210(

⑥

)。可以在主机210的完成队列212中存储或写入完成信息。当完成信息从存储装置230向交换机220被发送(

⑥

)之后交换机延迟过去时,完成

信息可以到达主机210(

⑥

)。如同在门铃的发送中一样,即使在发送完成信息(

⑥

)的情况下也会发生交换机延迟。

[0054]

考虑到由于主机210与存储装置230之间的交换机220而引起的交换机延迟,在此描述的实施例可以提供多个计算系统300至700以及计算装置1000,所述多个计算系统300至700以及所述计算装置1000用于减少处理从主机210生成(或发出)的命令所花费的时间,或者从主机210生成的命令或写入数据到达端点装置(即,存储装置230)所花费的时间。

[0055]

图5示出了图1的计算系统的框图。图6示出了图5的计算系统的时序图。图7示出了操作图5的计算系统的方法。

[0056]

如图5中所示,计算系统300可以包括主机310、交换机320和存储装置330。主机310可以包括提交队列311、完成队列312和数据缓冲器313。主机310的组件311至313可以分别与主机210的组件211至213相似。与图3的交换机220相比较,图5的交换机320可以包括门铃解析器321、命令解析器322、中间提交队列缓冲器323和中间写入缓冲器324。存储装置330可以包括控制器331和非易失性存储器339。控制器331可以包括门铃寄存器332、dma引擎333、提交队列缓冲器334和写入缓冲器335。图5的存储装置330的组件331至335和339可以分别与图3的存储装置230的组件231至235和239相似。上述组件的冗余描述将被省略,并且以下描述将集中在图5的计算系统300与图3的计算系统200之间的差异上。

[0057]

结合地参照图5、图6和图7,在操作s303中,主机310可以在提交队列311中写入或存储用于存储装置330的命令。在操作s306中,主机310可以将提交队列311的门铃发送到交换机320(

①

),并且交换机320可以接收门铃(

①

)。在操作s309中,交换机320可以将门铃发送(转发、中继、重新发送等)到存储装置330(

①

)。在操作s313中,交换机320可以读取或解析门铃。交换机320的门铃解析器321可以读取或解析门铃。在操作s316中,基于门铃,门铃解析器321可以请求主机310的提交队列311的命令,并且可以将请求发送到主机310(

①

)。例如,门铃解析器321可以访问主机310的一个或更多个提交队列之中的由门铃的地址指示(与门铃的地址对应)的提交队列311。在操作s319中,存储装置330的控制器331可以读取或解析门铃寄存器332的门铃。

[0058]

因为交换机320可以在操作s309中向存储装置330发送门铃之后在操作s313中解析门铃,所以交换机320和存储装置330可以同时解析门铃。可选地,当在操作s306中从主机310接收到门铃时,交换机320可以在操作s309中向存储装置330发送门铃之前在操作s313中立即开始解析门铃。就此而言,交换机320可以生成门铃的副本以解析门铃和向存储装置330发送门铃两者,或者另外执行任何操作以在由存储装置330完成对门铃的解析之前完成对门铃的解析。结果,可以降低由于主机310与存储装置330之间存在交换机320而引起的关于它们之间的通信的延迟。

[0059]

在操作s323中,存储装置330可以请求主机310的提交队列311的命令,并且可以将请求发送到交换机320(

②

)。例如,操作s313和操作s316分别与操作s319和操作s323相似。在操作s326中,交换机320可以从主机310接收提交队列311的命令(

③

)。由交换机320对来自主机310的提交队列311的命令的接收可以响应于操作s316中的交换机320的命令请求,从而操作s323中的存储装置330的命令请求的延迟可以被抢先避免。交换机320的中间提交队列缓冲器323可以存储接收到的命令。在操作s329中,交换机320可以响应于操作s323中的请求而将中间提交队列缓冲器323的命令发送到存储装置330(

③

)。在其中在操作s323中

接收到来自存储器装置330的命令请求之前,在操作s326中通过交换机320接收到中间提交队列缓冲器323的命令的情况下,交换机320随后可以对中间提交队列缓冲器323的命令进行缓冲,直到命令请求从存储装置330被接收到为止。控制器331的dma引擎333可以接收命令,并且可以将接收到的命令存储在提交队列缓冲器334中。

[0060]

在解析接收到的门铃并将接收到的门铃发送到存储装置330的时段的至少一部分期间,交换机320的门铃解析器321可以基于门铃请求写入主机310的提交队列311中的命令。在将门铃发送到存储装置330并从存储装置330接收到对命令的请求的时段的至少一部分期间,交换机320可以从主机310接收写入主机310的提交队列311中的命令。

[0061]

操作s309至s326的顺序不限于图7中示出的示例。例如,可以同时执行操作s309和操作s313。例如,操作s326可以优先于操作s323被执行。在任何情况下,当向存储装置330发送接收到的门铃时,交换机320可以例如同时基于门铃请求写入主机310的提交队列311中的命令。如由图6中的阴影所示,由门铃解析器321发送的操作s316的请求到达主机310所必需的延迟的至少一部分可以与由交换机320发送的操作s309的门铃到达存储装置330所必需的延迟或由存储装置330发送的操作s323的请求到达交换机320所必需的延迟重叠。如图6中的阴影所示,从主机310发送的操作s326的命令到达交换机320所必需的延迟的至少一部分可以与由交换机320发送的操作s309的门铃到达存储装置330所必需的延迟或由存储装置330发送的操作s323的请求到达交换机320所必需的延迟重叠。与交换机220相比,交换机320可以通过使用门铃解析器321而使请求与门铃对应的命令所必需的延迟混合。

[0062]

在操作s333中,交换机320可以确定在操作s326中接收到的命令是否是写入命令。当在操作s326中接收到的命令是写入命令(y)时,交换机320可以在操作s336中解析命令,以获得物理区域页(prp)或分散聚集表(sgl)。这里,prp或sgl可以是包括在操作s326中接收到的命令中的地址,所述地址可以指示数据缓冲器313的特定数据存储区域(位置)或存储装置330的特定数据存储区域。在操作s339中,交换机320可以请求主机310的数据缓冲器313的写入数据,并且可以将请求发送到主机310(

③

)。例如,交换机320的命令解析器322可以执行操作s333至s339。在操作s343中,存储装置330可以确定在操作s329中接收到的命令是否是写入命令。当在操作s329中接收到的命令是写入命令(y)时,存储装置330可以在操作s346中解析命令,以获得prp或sgl。在操作s349中,存储装置330可以请求主机310的数据缓冲器313的写入数据,并且可以将请求发送到交换机320(

④

)。dma引擎333可以请求写入数据。在操作s353中,交换机320可以从主机310接收数据缓冲器313的写入数据(

⑤

)。交换机320的中间写入缓冲器324可以存储接收到的写入数据。在操作s356中,交换机320可以响应于在操作s349中接收到的请求而将存储在中间写入缓冲器324中的写入数据发送到存储装置330(

⑤

)。dma引擎333可以接收写入数据,并且可以将接收到的写入数据存储在写入缓冲器335中。例如,操作s333、操作s336、操作s339和操作s353可以分别与操作s343、操作s346、操作s349和操作s356相似。

[0063]

如以上关于门铃所相似地描述的一样,在解析接收到的命令和将接收到的命令发送到存储装置330的时段的至少一部分之前或期间,交换机320的命令解析器322可以基于命令或包含在命令中的地址请求存储在主机310的数据缓冲器313中的写入数据。在将命令发送到存储装置330和从存储装置330接收对写入数据的请求的时段的至少一部分之前或期间,交换机320可以从主机310接收存储在主机310的数据缓冲器313中的写入数据。作为

抢先处理命令的结果,可以减少由于主机310与存储装置330之间存在交换机320而引起的关于它们之间的通信的延迟。

[0064]

操作s329至s356的顺序不限于图7中示出的示例。例如,可以同时执行操作s329和操作s333。例如,操作s353可以优先于操作s349被执行。在任何情况下,当向存储装置330发送接收到的写入命令时,交换机320可以例如同时基于写入命令请求存储在主机310的数据缓冲器313中的写入数据。如由图6中的阴影所示,由命令解析器322发送的操作s339的请求到达主机310所必需的延迟的至少一部分可以与由交换机320发送的操作s329的写入命令到达存储装置330所必需的延迟或由存储装置330发送的操作s349的请求到达交换机320所必需的延迟重叠。如由图6中的阴影所示,从主机310发送的操作s353的写入数据到达交换机320所必需的延迟的至少一部分可以与由交换机320发送的操作s329的写入命令到达存储装置330所必需的延迟或由存储装置330发送的操作s349的请求到达交换机320所必需的延迟重叠。与交换机220相比,交换机320可以通过使用命令解析器322而使请求与写入命令对应的写入数据所必需的延迟混合。

[0065]

在操作s343中,当在操作s329中接收到的命令不是写入命令(n)时或在操作s356之后,存储装置330可以在操作s359中处理命令。例如,当在操作s329中接收到的命令是写入命令时,控制器331可以将写入数据存储在非易失性存储器339中。操作s343、操作s346、操作s349和操作s356可以被包括在操作s359中。例如,当在操作s329中接收到的命令是读取命令时,控制器331可以将存储在非易失性存储器339中的读取数据发送到交换机320。交换机320可以接收读取数据,并且可以将接收到的读取数据发送到主机310。例如,读取数据可以被存储在主机310的数据缓冲器313中。

[0066]

在操作s363中,存储装置330可以将关于命令的完成信息发送到交换机320(

⑥

),并且交换机320可以接收完成信息(

⑥

)。当在操作s326中接收到的命令不是写入命令(n)时或者在操作s356之后,交换机320可以在操作s366中将完成信息发送到主机310(

⑥

)。可以在主机310的完成队列312中存储或写入完成信息。

[0067]

在一个实施例中,可以以硬件配置、以软件配置或以硬件和软件的组合来实现交换机320的组件321至324。在使用硬件的情况下,可以通过使用寄存器、锁存器、触发器、逻辑电路、逻辑门等来不同地实现组件321至324。中间提交队列缓冲器323和中间写入缓冲器324可以与在包括在交换机320中的片上存储器上分配的区域对应。在一个实施例中,可以以硬件配置、以软件配置或以硬件和软件的组合来实现控制器331的组件332至335。

[0068]

在一个实施例中,主机310可以不直接访问交换机320的中间提交队列缓冲器323和中间写入缓冲器324以及存储装置330的控制器331的提交队列缓冲器334和写入缓冲器335。主机310可以通过交换机320直接访问存储装置330的控制器331的门铃寄存器332,而无需交换机320或存储装置330的请求。当主机310更新门铃寄存器332的门铃时,通过执行图7的操作s309至操作s356,交换机320和存储装置330可以获得写入主机310的提交队列311中的命令或存储在数据缓冲器313中的写入数据,并且可以将命令或写入数据存储在以上组件323、324、334和335中。

[0069]

图8示出了图1的计算系统的框图。图9示出了图8的计算系统的时序图。图10示出了操作图8的计算系统的方法。上述组件的冗余描述将被省略,并且以下描述将集中在图8的计算系统400与图5的计算系统300之间的差异上。

[0070]

如图8中所示,计算系统400可以包括主机410、交换机420和存储装置430。主机410可以包括提交队列411、完成队列412和数据缓冲器413。主机410的组件411至413可以分别与主机310的组件311至313相似。交换机420可以包括命令解析器422和中间写入缓冲器424。交换机420的组件422和424可以分别与交换机320的组件322和324相似。

[0071]

存储装置430可以包括控制器431和非易失性存储器439。控制器431可以包括门铃寄存器432、dma引擎433、提交队列控制器存储器缓冲器(sq cmb)434和写入缓冲器435。存储装置430的组件431、432、433、435和439可以分别与存储装置330的组件331、332、333、335和339相似。然而,提交队列控制器存储器缓冲器434可以与提交队列缓冲器334不同。主机410可以在提交队列控制器存储器缓冲器434中直接写入或存储命令。详细地,主机410可以将命令写入提交队列411中,并且可以将写入提交队列411中的命令直接写入提交队列控制器存储器缓冲器434中而无需交换机420或存储装置430的请求。例如,图5的提交队列311可以放置在提交队列控制器存储器缓冲器434上作为提交队列,并且可以同时放置在主机存储器缓冲器hmb上作为提交队列411。同一命令可以存储在提交队列411和提交队列控制器存储器缓冲器434上的所有提交队列中。提交队列411的大小可以小于提交队列311的大小,并且提交队列控制器存储器缓冲器434上的提交队列的大小可以与提交队列311的大小相同。相反,主机310可以不在提交队列缓冲器334中直接写入或存储提交队列311的命令。代替地,可以仅在控制器331执行了操作s309、操作s319、操作s323和操作s329之后将所述命令存储在提交队列缓冲器334中。由于控制器431包括或支持能够由主机410直接访问的提交队列控制器存储器缓冲器434,因此交换机420可以不包括门铃解析器321和中间提交队列缓冲器323。

[0072]

结合地参照图8、图9和图10,主机410可以将用于存储装置430的命令存储在提交队列411中。在操作s403中,主机410可以将写入提交队列411中的命令发送到交换机420(

①

),并且交换机420可以接收命令(

①

)。在操作s406中,交换机420可以将命令发送到存储装置430(

①

)。在可位于操作s403之后的操作s409中,主机410可以将放置在提交队列控制器存储器缓冲器434上的提交队列的门铃发送到交换机420(

②

),并且交换机420可以接收门铃(

②

)。在操作s413中,交换机420可以将门铃发送到存储装置430(

②

)。存储装置430接收命令和门铃所必需的延迟可以比存储装置230/330接收命令和门铃两者所必需的延迟短。

[0073]

图10中的操作s416至操作s449与图7中的操作s333至操作s366相似。交换机420可以执行操作s416至操作s423,可以请求数据缓冲器413的写入数据,并且可以将请求发送到主机410(

②

)。存储装置430可以执行操作s426至操作s433,可以请求数据缓冲器413的写入数据,并且可以将请求发送到交换机420(

③

)。交换机420可以执行操作s436,并且可以从主机410接收数据缓冲器413的写入数据(

④

)。交换机420可以执行操作s436和操作s439,可以将写入数据存储在中间写入缓冲器424中,并且可以将存储在中间写入缓冲器424中的写入数据发送到存储装置430(

④

)。存储装置430可以执行操作s439至操作s446,并且可以将关于命令的完成信息发送到交换机420(

⑤

)。在操作s449中,交换机420可以将完成信息发送到主机410(

⑤

)。

[0074]

图11示出了图1的计算系统的框图。图12示出了图11的计算系统的时序图。图13示出了操作图11的计算系统的方法。上述组件的冗余描述将被省略,并且以下描述将集中在

图11的计算系统500与图5的计算系统300之间的差异上。

[0075]

如图11中所示,计算系统500可以包括主机510、交换机520和存储装置530。主机510可以包括提交队列511、完成队列512和数据缓冲器513。图11的主机510的组件511至513可以分别与图5的主机310的组件311至313相似。交换机520可以包括门铃解析器521和中间提交队列缓冲器523。图11的交换机520的组件521和523可以分别与图5的交换机320的组件321和323相似。

[0076]

存储装置530可以包括控制器531和非易失性存储器539。控制器531可以包括门铃寄存器532、dma引擎533、提交队列缓冲器534和写入控制器存储器缓冲器(写入cmb)535。图11的存储装置530的组件531、532、533、534和539可以分别与图5的存储装置330的组件331、332、333、334和339相似。然而,写入控制器存储器缓冲器535可以与写入缓冲器335不同。主机510可以将写入数据直接存储在写入控制器存储器缓冲器535中。详细地,主机510可以将写入数据存储在数据缓冲器513中,并且可以通过交换机520将存储在数据缓冲器513中的写入数据直接存储在写入控制器存储器缓冲器535中而无需交换机520或存储装置530的请求。例如,图5的数据缓冲器313可以设置在写入控制器存储器缓冲器535上作为数据缓冲器,并且可以同时设置在主机存储器缓冲器hmb上作为数据缓冲器513。相同的数据可以存储在数据缓冲器513和写入控制器存储器缓冲器535上的所有数据缓冲器中。数据缓冲器513的大小可以小于数据缓冲器313的大小,并且写入控制器存储器缓冲器535上的数据缓冲器的大小可以与数据缓冲器313的大小相同。相反,主机310可以不将数据缓冲器313的写入数据直接存储在写入缓冲器335中。代替地,可以仅在控制器331执行了操作s343、操作s346、操作s349和操作s356之后将数据存储在写入缓冲器335中。由于控制器531包括能够由主机510直接访问的写入控制器存储器缓冲器535,因此交换机520可以不包括命令解析器322和中间写入缓冲器324。

[0077]

结合地参照图11、图12和图13,操作s503、操作s506和操作s509可以分别与操作s303、操作s353和操作s356相似。在操作s503中,主机510可以将用于存储装置530的命令存储在提交队列511中。当在操作s503中接收到的命令是写入命令时,在操作s506中,主机510可以将写入数据发送到交换机520(

①

)。在操作s509中,交换机520可以将写入数据发送到存储装置530(

①

)。存储装置530接收写入数据所必需的延迟可以比存储装置230/330/430接收写入数据所必需的延迟短。当命令不是写入命令时,操作s506和操作s509可以被省略。

[0078]

操作s513至操作s536与操作s306至操作s329相似。主机510可以执行操作s513,并且可以将提交队列511的门铃发送到交换机520(

②

)。交换机520可以执行操作s513至操作s523,可以将门铃发送到存储装置530(

②

),可以请求提交队列511的命令,并且可以将请求发送到主机510(

②

)。存储装置530可以执行操作s516、操作s526和操作s529,可以请求提交队列511的命令,并且可以将请求发送到交换机520(

③

)。交换机520可以执行操作s533和操作s536,可以从主机510接收提交队列511的命令(

④

),并且可以将存储在中间提交队列缓冲器523中的命令发送到存储装置530(

④

)。存储装置530可以执行操作s536,并且可以接收命令(

④

)。存储装置530可以执行操作s539和操作s543,并且可以将关于命令的完成信息发送到交换机520(

⑤

)。在操作s546中,交换机520可以将完成信息发送到主机510(

⑤

)。

[0079]

图14示出了图1的计算系统的框图。图15示出了图14的计算系统的时序图。上述组件的冗余描述将被省略,并且以下描述将集中在图14的计算系统600与图5的计算系统300、

图8的计算系统400和图11的计算系统500之间的差异上。

[0080]

计算系统600可以包括主机610、交换机620和存储装置630。主机610可以包括提交队列611、完成队列612和数据缓冲器613。图14中的主机610的组件611、612和613可以分别与图8的主机410的组件411和412以及图11的主机510的组件513相似。图14的交换机620可以与图3的交换机220相似。

[0081]

存储装置630可以包括控制器631和非易失性存储器639。控制器631可以包括门铃寄存器632、提交队列控制器存储器缓冲器634和写入控制器存储器缓冲器635。图14的存储装置630的组件631、632、634、635和639可以分别与图5的存储装置330的组件331和332、图8的存储装置430的组件434、图11的存储装置530的组件535以及图5的存储装置330的组件339相似。尽管在附图中未示出,但是控制器631还可以包括dma引擎。由于控制器631包括能够由主机610直接访问的提交队列控制器存储器缓冲器634和写入控制器存储器缓冲器635,因此交换机620可以不包括交换机320的组件321至324。

[0082]

结合地参照图14和图15,主机610可以将用于存储装置630的命令存储在提交队列611中。主机610可以将提交队列611的命令发送到交换机620(

①

)。交换机620可以将命令发送到存储装置630(

①

)。当命令是写入命令时,主机610可以将写入数据发送到交换机620(

②

)。交换机620可以将写入数据发送到存储装置630(

②

)。当命令不是写入命令时,写入数据的发送可以被省略。与图14和15中示出的示例不同,写入数据可以优先于命令被发送,或者写入数据和命令可以同时被发送。在将命令和写入数据发送到交换机620之后,主机610可以将提交队列611的门铃发送到交换机620(

③

)。交换机620可以将门铃发送到存储装置630(

③

)。存储装置630接收命令、写入数据和门铃所必需的延迟可以比存储装置230/330/530接收命令、写入数据和门铃中的全部所必需的延迟短。存储装置630可以处理命令。存储装置630可以将关于命令的完成信息发送到交换机620(

④

)。交换机620可以将完成信息发送到主机610(

④

)。

[0083]

图16示出了图1的计算系统的框图。图17示出了图16的计算系统的时序图。图18示出了操作图16的计算系统的方法。上述组件的冗余描述将被省略,并且以下描述将集中在图16中的计算系统700与图5中的计算系统300和图14中的计算系统600之间的差异上。

[0084]

计算系统700可以包括主机710、交换机720和存储装置730。主机710可以包括提交队列711、完成队列712和数据缓冲器713。图16中的主机710的组件711至713可以分别与图14中的主机610的组件611至613相似。存储装置730可以包括控制器731和非易失性存储器739。控制器731可以包括门铃寄存器732、dma引擎733、提交队列缓冲器734和写入缓冲器735。图16中的存储装置730的组件731、732、733、734、735和739可以分别与图5中的存储装置330的组件331、332、333、334、335和339相似。

[0085]

交换机720可以包括提交队列控制器存储器缓冲器723和写入控制器存储器缓冲器724。提交队列控制器存储器缓冲器723的操作可以与提交队列控制器存储器缓冲器434的操作相似。主机710可以在交换机720的提交队列控制器存储器缓冲器723中直接写入或存储命令。相反,主机710可以不在存储装置730的控制器731的提交队列缓冲器734中直接写入或存储命令。写入控制器存储器缓冲器724的操作可以与写入控制器存储器缓冲器535的操作相似。主机710可以将写入数据直接存储在交换机720的写入控制器存储器缓冲器724中。相反,主机710可以不将写入数据直接存储在存储装置730的控制器731的写入缓冲

器735中。

[0086]

结合地参照图16、图17和图18,在操作s703中,主机710可以将提交队列711的命令发送到交换机720(

①

)。提交队列控制器存储器缓冲器723可以存储在操作s703中接收到的命令。当命令是写入命令时,在操作s706中,主机710可以将数据缓冲器713的写入数据发送到交换机720(

②

)。写入控制器存储器缓冲器724可以存储在操作s706中接收到的写入数据。与图16至图18中示出的示例不同,写入数据可以优先于命令被发送,或者写入数据和命令两者可以同时被发送。在操作s703和操作s706之后,在操作s709中,主机710可以将提交队列711的门铃发送到交换机720(

③

)。操作s713可以与操作s309相似。交换机720可以执行操作s713,并且可以将门铃发送到存储装置730(

③

)。

[0087]

图18中的操作s716、操作s719、操作s723、操作s726、操作s729、操作s733、操作s736、操作s739、操作s743和操作s746分别与图7中的操作s319、操作s323、操作s329、操作s343、操作s346、操作s349、操作s356、操作s359、操作s363和操作s366相似。存储装置730可以执行操作s716和操作s719,可以请求提交队列711的命令,并且可以将请求发送到交换机720(

④

)。交换机720可以执行操作s723,并且可以将提交队列控制器存储器缓冲器723的命令发送到存储装置730(

⑤

)。存储装置730可以执行操作s726、操作s729和操作s733,可以请求数据缓冲器713的写入数据,并且可以将请求发送到交换机720(

⑥

)。交换机720可以执行操作s736,并且可以将写入控制器存储器缓冲器724的写入数据发送到存储装置730(

⑦

)。存储装置730可以执行操作s739和操作s743,并且可以将关于命令的完成信息发送到交换机720(

⑧

)。在操作s746中,交换机720可以将完成信息发送到主机710(

⑧

)。

[0088]

图19示出了根据实施例的存储装置的框图。

[0089]

参照图3至图18描述图19的存储装置830。存储装置830可以是存储装置230至730中的一种。存储装置830可以包括控制器831、存储器缓冲器838和非易失性存储器839。

[0090]

控制器831可以用soc、asic或fpga等来实现。控制器831可以包括处理器831-1、片上存储器831-2、非易失性存储器接口电路831-3、外部接口电路831-4、dma引擎831-5和缓冲器接口电路831-6。处理器831-1可以控制控制器831的组件831-2至831-6。处理器831-1可以包括内部高速缓冲存储器以及至少一个或更多个核(例如,同构多核或异构多核)。处理器831-1可以执行加载到片上存储器831-2或存储器缓冲器838上的程序代码、软件、应用程序等。

[0091]

片上存储器831-2可以包括锁存器、寄存器、sram、dram、晶闸管随机存取存储器(tram)、紧耦合存储器(tcm)等。闪存转换层(ftl)可以被加载到片上存储器831-2上。ftl可以管理从外部提供的逻辑地址与非易失性存储器839的物理地址之间的映射。ftl还可以执行垃圾收集操作、耗损均衡操作等以及地址映射操作。

[0092]

非易失性存储器接口电路831-3可以按照接口协议(诸如,切换(toggle)双倍数据速率(ddr))与非易失性存储器839通信。非易失性存储器接口电路831-3可以通过通道ch1与一个或更多个非易失性存储器839通信,并且可以通过通道chn(n是2或更大的整数)与一个或更多个非易失性存储器839通信。控制器831与非易失性存储器839之间的通道ch1至chn的数量可以是一个或更多个,分配给一个通道的非易失性存储器的数量可以是一个或更多个,并且每个非易失性存储器839可以是参照图3至图18描述的非易失性存储器239至739中的一种。在处理器831-1的控制下,非易失性存储器接口电路831-3可以将从外部(例

如,主机11、根复合体120、电子装置141、151、153、161和162以及交换机220至720:参照图2至图18)发送的写入数据发送到非易失性存储器839,并且写入数据可以存储在非易失性存储器839中。非易失性存储器接口电路831-3可以在处理器831-1的控制下接收从非易失性存储器839发送的读取数据。

[0093]

外部接口电路831-4可以按照通信接口协议与外部(例如,主机11、根复合体120、电子装置141、151、153、161和162以及交换机220至720:参照图2至图18)通信。例如,所述接口协议可以是usb、scsi、pcie、m-pcie、nvme、ata、pata、sata、sas、ide、ufs、火线等。

[0094]

在处理器831-1的控制下,dma引擎831-5可以直接访问装置(例如,主机11、根复合体120、电子装置141、151、153、161和162以及交换机220至720:参照图2至图18)的各种存储器缓冲器(例如,130的hmb、211、213、323、324、424、523、723和724)。例如,dma引擎831-5可以访问以上存储器缓冲器中的一个,可以接收命令,可以接收写入数据,并且可以发送存储装置830的读取数据。dma引擎831-5可以访问存储装置230至830的各种存储器缓冲器234至734和235至735、片上存储器831-2以及存储器缓冲器838,并且可以与它们交换数据。

[0095]

缓冲器接口电路831-6可以按照接口协议(诸如,ddr标准)与存储器缓冲器838通信。缓冲器接口电路831-6可以在处理器831-1的控制下与存储器缓冲器838交换数据。存储器缓冲器838可以包括锁存器、寄存器、sram、dram、tram、tcm等。例如,存储器缓冲器838可以设置在控制器831外部,并且可以放置在存储装置830内部。又例如,存储器缓冲器838可以不被包括在存储装置830中。在存储器缓冲器838被包括在存储装置830中的构造中,处理器831-1可以使用存储器缓冲器838以及片上存储器831-2作为高速缓冲存储器。

[0096]

在一个实施例中,控制器831可以执行与参照图5至图18描述的存储装置330至730相关联的以下操作:s309、s319、s323、s329、s343、s346、s349、s356、s359、s363、s406、s413、s426、s429、s433、s439、s443、s446、s509、s516、s526、s529、s536、s539、s543、s713、s716、s719、s723、s726、s729、s733、s736、s739和s743。在另一实施例中,不作为端点装置而作为中间装置的存储装置830的操作可以与参考图5至图18描述的交换机320至720的操作类似。在这种情况下,控制器831还可以包括交换机320至720的组件321至324、422、424、521、523、723和724。控制器831可以执行与参照图5至图18描述的交换机320至720相关联的以下操作:s306、s309、s313、s316、s323、s326、s329、s333、s336、s339、s349、s353、s356、s363、s366、s403、s406、s409、s413、s416、s419、s423、s433、s436、s439、s446、s449、s506、s509、s513、s516、s519、s523、s529、s533、s536、s543、s546、s703、s706、s709、s713、s719、s723、s733、s736、s743和s746。

[0097]

图20示出了根据实施例的计算装置的框图。在参照图1至图19描述的计算系统10和100至700中,发明构思的各种实施例可以应用于计算装置1000。计算装置1000可以包括主处理器1100、存储器1200、用户接口1300、存储装置1400、通信块1500和图形处理器1600。例如,计算装置1000可以被称为“移动装置”。

[0098]

主处理器1100可以控制计算装置1000的全部操作。主处理器1100可以被配置为处理各种算术运算或逻辑运算。主处理器1100可以用包括一个或更多个处理器核的专用逻辑电路、fpga、asic、soc等来实现。主处理器1100可以用中央处理器、微处理器、通用处理器、专用处理器或应用处理器来实现。例如,主机11和210至710中的每个以及处理器110可以与主处理器1100对应。

[0099]

存储器1200可以临时地存储用于计算装置1000的操作的数据。存储器1200可以存储由主处理器1100处理后或将由主处理器1100处理的数据。例如,存储器130可以与存储器1200对应。

[0100]

用户接口1300可以在主处理器1100的控制下执行用户与计算装置1000之间的通信调解。例如,用户接口1300可以处理来自键盘、鼠标、小键盘、按钮、触摸面板、触摸屏、触摸板、触摸球、相机、陀螺仪传感器、振动传感器等的输入。此外,用户接口1300可以处理将被提供到显示装置、扬声器、电机等的输出。

[0101]

存储装置1400可以包括无论电力是否被供应都能够存储数据的存储介质。例如,存储装置1400可以是参照图1至图19描述的电子装置12、13、141、142、151至154和161至163、交换机220至720以及存储装置230至730中的一个。存储装置1400可以是中间装置,并且连接到存储装置1400的另一中间装置和另一端点装置也可以被包括在计算装置1000中。

[0102]

通信块1500可以在主处理器1100的控制下与计算装置1000的外部装置/系统通信。例如,通信块1500可以基于各种有线通信协议(诸如,以太网、传输控制协议/互联网协议(tcp/ip)、通用串行总线(usb)和火线)中的至少一种和/或各种无线通信协议(诸如,长期演进(lte)、全球微波接入互操作性(wimax)、全球移动通信系统(gsm)、码分多址(cdma)、蓝牙、近场通信(nfc)、无线保真(wi-fi)和射频识别(rfid))中的至少一种与计算装置1000的外部装置/系统通信。

[0103]

图形处理器1600可以是图形处理单元(gpu),并且可以包括多个处理器核(例如,多个图形处理单元)。包括在图形处理器1600中的处理器核可以快速地并行处理图形数据。例如,图形处理器1600可以通过使用处理器核来处理各种图形运算,诸如,像素着色器、超采样和颜色空间变换。

[0104]

主处理器1100、存储器1200、用户接口1300、存储装置1400、通信块1500和图形处理器1600中的每个可以利用电路级、芯片级和/或封装件级的装置来实现,以安装在计算装置1000中。可选地,主处理器1100、存储器1200、用户接口1300、存储装置1400、通信块1500和图形处理器1600中的每个可以用独立的电子装置来实现,以组装在计算装置1000内。安装后或组装后的组件可以通过总线1700彼此连接。

[0105]

总线1700可以提供计算装置1000的组件之间的导线的通信路径。计算装置1000的组件可以基于总线1700的总线格式来彼此交换数据。例如,总线格式可以包括各种协议(诸如,pcie、nvme、scsi、ata、pata、sata、sas和ufs)中的一种或更多种。

[0106]

根据发明构思的实施例,可以通过使用放置在端点装置与主机之间的电子装置的缓冲器来改善端点装置与主机之间的通信速度。

[0107]

尽管已经参照发明构思的实施例描述了发明构思,但对本领域普通技术人员而言将清楚的是,在不脱离如在权利要求中阐述的发明构思的精神和范围的情况下,可以对其做出各种改变和修改。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1