一种多核芯片的程序更新方法及系统与流程

[0001]

本发明属于嵌入式系统技术领域,涉及一种多核芯片的程序更新方法及系统。

背景技术:

[0002]

电源行业尤其是逆变器行业,为了应对安全规范,通常使用双芯片结构,一个用作主控芯片,性能高价格贵;另一个副芯片性能弱价格低,主要用作冗余检测。当前主控芯片已经沿着应用多核芯片的方向发展,在程序更新维护上少有安全可靠的监测更新装置与方法。在多核芯片的程序更新过程中需要对多个内核进行程序改写,该改写过程极易出错,可能出现程序不能正确运行的“死机”现象,而且开发者往往不能准确知道卡死在程序更新的哪一步骤。

技术实现要素:

[0003]

为了解决上述技术问题,本发明的目是提供一种多核芯片的程序更新方法及系统,其有效降低了由多核芯片自身程序更新而死机的现象。

[0004]

为达到上述目的,本发明采用的一种技术方案为:

[0005]

一种多核芯片的程序更新方法,包括对多核芯片进行更新,所述对多核芯片进行更新包括如下步骤:

[0006]

a、所述多核芯片通知监测器芯片进入程序更新阶段;

[0007]

b、所述多核芯片接收到所述监测器芯片返回的第一监测信号后开启看门狗;

[0008]

c、依次对所述多核芯片的多个内核进行程序更新;及

[0009]

d、所述多核芯片接收到所述监测器芯片在判定更新过程完成后返回的第二监测信号后由看门狗进行复位操作。

[0010]

在一优选的实施例中,所述步骤a中,通过所述多核芯片的输出管脚io_out依据t1低电平t2高电平向所述监测器芯片的输入管脚det_in连续发送n个周期通知所述监测器芯片进入程序更新阶段,t1表示低电平的持续时间,t2表示高电平的持续时间,n大于1。

[0011]

在一优选的实施例中,所述步骤b中,所述监测器芯片的输出管脚det_out由低电平变为高电平,所述多核芯片具有与所述输出管脚det_out连接的输入管脚io_in,所述多核芯片检测到所述输入管脚io_in的信号为高电平,则开启看门狗。

[0012]

在一优选的实施例中,所述步骤c中,所述多核芯片进行某一内核的程序更新,更新完成后,所述多核芯片的输出管脚io_out向所述监测器芯片的输入管脚det_in输出该内核的程序更新完成信息标志,进行下一内核的程序更新。

[0013]

进一步地,所述监测器芯片依据自所述多核芯片的输出管脚io_out接收的信号判别当前程序更新所处的阶段。

[0014]

在一优选的实施例中,所述步骤d中,所述多核芯片的输出管脚io_out输出程序更新结束标志,所述监测器芯片检测到程序更新结束标志并监测到所述多核芯片的输出管脚io_out的输出持续超出t3时间为低电平,则判定程序更新完成。

[0015]

在一优选且具体的实施例中,所述对多核芯片进行更新具体实施如下:

[0016]

s1、进入所述多核芯片的第一内核的第一boot程序,驱动所述多核芯片的输出管脚io_out1、io_out2及io_out3依据t1低电平t2高电平连续发送n个周期,通知监测器芯片进入程序更新阶段;

[0017]

s2、所述监测器芯片的输出管脚det_out1由低电平变为高电平,所述多核芯片依据监测到与所述输出管脚det_out1相连的输入管脚io_in1的信号为高电平,则开启内部看门狗;

[0018]

s3、第一内核由第一boot程序进入第二boot程序,进行程序更新;

[0019]

s4、控制输出管脚io_out1、io_out2及io_out3依据设定的起始数据采集条件及结束条件进行数据采集,所述监测器芯片依据接收到的来自输出管脚io_out3的数据进行当前程序更新所处在的阶段判别;

[0020]

s5、将程序更新数据传递到第一内核的程序区;

[0021]

s6、若第一内核的程序更新数据传递完成,则输出管脚io_out3输出第一内核的程序更新完成信息标志;随即进入下一内核的程序数据传递过程;

[0022]

s7、跳转到所述多核芯片的下一内核的第一boot程序,进行程序数据传递;

[0023]

s8、控制输出管脚io_out1、io_out2及io_out3依据设定的起始数据采集条件及结束条件进行数据采集,所述监测器芯片依据接收到的来自输出管脚io_out3的数据进行当前程序更新所处在的阶段判别;

[0024]

s9、若该内核的程序更新数据传递完成,则输出管脚io_out3输出该内核的程序更新完成信息标志;

[0025]

s10、重复步骤s7至s9,直至完成对所有内核的程序更新;

[0026]

s11、在输出管脚io_out3输出结束标志后,将输出管脚io_out1、io_out2及io_out3的输出同时设置为低;

[0027]

s12、所述监测器芯片检测到程序更新结束标志,且监测出输出管脚io_out1、io_out2及io_out3的输出持续超出t3时间为低电平,则判定程序更新过程完成;监测器芯片将其输出管脚det_out1的输出设定为低电平,则多核芯片会由内部看门狗进行复位操作。

[0028]

在一优选的实施例中,若在程序更新过程中检测到某一步骤执行时间异常,或所述多核芯片的输出管脚的数据错乱,或程序更新文件异常,则由所述监测器芯片对所述多核芯片进行复位。

[0029]

在一优选的实施例中,所述程序更新方法还包括如下步骤:

[0030]

所述多核芯片的外部数据接口接收程序更新文件并将所述程序更新文件传递到外扩存储器的对应区域;

[0031]

所述多核芯片获取所述外扩存储器的数据状态信息;

[0032]

若获取到所述数据状态信息标识为所述外扩存储器的程序未烧录,则对多核芯片进行更新。

[0033]

本发明还采用如下技术方案:

[0034]

一种多核芯片的程序更新系统,搭载如上所述的程序更新方法,所述程序更新系统包括:多核芯片、监测器芯片及用于储存程序更新文件的外扩存储器;

[0035]

所述多核芯片包括:

[0036]

控制交互总线;

[0037]

n个内核,各所述内核分别和所述控制交互总线电性连接;

[0038]

对外数据接口,其用于从外部获取程序更新文件,所述对外数据接口和所述控制交互总线电性连接;

[0039]

通讯接口,其用于和所述外扩存储器进行信息交互;

[0040]

数字io模块,其用于和所述监测器芯片进行信息交互,所述数字io模块和所述控制交互总线电性连接,所述数字io模块具有用于向所述监测器芯片发送信息的输出管脚io_out及用于接收来自所述监测器芯片的输入管脚io_in;及

[0041]

看门狗,其与所述控制交互总线电性连接;

[0042]

所述监测器芯片具有与所述输出管脚io_out电性连接的输入管脚det_in及与所述输入管脚io_in电性连接的输出管脚det_out。

[0043]

本发明采用以上方案,相比现有技术具有如下优点:

[0044]

本发明的程序更新方法及系统,由监测器芯片对多核芯片的程序更新过程进行管理,有效降低由多核芯片自身程序更新而“死机”的现象。

附图说明

[0045]

为了更清楚地说明本发明的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0046]

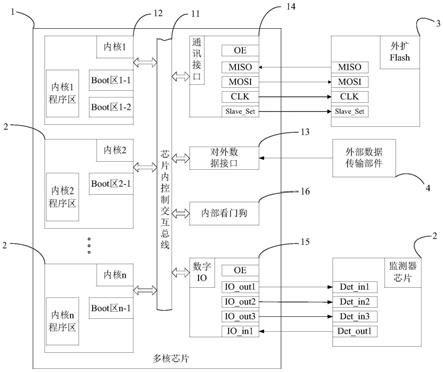

图1为实施例的一种程序更新系统的结构示意图;

[0047]

图2为外扩flash的存储信息排列示意图;

[0048]

图3为程序更新起始阶段多核芯片输出的io电平的示意图;

[0049]

图4为多核芯片的输出管脚的数据传递波形示意图。

[0050]

1、多核芯片;11、控制交互总线;12、内核;13、对外数据接口;14、通讯接口;15、数字io模块;16、看门狗;2、监测器芯片;3、外扩flash;4、外部数据传输部件。

具体实施方式

[0051]

下面结合附图对本发明的较佳实施例进行详细阐述,以使本发明的优点和特征能更易于被本领域的技术人员理解。在此需要说明的是,对于这些实施方式的说明用于帮助理解本发明,但并不构成对本发明的限定。此外,下面所描述的本发明各个实施方式中所涉及到的技术特征只要彼此之间未构成冲突就可以互相结合。

[0052]

本实施例提供一种多核芯片的程序更新系统及该系统搭载的程序更新方法。参照图1所示,该程序更新系统包括多核芯片1、监测器芯片2、外扩存储器及外部数据传输部件4。其中,外扩存储器为非易失性存储器,具体为外扩flash 3,监测器芯片2为单片机或微控制器。

[0053]

多核芯片1为微控制器(mcu芯片)或数字处理器(dsp芯片),其具体包括:控制交互总线11、n个内核12(n≥2)、对外数据接口13、通讯接口14、数字io模块15及看门狗16。其中,控制交互总线11分别和各内核12及对外数据接口13、通讯接口14、数字io模块15及看门狗16电性连接,以实现信息交互。

[0054]

对外数据接口13和外部数据传输部件4相互通信,用于获取外部数据传输部件4接收的程序更新文件。外部数据传输部件4用于对接外部数据的穿入,其为有线传输模块或无线传输模块(wifi模块或gps模块)。具体地,对外数据接口13为ethernet接口、rs422接口或rs485接口。

[0055]

通讯接口14具体为spi接口(serial peripheral interface),其具有miso端口、mosi端口、clk端口及slave_set端口。外扩flash 3也包括spi接口,其也具有miso端口、mosi端口、clk端口及slave_set端口,并与多核芯片1的spi接口的各端口对应电性连接。外扩flash 3预防多核芯片1内部存储程序损坏出现不能正常运行的情形,其为一种非易失性存储介质,断电时数据也不会丢失

[0056]

数字io模块15用于和所述监测器芯片2进行信息交互,数字io模块15具有用于向所述监测器芯片2发送信息的输出管脚io_out及用于接收来自所述监测器芯片2的输入管脚io_in1。具体地,输出管脚io_out为三个,分别为io_out1、io_out2及io_out3。监测器芯片2具有与所述输出管脚io_out电性连接的输入管脚det_in及与所述输入管脚io_in电性连接的输出管脚det_out1。相应地,输入管脚det_in为三个,分别为det_in1、det_in2及det_in3,输出管脚io_out1与输入管脚det_in1电性连接,输出管脚io_out2与输入管脚det_in2电性连接,输出管脚io_out3与输入管脚det_in3电性连接。

[0057]

参照图2所示,对外扩flash 3的分区主要包含flash全局管理信息区、内核1存储区、内核2存储区、内核n等n个内核的存储区(例如,如有3个内核,则每个内核均有对应的程序存储区)。flash全局管理信息区的内容包含flash的分区结构信息、当前flash数据版本信息以及状态信息、预留数据段、该数据区的crc校验码。以内核1为例,内核1存储区包含内核1存储信息标记、内核1程序暂存区1、内核1程序暂存区2。各个分区均包含数据校验码。

[0058]

本实施例中,多核芯片1由对外数据接口13接收外部传递的程序数据文件,并通过spi接口将程序数据文件存储在外部flash。监测器芯片2负责监测以及引导程序更新过程。

[0059]

本实施例的程序更新方法的具体过程如下。

[0060]

1、多核芯片1的对外数据接口13与外部数据传输部件4进行数据交互,接收程序文件并通过spi接口将程序数据依据flash全局管理信息的定义传递到外扩flash 3的对应区域。内核12n程序暂存区2作为新程序数据存储区,在程序文件更新完成后,将暂存区2的数据复制到暂存区1,起备份作用。

[0061]

2、多核芯片1与外扩flash 3信息交互,获取当前flash的分区结构信息、flash数据版本信息以及状态信息。

[0062]

3、若获取状态信息标识为当前flash区域的程序未烧录,则进行程序更新。

[0063]

4、内核12程序更新过程:

[0064]

1)进入多核芯片1的第一个内核的boot程序1-1,驱动io_out1/2/3依据1s低电平1s高电平连续发送3个周期,通知监测器芯片2进入程序更新阶段,如图3所示。

[0065]

2)监测器芯片2输出管脚det_out1由低电平变为高电平。多核芯片1依据监测到的io_in1信号为高电平,则开启内部看门狗16(即io_in1为高电平则开启喂狗操作)。

[0066]

3)第一个内核中的boot程序1-1进入boot程序1-2,进行程序更新。

[0067]

4)控制io_out1/2/3依据设定的起始数据采集条件以及结束条件进行数据采集,如图4所示。依据接收到io_out3的数据进行当前程序更新所处在的阶段判别。

[0068]

5)将flash中的内核1程序暂存区2的数据传递到内核1程序区。

[0069]

6)若第一个内核程序数据传递完成,则io_out3输出第一个内核的程序更新完成信息标志;随即进入第二个内核的程序数据传递过程。

[0070]

7)程序跳转至多核芯片1的第二个内核的boot程序2-1,进行程序数据传递。

[0071]

8)控制io_out1/2/3依据设定的起始数据采集条件以及结束条件进行数据采集。依据接收到io_out3的数据进行当前程序更新所处在的阶段判别。

[0072]

9)若第二个内核的程序数据传递完成,则io_out3输出第二个内核的程序更新完成信息标志;随即进入下一个内核的程序数据传递过程。

[0073]

10)重复步骤7)至9),进行其它内核的程序更新。

[0074]

11)若全部更新完成,则对外部flash的程序暂存区2的数据复制到暂存区1。在io_out3输出结束标志后,将io_out1/2/3的输出同时设置为低。

[0075]

12)监测器芯片2检测到程序更新结束标志,且监测除io_out1/2/3的输出持续超出3秒为低电平,则判定程序更新过程完成。监测器芯片2将det_out1管脚输出设定为低电平,则多核芯片1会由内部看门狗16进行复位操作,重新启动运行。

[0076]

其中,如图4所示,输出管脚io_out1的输出为对称方波,可依据不同多核芯片1与监测器芯片2的需求,设定匹配的频率;本实施例中设定1ms周期。数据采集起始:输出管脚io_out1输出方波正常,io_out2由低变高(低电平事件超出1s)。数据采集期间:输出管脚io_out2保持高电平;在io_out1为高电平时读取io_out3的电平并记录数据。

[0077]

通讯信息采用的数据结构如表1所示,以0xa5为帧头,标志数据长度为2个字节,帧尾为特别校验码0x5a。

[0078]

表1

[0079][0080]

标志数据及其含义如表2所示。

[0081]

表2

[0082]

[0083][0084]

数据采集结束:io_out2为低电平,则本次数据传输结束。

[0085]

若在程序更新过程中检测到某一步骤执行时间异常,或者io_out1/2/3数据错乱,或者外部flash新程序文件异常,则由监测器芯片2对多核芯片1进行复位。

[0086]

若外部flash新程序文件异常,则由未被覆盖的内核程序暂存区1的程序数据进行程序复位。

[0087]

上述程序更新系统及方法,由监测器芯片2对多核芯片1的程序更新过程进行管理,有效降低由多核芯片1自身程序更新而“死机”的现象,较为实用;利用外扩flash 3的非易失特性支持芯片程序的备份与升级;若程序数据出错,可以恢复一个正确的版本;无需复杂的通信端口与通信协议,由现有双芯片结构的副芯片执行监测功能,作为监测器芯片2,成本降低。

[0088]

上述实施例只为说明本发明的技术构思及特点,是一种优选的实施例,其目的在于熟悉此项技术的人士能够了解本发明的内容并据以实施,并不能以此限定本发明的保护范围。凡根据本发明的精神实质所作的等效变换或修饰,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1