数据访问的方法和处理器系统与流程

数据访问的方法和处理器系统

1.本技术要求于2020年7月13日提交的申请号为202010671444.3、发明名称为“一种数据访问的方法和处理器系统”的中国专利申请的优先权,其全部内容通过引用结合在本技术中。

技术领域

2.本技术涉及计算领域,特别涉及一种数据访问的方法和处理器系统。

背景技术:

3.服务器系统中,缓存的结构和容量大小是中央处理器(central processing unit,cpu)的重要性能指标,对cpu速度的影响非常大。cpu内缓存的运行频率极高,一般可以和处理器同频运作,效率远远高于系统内存和硬盘。实际运行场景中,cpu往往需要重复读取同样的数据块,而缓存容量的增大,可以大幅度提升cpu读取数据的命中率,以此提高系统性能。但是由于cpu芯片面积和成本的因素,缓存容量一般较小。

4.按照数据读取顺序和与cpu结合的紧密程度,cpu缓存可以分为第一级缓存l1,第二级缓存l2,部分高端cpu还具有第三级缓存l3,每一级缓存中所储存的全部数据都是下一级缓存的一部分,这三种缓存的技术难度和制造成本是相对递减的,其容量也是相对递增的。上述三级缓存容量有限,因此,现有技术中还引入了大容量的第四级缓存l4。

5.当cpu要读取待访问数据时,依次从l1-l3中查找待访问数据。当在l1~l3级缓存均未命中所述待访问数据时,l3缓存的控制器基于l3缓存中存的l4 tags(标签)判断数据是否在l4中,如果不在,则从内存中读取待访问数据。

技术实现要素:

6.本技术提供了一种数据访问的方法和处理器系统,避免在上级缓存中存放下级缓存标签tags,从而避免对所述上级缓存的空间浪费。

7.第一方面,本技术提供了一种数据访问的方法,所述方法应用于处理器系统,所述处理器系统包括:处理器核、上级缓存和下级缓存,其中,所述上级缓存和所述下级缓存位于不同的die,所述方法包括:当所述上级缓存未存储待访问数据时,所述上级缓存向所述下级缓存和所述内存分别发送数据读取请求,从所述下级缓存或者所述内存中的任一方接收在先返回的所述待访问数据。

8.通过上述方式,可以使得在上级缓存中未命中待访问数据时,无需先判断是否可以在所述下级缓存中命中所述待访问数据,而是并发向下级缓存和内存发送数据获取请求,从二者中的任一个获取待访问数据,从而不需要在所述上级缓存中存储用于查询所述下级缓存的标签tag,避免了对上级缓存的空间浪费。

9.在一种可能的实施方式中,上级缓存和下级缓存分别包括硬件控制逻辑和缓存空间,例如缓存控制器(cache controller)。缓存控制器用于与cpu核或者其他缓存的缓存控制器通信,并对本级缓存的缓存空间执行操作,例如,查询、写入和老化等等。

10.在另一种可能的实施方式中,可以由所述上级缓存的缓存控制器执行第一方面的方法。

11.在另一种可能的实施方式中,所述从所述下级缓存或者所述内存中的任一方接收在先返回的所述待访问数据包括:在先接收到从所述下级缓存返回的所述待访问数据时,丢弃在后收到的所述内存返回的数据读取响应;或者,在所述下级缓存中未存储所述待访问数据时,获取从所述内存返回的所述待访问数据。

12.由于下级缓存的数据访问速度远快于内存的数据访问速度,当待访问数据已经缓存在所述下级缓存时,下级缓存返回所述待访问数据给所述上级缓存的速度快于内存返回所述待访问数据的速度。此时,所述上级缓存在接收到来自下级缓存的待访问数据后,想处理器核返回待访问数据,并丢弃在后收到的内存返回的待访问数据。当待访问数据没有缓存在所述下级缓存中时,下级缓存会向上级缓存返回查询响应(snoop response),所述查询响应用于表示所述下级缓存中未缓存有有效的所述待访问数据。所述上级缓存从所述内存接收所述待访问数据。

13.在一种可能的实施方式中,所述上级缓存所在的die与所述下级缓存所在的die合封形成处理器芯片,所述上级缓存与所述下级缓存通过die间总线通信。

14.上级缓存和处理器核可以在同一cpu die上。

15.在另一种可能的实施方式中,所述下级缓存处在所述上级缓存所在的处理器芯片的外部,所述上级缓存与所述下级缓存通过芯片间总线通信。

16.在一种可能的实施方式中,所述上级缓存通过所述处理器芯片上的内存控制器第一端口与所述内存通信,所述下级缓存通过所述处理器芯片上的内存控制器第二端口与所述内存通信。所述内存为双通道随机存取内存(dual-ported random access memory,dpram)

17.在另一种可能的实施方式中,所述处理器系统还包括io die,所述io die可以用于实现所述上级缓存和所述下级缓存与所述内存之间的连接。具体的,所述io die通过其上的内存控制器连接所述上级缓存与所述内存,以及,连接所述下级缓存和所述内存。

18.在一种可能的实施方式中,所述下级缓存通过所述内存控制器与所述内存之间存在ddr总线(phy)与所述内存进行通信。

19.具体的,所述下级缓存通过所述ddr总线将老化的缓存数据更新到所述内存中;或者所述下级缓存通过所述ddr总线从所述内存获取待缓存的数据。

20.所述下级缓存通过所述内存控制器将老化的缓存数据更新到所述内存中。

21.在一种可能的实施方式中,所述上级缓存将老化的第一缓存行cache line发送给所述下级缓存;如果所述第一缓存行在所述下级缓存中命中,则所述下级缓存使用接收到的所述第一缓存行更新本地缓存;如果所述第一缓存行未在所述下级缓存命中,则将所述第一缓存行写入所述下级缓存。

22.所述上级缓存为第三级缓存l3,所述下级缓存为第四级缓存l4;或,

23.所述上级缓存为第二级缓存l2,所述下级缓存为第三级缓存l3。

24.第二方面,本技术实施例还提供了一种处理器系统,包括处理器核、上级缓存和下级缓存,其中,所述上级缓存和所述下级缓存位于不同的die,

25.所述上级缓存用于在所述上级缓存中没有存储待访问数据时,向所述下级缓存和

内存分别发送数据读取请求,用于请求所述待访问数据,从所述下级缓存或者所述内存中的任一方接收在先返回的所述待访问数据。

26.具体的,可以由所述上级缓存的缓存控制器执行前述第二方面的动作。

27.第三方面,本技术实施例还提供了一种处理器系统,包括处理器核、上级缓存和下级缓存,其中,所述上级缓存和所述下级缓存位于不同的die,所述上级缓存中未存储所述下级缓存的标签tag。

28.第四方面,本技术实施例还提供了一种处理器系统,包括处理器核、第一级缓存、第二级缓存、第三级缓存和第四级缓存,其中,所述处理器核、第一级缓存、第二级缓存和第三级缓存位于处理器die,所述第四级缓存与所述第三级缓存位于不同的die,

29.所述第三级缓存用于在所述第一级缓存、第二级缓存和第三级缓存中均未存储有处理器核请求的待访问数据时,向所述第四级缓存发送数据读取请求;

30.所述第四级缓存在所述第四缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

31.所述第四级缓存与所述第三级缓存在同一处理器芯片中的不同die,并通过die间总线与所述第三级缓存通信;或者,

32.所述第四级缓存位于所述第三级缓存所在的处理器芯片外部,通过芯片间总线域所述第三级缓存通信。

33.第五方面,本技术实施例还提供了一种服务器,包括内存和如前述第二至第四方面任一所述的处理器系统。

34.第六方面,本技术实施例还提供了一种处理器芯片,包括处理器核、第一缓存和第二缓存,其中,所述第一缓存和所述第二缓存位于所述处理器芯片中不同的die,

35.所述第一缓存用于向第二缓存发送数据读取请求,用于获取所述处理器核请求的待访问数据;

36.所述第一缓存在所述第二缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

37.第七方面,本技术实施例还提供了一种处理器芯片,包括处理器核和第一缓存,

38.所述第一缓存用于向所述处理器芯片外的第二缓存发送数据读取请求,用于获取所述处理器核请求的待访问数据;

39.所述第一缓存在所述第二缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

40.第八方面,本技术实施例还提供了另一种数据访问的方法,所述方法应用于处理器系统,所述处理器系统包括:处理器核、上级缓存和下级缓存,其中,所述上级缓存中未存储所述下级缓存的标签tag,所述方法包括:

41.当所述上级缓存中未存储待访问数据时,向所述下级缓存和内存分别发送数据读取请求,用于请求所述待访问数据;

42.从所述下级缓存或者所述内存中的任一方接收在先返回的所述待访问数据。

43.第九方面,本技术实施例还提供了另一种处理器系统,包括:第一die和第二die,所述第一die包括上级缓存和内存控制器,所述第二die包括下级缓存,

44.所述下级缓存用于确定待老化的缓存行,将所述缓存行发送到所述第二die;

45.所述第二die用于通过所述内存控制器的端口将所述缓存行发送到内存。

46.第十方面,本技术实施例还提供了另一种数据访问的方法,所述方法应用于处理器系统,所述处理器系统包括:上级缓存和下级缓存,其中,所述上级缓存和所述下级缓存位于不同的die,所述方法包括:

47.所述下级缓存确定待老化的缓存行;

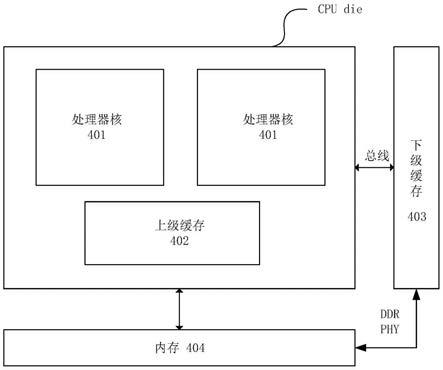

48.所述下级缓存将所述缓存行通过所述上级缓存所在的die上的内存控制器端口发送到内存。

49.第十一方面,本技术实施例提供了一种缓存控制器,所述缓存控制器用于执行前述第一方面、第八方面和第十方面的方法。

附图说明

50.图1是本技术实施例提供的一种缓存结构示例的示意图;

51.图2是本技术实施例提供的一种cache line结构示意图;

52.图3是本技术实施例提供的一种处理器系统结构示意图;

53.图4是本技术实施例提供的另一种处理器系统结构示意图;

54.图5是本技术实施例提供的一种处理器核读取待访问数据的方法流程示意图;

55.图6是本技术实施例提供的另一种处理器系统结构示意图;

56.图7是本技术实施例提供的另一种处理器系统结构示意图;

57.图8是本技术实施例提供的另一种处理器系统的结构图示意图;

58.图9是本技术实施例提供的一种数据访问的方法流程示意图;

59.图10是本技术实施例提供的另一种数据访问的流程示意图;

60.图11是申请实施例提供的一种缓存数据老化(evict)的方法流程示意图。

具体实施方式

61.下面将结合附图对本技术实施方式作进一步地详细描述。

62.处理器通常包含多级缓存。在第一级缓存l1中,指令(instruction)和数据(data)分别使用各自的缓存l1i和l1d,在第二级缓存以及第二级以下的缓存中,通过程序和数据共用一套缓存。本技术将缓存的内容统一称为数据,将处理器核要访问的数据成为待访问数据。

63.如图1所示,为本技术实施例提供的一种缓存结构示例的示意图。示例性的,处理器核0和处理器核1分别独享l1缓存和l2缓存,共享l3缓存。缓存空间被分为多个缓存行(cache line,cl),每个cache line的大小可以为32byte、64byte等等,cache line为缓存和内存进行数据交换的最小单位。

64.如图2所示,为本技术实施例提供的一种cache line结构示意图,每个cache line通常包含3个部分:标志位(valid)、tag和block,其中,标志位表示该cache line是否有效,tag中存储的是该cache line对应的内存块的地址、block中存储的是内存块的地址对应的数据。当处理器核需要读取某个数据时,首先在缓存中查找,根据待访问数据的地址查找cache line并验证该cache line的valid标志,如果根据地址查找到的cache line的valid标志位为有效,则从缓存中读取数据,此过程又称为缓存命中(cache hit)。当缓存命中时,

处理器核从缓存中读取数据,这个过程的时间消耗通常为几个时钟周期,当缓存未命中时,处理器核从内存中读取数据,则需要消耗的时间一般为几十或几百个时钟周期,会影响到处理器系统的整体性能。在具体实施场景中,缓存通过索引和标签tag中的地址,来确定本地缓存是否有处理器核读取的待访问数据。标签中的地址具体可以为待访问数据内存地址的高位地址或者部分内存地址位,索引可以为待访问数据内存地址的低位地址。本技术实施例中,判断缓存是否命中的方法可以采用本领域中的常用方式,本技术实施例对此并不进行限定。

65.如图3所示,为本技术实施例提供的一种处理器系统结构示意图。示例性的,处理器系统包括cpu die 30、第四级缓存32和内存34,所示cpu die 30包括处理器核301、第一级缓存l1i302a和l1d302b、第二级缓存303和第三级缓存304。

66.当所述第三级缓存304中存储有第四级缓存的标签l4 tag时,所述标签用于表示第四级缓存中存储的数据的地址信息,例如,数据在内存中的地址。所述第三级缓存通过上述标签可以判断处理器核要访问的数据是否缓存在所述第四级缓存中。此时,随着第四级缓存的容量越大,l4 tag则会占用越多的第三级缓存的空间

67.具体的,处理器核发送访问请求,访问请求携带待访问数据的内存地址,缓存根据所述内存地址查询本地是否缓存有待访问数据。在上一级缓存中未命中待访问数据时,向下一级缓存发送数据访问请求,所述数据访问请求可以为load请求。具体的,如果第一级和第二级缓存中均没有命中待访问数据时,第三级缓存判断本地是否缓存了待访问数据,如果也没有命中,则第三级缓存根据本地存储的第四级缓存的标签判断第四级缓存中是否存储有所述待访问数据,如果第四级缓存中缓存有所述待访问数据,则向第四级缓存发送load请求,从第四级缓存中读取待访问数据,如果第四级缓存中没有存储所述待访问数据,第三级缓存则从内存获取待访问数据。由于第四级缓存为大容量缓存,而第四级缓存的标签则会占用第三级缓存宝贵的存储空间,从而降低了第三级缓存可以存储的数据量,影响了处理器系统的性能。例如,容量为512mb的第四级缓存可能需要在第三级缓存中占用大约25m空间存储,用于存储第四级缓存的标签l4 tags,使得第三级缓存中的该25m的空间无法作为数据缓存使用。

68.为了解决上述技术问题,本技术实施例提供了一种数据访问的方法,应用于处理器系统,如图4所示,所述处理器系统包括处理器核401、上级缓存402、下级缓存403以及内存404,如图5所示,处理器核401读取待访问数据的方法包括:

69.501:判断所述上级缓存402中是否存储有所述待访问数据;

70.502:在所述上级缓存402中没有存储待访问数据时,向所述下级缓存403和所述内存404分别发送数据读取请求,用于请求所述待访问数据;

71.具体的,所述上级缓存402可以向所述下级缓存403和所述内存404并行发送所述数据读取请求。

72.503:从所述下级缓存403或者所述内存404中的任一方接收在先返回的所述待访问数据。

73.其中,所述下级缓存的标签tag用于表示缓存在所述下级缓存中的数据的信息。

74.通过上述方式,可以使得在上级缓存中未命中待访问数据时,并发向下级缓存和内存发送数据获取请求,从二者中的任一个获取待访问数据,从而无需由所述上级缓存判

断是否可以在所述下级缓存中命中所述待访问数据,因此,上级缓存中不需要存储下级缓存的标签,避免了对上级缓存的空间浪费,提高了所述上级缓存的空间使用效率。

75.所述上级缓存中未存储所述下级缓存的标签tag,所述标签用于表示所述下级缓存中存储的数据的地址信息。

76.需要说明的是,所述上级缓存402具体用于向内存404的内存控制器发送数据读取请求,由所述内存404的内存控制器执行待访问数据的查询和返回操作。

77.与现有技术中将下级缓存的标签放在上级缓存,避免跨die时延相比,本技术实施例,通过避免在上级缓存中存储下级缓存的标签,避免上级缓存空间的浪费,提高上级缓存的空间使用效率。

78.图4所示的示例中,处理器核401和上级缓存402在cpu die。与图4不同的是,在另一种可能的实施方式中,所述上级缓存402还可能与处理器核401在不同的die上。例如,所述上级缓存为第三级缓存,所述下级缓存为第四级缓存,此时,处理器核所在的cpu die包括处理器核、第一级缓存和第二级缓存,第三级缓存在非cpu die的第二die上,第四级缓存在第三die上。当三个die合封时,三个die可以通过die间总线通信。

79.在具体的实施方式中,与前述实施例描述内容类似,在所述上级缓存和所述处理器核之间还可以包括归属于处理核独享的缓存,在处理器核读取待访问数据时,先确定待访问数据未存储在独享的缓存后,查询所述待访问数据是否缓存在了所述上级缓存。所述上级缓存与所述处理器核之间可以有一级或多级缓存,本技术实施例对此并不进行限定。

80.示例性的,处理器核401和上级缓存402可以合封,形成的封装结构为处理器芯片。所述内存404与所述下级缓存403之间存在ddr(double data rate)总线(phy),所述下级缓存403与所述内存404可以通过所述ddr phy进行直接通信。具体的,所述下级缓存将通过所述ddr phy将老化的缓存数据更新到所述内存中;或者,所述下级缓存通过所述ddr phy从所述内存获取待缓存的数据。

81.在可能的实施方式中,各级缓存均可以包括缓存控制器,用来执行针对本级缓存的各种操作。

82.示例性的,所述缓存控制器为硬件控制逻辑。所述上级缓存403包括所述硬件控制逻辑,用于执行缓存内容查询,确定待访问数据是否命中,以及读取请求的分别发送等等控制功能。

83.进一步的,如图6所示,为本技术实施例提供的另一种处理器系统结构示意图。与图4不同的是,所述封装结构还可以包括所述下级缓存403,此时,所述处理器核401所在的die与所述下级缓存403所在的die可以通过die间总线相连。

84.如图7所示,为本技术实施例提供的另一种处理器系统结构示意图。所述处理器系统包括处理器核701、第一级缓存l1d和l1i 702、第二级缓存703、第三级缓存704、第四级缓存705和内存706,所述封装结构71包括处理器核701、第一级缓存l1d和l1i 702、第二级缓存703和第三级缓存704,所述封装结构71包括至少2个内存控制器端口711和712,所述内存706具有双通道,一个通道连接到内存控制器第一端口711,另一个通道连接到内存控制器第二端口,所述内存控制器第一端口711与所述第三级缓存704相连,所述内存控制器第一端口712与所述第四级缓存705相连。

85.与图7不同的是,在一种可能的实施方式中,第四级缓存70还可以位于封装结构

内。

86.所述第三级缓存704通过所述处理器芯片上的内存控制器第一端口与所述内存通信,所述第四级缓存705通过所述处理器芯片上的内存控制器第二端口与所述内存通信。

87.第四级缓存705可以通过内存控制器第一端口执行缓存行老化evict操作以及数据预取prefetch操作。

88.如图8所示,为本技术实施例提供的另一种处理器系统的结构图示意图,与图7不同的是,图8所示的处理器系统还包括io die 809,所述io die 809用于连接所述第三级缓存704与所述内存706,以及用于连接所述第四级缓存705和所述内存706。具体的,所述第四级缓存705和所述内存706与所述io die 809上的内存控制器相连,所述内存控制器具体为ddr控制器。所述第四级缓存705与所述io die之间的连接可以仅用于执行老化evict功能。

89.如图9所示,结合前述实施例提供的处理器系统的结构,本技术实施例提供了一种数据访问的方法流程示意图,所述方法包括:

90.步骤901:处理器核执行内存访问操作,读取待访问的数据时,第二级换成中未查询到所述待访问的数据,此时,l2 miss。

91.步骤902:处理器核向第三级缓存发送读取(load)请求,用于请求所述待访问数据。

92.步骤903:第三级缓存中未查询到所述待访问数据,此时,l3 miss。

93.步骤904:所述第三级缓存向第四级缓存和内存控制器分别发送读取(load)请求,用于在l3 miss的情况下,并发地向第四级缓存和内存请求所述待访问数据。

94.步骤905:第四级缓存中查询到所述待访问数据时,表示l4 hit,此时第四级缓存向第三级缓存返回所述待访问数据,并通过所述第三级缓存向所述处理器核返回所述待访问数据。

95.需要说明的是,本技术实施例中,第四级缓存的cache line的存储方式和查询方式可以与现有技术中的第三级缓存l3相同,本技术实施例对缓存内部的实现原理并不进行限定。

96.步骤906:内存控制器向所述第三级缓存返回从内存中查询到的待访问数据。

97.步骤907:第三级缓存确定在先收到了第四级缓存返回的所述待访问数据,丢弃所述内存控制器从所述内存中读取的所述待访问数据。

98.现有技术中,第三级缓存中存储第四级缓存的tag,在l3 miss的情况下,通过查询在l3中存储的l4 tag判断第四级缓存中是否有待访问的数据。与现有技术不同的是,在本技术实施例提供的上述方式中,第三级缓存无需存储第四级缓存的tag,处理器核在l1-l3缓存中未命中待访问数据时,无需通过tag先判断是否可以在所述第四缓存中命中所述待访问数据,而是并发向第四级缓存和内存发送数据读取请求,从二者中的任一个获取待访问数据,从而不需要将用于查询所述第四级缓存的tag存储在第三级缓存中,避免了对第三级缓存的空间浪费。

99.如图10所示,为本技术实施例提供的另一种数据访问的流程示意图,与图9所示的实施例不同之处在于,第四级缓存中未存储有待访问的数据。所述方法包括:

100.步骤1001-步骤1004:与步骤901-904相同。

101.步骤1005:第四级缓存中未查询到所述待访问数据时,表示l4 miss,第四级缓通

知第三级缓存未查询到所述待访问数据。响应可能是读取失败

102.步骤1006:内存控制器向所述第三级缓存返回从内存中查询到的待访问数据。

103.步骤1007:第三级缓存将从内存中获取的所述待访问数据返回给处理器核。

104.如图11所示,为本技术实施例提供的一种缓存数据老化(evict)的方法流程示意图,所述方法包括:

105.步骤1101:处理器核对l2中的第一缓存行cache line执行evict操作,示例性的,所述第一cache line可以为依据现有技术确定的需要老化的cache line;

106.步骤1102:判断在第三级缓存中是否命中(hit)待老化的所述第一cache line,如果是,则更新第三级缓存中的所述第一cache line,如果第三级缓存中没有存储所述第一cache line(cache line miss),则需要把所述第一cache line写入到第三级缓存中。此时,如果第三级缓存没有空余的存储空间,则为了将所述第一cache line写入到第三级缓存,需要从所述第三级缓存中删除掉另外一条cache line(第二cache line)。具体的,可以根据lru算法等方式从缓存中选择待老化的cache line。

107.步骤1103:第三级缓存对第二cache line执行evict操作,向第四级缓存发送所述第二cache line。

108.步骤1104:判断在第四级缓存中是否命中(hit)待老化的所述第二cache line,如果是,则更新第四级缓存中的所述第二cache line,如果第四级缓存中没有存储所述第二cache line(cache line miss),则需要把所述第二cache line写入到第四级缓存中。此时,如果第四级缓存没有空余的存储空间,则为了将所述第二cache line写入到第四级缓存,需要从所述第四级缓存中老化掉另外一条cache line(第三cache line)。具体的,可以根据lru算法等方式从缓存中选择待老化的cache line。

109.步骤1105:第四级缓存对第三cache line执行evict操作,向内存发送所述第三cache line。

110.步骤1106:内存控制器接收所述第三cache line,将第三cache line的数据更新到内存。

111.在一种具体的实施方式中,第四级缓存与所述内存之间存在ddr phy接口,所述第四级缓存通过所述ddr phy接口将所述第三cache line写入到所述内存;

112.在另一种具体的实施方式中,所述第四级缓存与所述内存之间不存在直接连接,所述第四级缓存将所述第三cache line写入第三级缓存,通过所述第三级缓存将所述第三cache line写入到所述内存中。

113.需要说明的是,本技术实施例中前述处理器系统包括的处理器核、上级缓存和下级缓存可能存在多种连接结构。

114.在一种可能的实施方式中,本技术实施例提供的处理器系统,包括处理器核、上级缓存和下级缓存,其中,所述上级缓存和所述下级缓存位于不同的die,所述上级缓存中未存储所述下级缓存的标签tag。

115.在另一种可能的实施方式中,所述上级缓存包括第一级缓存、第二级缓存和第三级缓存,所述下级缓存为第四级缓存。相应地,本技术实施例还提供了一种处理器系统,包括处理器核、第一级缓存、第二级缓存、第三级缓存和第四级缓存,其中,所述处理器核、第一级缓存、第二级缓存和第三级缓存位于处理器die,所述第四级缓存与所述第三级缓存位

于不同的die,

116.所述第三级缓存用于在所述第一级缓存、第二级缓存和第三级缓存中均未存储有处理器核请求的待访问数据时,向所述第四级缓存发送数据读取请求;

117.所述第三级缓存在所述第四缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

118.所述第四级缓存与所述第三级缓存在同一处理器芯片中的不同die,并通过die间总线与所述第三级缓存通信;或者,

119.所述第四级缓存位于所述第三级缓存所在的处理器芯片外部,通过芯片间总线域所述第三级缓存通信。

120.本技术实施例还提供了一种服务器,包括内存和如前述各实施例中的处理器系统。

121.需要说明的是,处理器系统在封装时,可以将下级缓存与上级缓存合封,或者不将下级缓存与上级缓存合封,而是通过芯片间总线相连。前述各实施例中的上级缓存可以称为第一缓存,下级缓存可以称为第二缓存。

122.本技术实施例还提供了一种处理器芯片,包括处理器核、第一缓存和第二缓存,其中,所述第一缓存和所述第二缓存位于所述处理器芯片中不同的die,

123.所述第一缓存用于向第二缓存发送数据读取请求,用于获取所述处理器核请求的待访问数据;

124.所述第一缓存在所述第二缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

125.本技术实施例还提供了一种处理器芯片,包括处理器核和第一缓存,

126.所述第一缓存用于向所述处理器芯片外的第二缓存发送数据读取请求,用于获取所述处理器核请求的待访问数据;

127.所述第一缓存在所述第二缓存中未存储所述待访问数据时,从内存获取所述待访问数据。

128.处理器核在上级缓存中未命中待访问数据时,上级缓存(例如,第三级缓存)可以向下级缓存(例如第四级缓存)请求待访问数据,无需先判断是否可以在所述下级缓存中命中所述待访问数据,从而不需要将所述下级缓存的tag存储在上级缓存中,避免了对上级缓存的空间浪费。在下级缓存中未存储待访问数据时,再向内存请求待访问数据。

129.需要说明的是,在本技术前述各实施例中的die又称为裸晶或者裸片,是以半导体材料制作而成,且未经封装的一块集成电路,该集成电路的既定功能就是在这一小片半导体上实现。通常情况下,集成电路是经光刻等多项步骤,制作在大片的半导体晶圆上,然后再分割成方型小片,方形小片就称为裸晶die。die上只有用于封装的压焊点(pad),在经过封装后得到的芯片对外提供引脚。

130.在具体实现中,作为一种实施例,处理器系统可以包括多个处理器,这些处理器中的每一个可以是一个单核(single-cpu)处理器,也可以是一个多核(multi-cpu)处理器。这里的处理器可以指一个或多个设备、电路、和/或用于处理数据(例如计算机程序指令)的处理核。

131.本领域普通技术人员可以理解实现上述实施例的全部或部分步骤可以通过硬件

来完成,也可以通过程序来指令相关的硬件完成,所述的程序可以存储于一种计算机可读存储介质中,上述提到的存储介质可以是只读存储器,磁盘或光盘等。

132.以上所述仅为本技术的可选实施例,并不用以限制本技术,凡在本技术的原则之内,所作的任何修改、等同替换、改进等,均应包含在本技术的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1