一种单总线芯片的电源电路的制作方法

1.本发明涉及电子应用技术领域,尤其涉及一种单总线芯片的电源电路。

背景技术:

2.目前国内外各开发商、厂商、经销商等对自有产品专利意识提高,商品防伪认证方面需求迫切,为此衍生出许多用于防伪认证的产品,其中加密芯片在防伪认证中的应用十分广泛。比如医疗器械耗材、墨盒、电子烟等产品中都有用到芯片防伪,且主要是采用单总线芯片。但是单总线芯片并不是每时每刻都在工作,除了认证、读写以及其他一些功能性操作外,单总线芯片大部分时间处于空闲状态,然而即使单总线芯片处于空闲状态,单总线芯片的电源电路依旧在为芯片功能,这样整个单总线芯片时刻都处于功耗较大的状态。

技术实现要素:

3.本发明的目的在于提供一种单总线芯片的电源电路,其能够在单总线芯片处于空闲状态时,关断芯片内部电源,使芯片内部掉电,进入低功耗状态。

4.为达到上述目的,本发明提供的方案是:

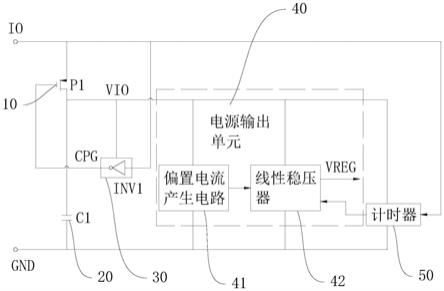

5.一种单总线芯片的电源电路,包括开关元件、电容器件、控制元件、电源输出单元和计时器,所述电容器件、所述控制元件、所述电源输出单元和所述计时器并联设置;所述开关元件一端与单总线芯片的io引脚连接,另一端与所述电容器件连接,所述电容器件的另一端与单总线芯片的gnd引脚连接,所述电容器件用于提供电源给所述控制元件、所述电源输出单元和所述计时器;所述控制元件用于控制所述开关元件的导通和断开,所述控制元件的输入端与单总线芯片的io引脚连接,输出端与所述开关元件连接;所述电源输出单元用于输出电源信号;所述计时器用于输出关断信号或非关断信号给电源输出单元,所述计时器的输入端与单总线芯片的io引脚连接,输出端与所述电源输出单元连接。

6.优选地,所述开关元件为mos器件。

7.优选地,所述开关元件为pmos器件。

8.优选地,所述控制元件为反相器inv1。

9.优选地,所述电源输出单元包括并联设置的偏置电流产生电路和稳压元件,所述偏置电流产生电路并联在所述电容器件的两端,所述偏置电流产生电路用于为所述稳压元件提供工作电流;所述稳压元件用于输出幅值稳定的电源信号;所述计时器与所述稳压元件连接,所述计时器用于输出关断信号或非关断信号给稳压元件。

10.优选地,所述稳压元件为线性稳压器。

11.本发明提供的单总线芯片的电源电路通过计时器与电源输出单元的相互配合实现在单总线芯片处于空闲状态时使芯片内部掉电,当单总线芯片处于空闲状态,计时器开始计时,在计时满一段时间后,电源输出单元停止输出电源信号,从而关断芯片内部电源,使芯片内部掉电,进入低功耗状态,从而能够节约能量。

附图说明

12.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

13.图1是本发明实施例提供的单总线芯片的电源电路的结构示意图。

14.附图标号说明:

15.10、开关元件;20、电容器件;30、控制元件;40、电源输出单元;41、偏置电流产生电路;42、稳压元件;50、计时器。

具体实施方式

16.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明的一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

17.需要说明,本发明实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

18.还需要说明的是,当元件被称为“固定于”或“设置于”另一个元件上时,它可以直接在另一个元件上或者可能同时存在居中元件。当一个元件被称为是“连接”另一个元件,它可以是直接连接另一个元件或者可能同时存在居中元件。

19.另外,在本发明中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本发明要求的保护范围之内。

20.如图1所示,其为本发明的一种实施例的单总线芯片的电源电路。工作时,单总线芯片被当作从机使用。单总线芯片只有两个引脚,所以单总线芯片与主机的互连线非常简单,只有两根互连线:一根互连线共地,另一根互连线用来传输能量和数据,能量供单总线芯片正常工作,数据相互传输则用来完成认证防伪的功能。

21.单总线芯片具有io引脚和gnd引脚,主机能量经过开关元件10存储在电容器件20上,为芯片提供一个电源信号vio。vio再经过电源输出单元40输出幅值稳定的电源信号vreg,vreg为整个芯片供能。

22.请参阅图1,本发明实施例的单总线芯片的电源电路,包括开关元件10、电容器件20、控制元件30、电源输出单元40和计时器50,电容器件20、控制元件30、电源输出单元40和计时器50并联设置;开关元件10一端与单总线芯片的io引脚连接,另一端与电容器件20连接,电容器件20的另一端与单总线芯片的gnd引脚连接,电容器件20用于存储电源,为控制元件30、电源输出单元40和计时器50提供电源;控制元件30用于控制开关元件10的导通和

断开,控制元件30的输入端与单总线芯片的io引脚连接,输出端与开关元件10连接;电源输出单元40用于输出电源信号,为单总线芯片供能;计时器50的输入端与单总线芯片的io引脚连接,输出端与电源输出单元40连接,用于输出关断信号或非关断信号给电源输出单元40。

23.控制元件30接收到的输入信号为io信号,输出信号为cpg信号,io信号为高,cpg信号为低,则开关元件10导通给电容器充电储能;io信号为低,cpg信号为高,则断开开关元件10,防止电容器上电流从开关元件10流走。

24.计时器50在io信号由低跳变为高的时候开始计时,计时满时间t1之后,给出关断信号电平,控制电源输出单元40停止工作,关断vreg信号,使芯片内部掉电;计时器50在io信号由高跳变为低时,则复位计时器50,此时计时器50的输出与关断信号电平相反,不影响电源输出单元40工作;只有在计时满时间t1之后,计时器50才能输出关断信号电平,其他情况下计时器50的输出均与关断信号电平相反,不影响电源输出单元40工作。

25.本发明实施例的单总线芯片的电源电路通过计时器50与电源输出单元40的相互配合实现在单总线芯片处于空闲状态时使芯片内部掉电,当单总线芯片处于空闲状态,计时器50开始计时,在计时满一段时间后,电源输出单元40停止输出电源信号,从而关断芯片内部电源,使芯片内部掉电,进入低功耗状态,从而能够节约能量。

26.优选地,开关元件10为mos器件,具体地,mos器件的漏极与单总线芯片的io引脚连接,mos器件的源极与电容器件20连接,mos器件的栅极与控制元件30的输出端连接。mos器件具有制造结构简单,隔离方便,电路尺寸小、功耗低适于高密度集成的优点。

27.可选地,开关元件10为pmos器件p1。

28.优选地,控制元件30为反相器inv1。

29.优选地,电源输出单元40包括并联设置的偏置电流产生电路41和稳压元件42;偏置电流产生电路41并联在电容器件20的两端,用于为稳压元件42提供工作电流;稳压元件42用于输出幅值稳定的电源信号;计时器50与稳压元件42连接,用于输出关断信号或非关断信号给稳压元件42。

30.进一步地,稳压元件42为线性稳压器,线性稳压器具有低成本,低噪声的优点。

31.可以理解地,在其他实施例中,稳压单元也可以为稳压二极管。

32.以上所述仅为本发明的优选实施例,并非因此限制本发明的专利范围,凡是在本发明的发明构思下,利用本发明说明书及附图内容所作的等效结构变换,或直接/间接运用在其他相关的技术领域均包括在本发明的专利保护范围内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1