一种可综合的CPU模型的制作方法

一种可综合的cpu模型

技术领域

1.本发明涉及一种可综合的cpu模型,用于cpu与总线之间的逻辑功能验证。

背景技术:

2.随着集成电路的不断发展,系统设计的规模越来越大,模块划分的也越来越复杂,作为调度系统工作的核心cpu,显得也越来越重要。一般cpu作为系统的重要组成部分,多采用授权的ip,使用的灵活性和便利性均受到限制。在整个asic设计过程之中,前期需要配置cpu参数,将cpu集成进系统,进行rtl仿真,后期还需要进行fpga综合下板子调试。经过一系列的行为才能通过cpu调度整个系统,观察整个系统的行为是否符合预期。但是若只是验证cpu外的逻辑功能,这将带来巨大的时间成本以及人力成本。

技术实现要素:

3.针对现有技术的缺陷,本发明提供一种可综合的cpu模型,通过模仿cpu的行为,驱动不同类型总线进行系统的读写等操作,来实现cpu系统对外围模块的配置和使用,达到cpu系统原型验证的目的,甚至可以在简单的无需复杂运算的场合,实现对cpu的全替换。

4.为了解决所述技术问题,本发明采用的技术方案是:一种可综合的cpu模型,本cpu模型配置多个总线接口,包括指令获取模块、指令解析模块、数据比较模块、接口仲裁路由模块和总线协议生成模块;所述指令获取模块用于获取模型运行所需的指令,并将指令提供给指令解析模块;指令解析模块实现对编译后的指令解析成cpu能够识别的二进制,达到区分指令功能的目的,然后将解析后的指令传递至数据比较模块;数据比较模块将执行完指令的结果与收到的指令进行比较,从而判断指令是否正确执行;接口仲裁路由模块根据指令内容决定发送的总线端口;总线协议生成模块将接收到的指令或数据按照总线协议格式发送到总线接口,达到将数据转换成标准总线协议接口的功能。

5.进一步的,所述指令获取模块为指令存储模块、指令读取模块、外设接口中的一种或多个组合。

6.进一步的,指令获取模块为多个组合时,cpu模型设置指令获取启动模块,所述指令获取启动模块为外部引脚接拨码开关。

7.进一步的,本cpu模型挂载的总线接口类型包括ahb总线接口、apb总线接口和axi总线接口。

8.进一步的,本cpu挂载ahb总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、burst、size、addr、data共7部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,burst代表该笔传输的

burst类型,size表示该笔传输的数据大小,addr为接受命令的具体地址,data为发送的具体数据。

9.进一步的,本cpu挂载apb总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、addr、strb、data共6部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,addr为接受命令的具体地址,strb为apb 4使用的strb信号,data为发送的具体数据。

10.进一步的,本cpu挂载axi总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、burst、size、length、addr、data共8部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,burst代表该笔传输的burst类型,size表示该笔传输的数据大小,length表示此次传输的数据长度,addr为接受命令的具体地址,data为发送的具体数据。

11.进一步的,本模型支持的协议包括ahb、ahb

‑

lite、amba 2 apb、amba 3 apb、amba 4 apb、axi3、axi4、axi4

‑

lite。

12.本发明为一种可综合的cpu模型,有以下有益效果:1、模型为完全可综合设计,可以实现对系统的原型验证;2、可根据系统需求,配置支持的总线接口个数;3、在无需复杂运算的场合可实现对cpu的替代,突破对cpu ip的依赖;4、该模型较传统cpu而言,结构简单,可以通过较少的模块来实现传统的cpu的功能,从而提高指令执行的效率;5、用该模型替换传统的cpu,可以减少rtl集成复杂度,减少cpu配置参数的复杂度,从而用较少的时间即可验证系统电路逻辑功能的正确性,减少项目整体的开发周期。

附图说明

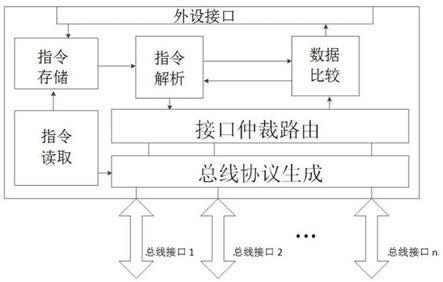

13.图1为实施例1所述可综合cpu模型框图;图2为内嵌指令存储的可综合cpu模型框图;图3为从外部存储读取指令的可综合cpu模型框图;图4为外设接口获取指令的可综合cpu模型框图;图5为挂载ahb总线接口时,指令结构示意图;图6为挂载apb总线接口时,指令结构示意图;图7为挂载axi总线接口时,指令结构示意图。

具体实施方式

14.下面结合附图和具体实施例对本发明做进一步的说明。

15.实施例1本实施例公开一种可综合的cpu模型,如图1所示,本cpu模型挂载n个总线接口,n为大于1的正整数,n可根据系统需求配置。

16.cpu模型包括指令获取模块、指令解析模块、数据比较模块、接口仲裁路由模块和总线协议生成模块。

17.所述指令获取模块用于获取模型运行所需的指令,并将指令提供给指令解析模

块;指令解析模块实现对编译后的指令解析成cpu能够识别的二进制,达到区分指令功能的目的,然后将解析后的指令传递至数据比较模块;数据比较模块将执行完指令的结果与收到的指令进行比较,从而判断指令是否正确执行;接口仲裁路由模块根据指令内容决定发送的总线端口;总线协议生成模块将接收到的指令或数据按照总线协议格式发送到总线接口,达到将数据转换成标准总线协议接口的功能。

18.本实施例中,所述指令获取模块由指令存储模块、指令读取模块、外设接口组合而成,三种模块均可实现指令获取。为了确定指令获取的方式,cpu模型设置指令获取启动模块,所述指令获取启动模块为外部引脚接拨码开关,通过拨码开关确定由三个模块中的一个来获取指令。

19.实施例2本实施例中,如图2所示,所述指令获取模块为指令存储模块,即通过内嵌指令存储的方式获取指令,获取后的指令传递至指令解析模块。

20.实施例3如图3所示,本实施例的指令获取模块为指令读取模块,即通过外部存储读取指令的方式获取指令,获取后的指令传递至指令解析模块。

21.实施例4如图4所示,本实施例的指令获取模块为外设接口,即通过外设接口获取指令,获取后的指令传递至指令解析模块。

22.上述三种实施例中的cpu模型均可以挂载包括ahb总线接口、apb总线接口和axi总线接口在内的amba总线接口。

23.如图5所示,cpu模型挂载ahb总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、burst、size、addr、data共7部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,burst代表该笔传输的burst类型,size表示该笔传输的数据大小,addr为接受命令的具体地址,data为发送的具体数据。

24.如图6所示,cpu模型挂载apb总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、addr、strb、data共6部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,addr为接受命令的具体地址,strb为apb 4使用的strb信号,data为发送的具体数据。

25.如图7所示,cpu模型挂载axi总线接口时,指令获取模块获取的指令包括portid、cmd、w/r、burst、size、length、addr、data共8部分,portid指明发送的指令或数据到达哪个总线接口,cmd表示发送的是数据还是指令,w/r表明该笔传输是读还是写,burst代表该笔传输的burst类型,size表示该笔传输的数据大小,length表示此次传输的数据长度,addr为接受命令的具体地址,data为发送的具体数据。

26.本实施例所述cpu模型支持的协议包括ahb、ahb

‑

lite、amba 2 apb、amba 3 apb、amba 4 apb、axi3、axi4、axi4

‑

lite。这些协议是amba协议的重要组成部分。

27.ahb(advanced high performance bus)系统总线是amba总线规范2.0的重要组成部分,因为分块处理、单周期总线主机移交、单时钟沿操作、流水线操作、更宽的数据总线架构、支持多个总线主从设备的特性,成为ip开发商和soc系统集成者最为青睐的工业标准片上结构,在高性能模块(如 cpu、dma 和 dsp 等)之间的广泛使用。

28.apb(advanced peripheral bus) 外围总线是amba总线规范的重要组成部分,主要用于低带宽的周边外设之间的连接和系统中挂载模块的寄存器配置,是soc系统中普遍采用的控制通路总线协议。apb总线随着amba体系的升级,逐渐形成amba 2 apb、amba 3 apb、amba 4 apb的apb协议序列,对不同apb协议的兼容性已成为对外围设备和寄存器控制通路的主要限制,是cpu设计中用于控制通路的通用接口。

29.axi系统总线是amba(advanced microcontroller bus architecture)3.0协议中最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线。目前,axi协议普遍在大规模、超大规模的soc系统内使用,特别是主流的高性能嵌入式cpu,均使用axi接口作为外部通讯接口使用。

30.验证时,使用人员只需参考图五中的指令格式发送指令,并参考图一指令编译部分使用脚本将特定的指令转换成cpu可识别的二进制即可。该模型便可实现cpu的功能执行指令发送数据,并返回结果进行数据比较。可以避免传统设计验证流程中复杂的cpu集成以及使用难度很大的问题,加快项目开发周期,减少人力以及时间资源上的开销。

31.本发明所述cpu模型支持指令解析,可根据编译后的用户指令进行解析,由接口仲裁部分进行仲裁,然后根据实际总线生成不同的总线协议的数据,可以同时配置多个总线接口以支持不同的总线接口需求。指令来源可以通过指令读取模块产生指令由apb总线接口从外部存储读取,可以通过外设接口读取获得,可以从模型内部例化的存储直接获取。该cpu模型还包含数据比较部分,可将取回的数据与解析后的指令作比较,将比较结果反馈给指令解析部分,以保证数据的正确性。本发明提出的可综合的cpu模型,简化了建立cpu的方法,优化了系统搭建和基础功能验证的效率,支持外设输入编译指令或从内部烧录的指令自启动,发送指令序列进行读写数据,验证外围设备的合理性和正确性,使得芯片设计和验证流程变的更加高效。

32.以上描述的尽是本发明的基本原理和优选实施例,本领域技术人员根据本发明做出的改进和替换,属于本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1