一种数字版图布局设计方法及装置与流程

1.本发明涉及芯片测试技术领域,尤其是涉及一种数字版图布局设计方法及装置。

背景技术:

2.集成电路,又称为ic(intergrated circuit),按其功能、结构不同,可以区分为analog ic模拟集成电路、digital ic数字集成电路和数模混合集成电路三大类。其中,数模混合集成电路设计又可以分为数字包模拟设计和模拟包数字设计两种方式,特别地,模拟包数字设计是指以模拟版图为fullchip(全芯片)的设计,数字版图以模块化(block)的形式集成到全芯片级版图的设计方式。在数模混合集成电路的版图设计中,由于数字版图和模拟版图采用的设计工具的不同,因此需要提供数字版图与模拟版图的信息交互,以完成数字和模拟两者的集成,最终实现数模混合集成电路芯片的设计。现有的版图布局映射方法通常为:模拟版图工程师需要较准确地整理数字block准确的size(大小)、数字block和模拟版图之间信号传递的引脚位置信息(包含引脚所用金属层的所在层数、金属层的width宽度、引脚在数字block边界boundary的具体坐标信息),数字后端工程师根据这些信息手动进行数字block的floorplan(布局)和引脚位置的摆放以实现数字block版图设计,然后再把数字block版图数据交付给模拟版图工程师完成fullchip的芯片设计。但是现有的数字版图布局设计方法容易出现信息的缺漏或者误传,导致数字版图的设计效率较低。

技术实现要素:

3.本发明提供了一种数字版图布局设计方法及装置,以解决现有的数字版图布局设计方法容易出现信息的缺漏或者误传,导致版数字版图的设计效率较低的技术问题。

4.本发明的一个实施例提供了一种数字版图布局设计方法,包括:

5.在全芯片版图中规划初始数字版图;

6.提取所述初始数字版图中的引脚位置信息和版图尺寸信息,所述引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息;

7.将所述版图尺寸信息转换为第一脚本,将所述信号传递的引脚位置信息转换为第二脚本,将所述电源供电的引脚信息转换为第三脚本;

8.通过加载所述第一脚本,确定所述初始数字版图在全芯片版图中的实际区域,通过加载所述第二脚本,调整所述初始数字版图中的引脚位置,通过加载所述第三脚本,确定所述初始数字版图的电源网络布线,得到数字版图布局。

9.进一步的,在得到数字版图布局之后,还包括:

10.对所述数字版图布局的布局状态进行调整,得到优化数字版图布局;

11.在所述优化数字版图布局满足预设的芯片布局设计时,判断所述优化数字版图布局是否时序收敛;若否,通过对所述优化数字版图布局进行签核处理,使得所述优化数字版图布局的时序收敛,得到最终数字版图布局。

12.进一步的,所述提取所述初始数字版图中的引脚位置信息和版图尺寸信息,所述

引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息,具体为:

13.提取所述初始数字版图中的lef文件,通过对所述lef文件进行编辑和提取,得到数模电路模块中信号传递的引脚位置信息和电源供电的引脚位置信息。

14.进一步的,所述将所述版图尺寸信息转换为第一脚本,具体为:

15.获取所述版图尺寸信息中多边形的各个交点坐标,将所述交点坐标转换为第一脚本。

16.进一步的,所述布局状态包括:设计规则是否违例、电源网络是否正确以及引脚摆放位置是否正确。

17.进一步的,所述判断所述优化数字版图布局是否时序收敛,具体为:

18.对所述优化数字版图布局依次进行时钟树综合处理和绕线处理,并分析绕线处理后的优化数字版图布局是否收敛。

19.本发明的另一个实施例提供了一种数字版图布局设计装置,包括:

20.版图规划模块,用于在全芯片版图中规划初始数字版图;

21.信息提取模块,用于提取所述初始数字版图中的引脚位置信息和版图尺寸信息,所述引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息;

22.脚本转换模块,用于将所述版图尺寸信息转换为第一脚本,将所述信号传递的引脚位置信息转换为第二脚本,将所述电源供电的引脚信息转换为第三脚本;

23.脚本加载模块,用于通过加载所述第一脚本,确定所述初始数字版图在全芯片版图中的实际区域,通过加载所述第二脚本,调整所述初始数字版图中的引脚位置,通过加载所述第三脚本,确定所述初始数字版图的电源网络布线,得到数字版图布局。

24.本发明实施例通过提取初始数字版图中的引脚位置信息和版图尺寸信息,并根据该引脚信息和版图尺寸信息分别转换为第一脚本、第二脚本和第三脚本,通过对三个脚本的加载确定数字版图的实际区域、调整数字版图的引脚位置以及实现电源网络布线,从而能够得到精确的数字版图布局,能够有效避免信息的缺漏和误传,从而能够有效减少芯片设计上的迭代次数。

附图说明

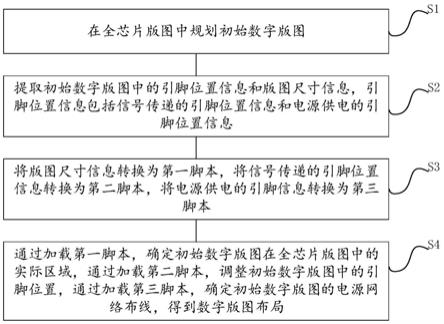

25.图1是本发明实施例提供的一种数字版图布局设计方法的系统示意图;

26.图2是本发明实施例提供的一种数字版图布局设计装置的结构示意图。

具体实施方式

27.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

28.在本技术的描述中,需要理解的是,术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括一个或者更多个该特征。在本技术的描述中,除非另有说明,“多个”的含义是两个或两个以上。

29.在本技术的描述中,需要说明的是,除非另有明确的规定和限定,术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本技术中的具体含义。

30.请参阅图1,在本发明的第一实施例中,提供了一种数字版图布局设计方法,包括:

31.s1、在全芯片版图中规划初始数字版图;

32.在本发明实施例中,根据芯片功能模块在数字版图设计工具virtuoso对全芯片版图规划初始模拟版图和初始数字版图。

33.s2、提取初始数字版图中的引脚位置信息和版图尺寸信息,引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息;

34.在本发明实施例中,基于模拟电路板块版图设计的基础上,确定信号传递的引脚位置信息和电源供电的引脚位置信息。

35.s3、将版图尺寸信息转换为第一脚本,将信号传递的引脚位置信息转换为第二脚本,将电源供电的引脚信息转换为第三脚本;

36.s4、通过加载第一脚本,确定初始数字版图在全芯片版图中的实际区域,通过加载第二脚本,调整初始数字版图中的引脚位置,通过加载第三脚本,确定初始数字版图的电源网络布线,得到数字版图布局。

37.本发明实施例通过提取初始数字版图中的引脚位置信息和版图尺寸信息,并根据该引脚信息和版图尺寸信息分别转换为第一脚本、第二脚本和第三脚本,通过对三个脚本的加载确定数字版图的实际区域、调整数字版图的引脚位置以及实现电源网络布线,从而能够得到精确的数字版图布局,能够有效避免信息的缺漏和误传,从而能够有效减少芯片设计上的迭代次数。

38.在一个实施例中,在得到数字版图布局之后,还包括:

39.对数字版图布局的布局状态进行调整,得到优化数字版图布局;

40.在本发明实施例中,对数字版图布局的设计规则是否违例、电源网络是否正确和引脚摆放位置是否进行检测,若存在问题,则对数字版图进行引脚位置的微调。可以理解的是,上述出现的问题一般是由于模拟版图设计工具和数字版图设计工具在精度上的不同导致的,通过微调能够有效降低这种差异带来的偏差。在检测没有存在问题后,进行数字版图设计的placement阶段。

41.在一种具体的实施方式中,在完成placement阶段后得到的数字版图布局中抽取出gds文件,并以指定命名统一放在指定的工作路径,便于模拟版图工程师调用数字后端实现工程师完成的数字版图布局后,后续数字后端实现工程师更新数字版图布局的gds文件,无需对数字版图布局进行二次调用。

42.在优化数字版图布局满足预设的芯片布局设计时,判断优化数字版图布局是否时序收敛;若否,通过对优化数字版图布局进行签核处理,使得优化数字版图布局的时序收敛,得到最终数字版图布局。

43.本发明实施例通过对数字版图布局中的布局状态进行调整,包括对设计规则是否违例、电源网络是否正确和引脚摆放位置是否进行检测,通过检测结果对引脚位置进行调

整,从而能够优化数字版图布局,以提高数字版图布局的确定效率。

44.在一个实施例中,提取初始数字版图中的引脚位置信息和版图尺寸信息,引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息,具体为:

45.提取初始数字版图中的lef文件,通过对lef文件进行编辑和提取,得到数模电路模块中信号传递的引脚位置信息和电源供电的引脚位置信息。

46.本发明实施例通过提取初始数字版图中的lef文件,并进一步对lef文件进行编辑和提取,以快速得到初始数字版图中的引脚信息,从而能够有效提高引脚信息的统计效率。

47.在一个实施例中,将版图尺寸信息转换为第一脚本,具体为:

48.获取版图尺寸信息中多边形的各个交点坐标,将交点坐标转换为第一脚本。具体地,将交点坐标(x0,y0)(x1,y1)(x2,y2)(x3,y3)

…

(x0,y0)转化为数字版图设计工具进行floorplan布局的第一脚本。

49.在一个实施例中,判断优化数字版图布局是否时序收敛,具体为:

50.对优化数字版图布局依次进行时钟树综合处理和绕线处理,并分析绕线处理后的优化数字版图布局是否收敛。

51.本发明实施例在优化数字版图布局满足芯片版图设计时,则进行cts(时钟树综合)和route(绕线)处理;此时,数字后端实现工程师需要分析最终route后的优化数字版图布局的时序是否收敛以及各项物理验证是否通过;若因数字block floorplan引起时序很难收敛或者有严重设计规则违例,则需要重新优化数字版图布局;若时序收敛和物理验证出现的问题不是因为数字block floorplan引起的,则在placement、cts、route阶段加以一定手段,解决这些问题。

52.实施本发明实施例,具有以下有益效果;

53.本发明实施例通过提取初始数字版图中的引脚位置信息和版图尺寸信息,并根据该引脚信息和版图尺寸信息分别转换为第一脚本、第二脚本和第三脚本,通过对三个脚本的加载确定数字版图的实际区域、调整数字版图的引脚位置以及实现电源网络布线,从而能够得到精确的数字版图布局,能够有效避免信息的缺漏和误传,从而能够有效减少芯片设计上的迭代次数。

54.请参阅图2,本发明的另一个实施例提供了一种数字版图布局设计装置,包括:

55.版图规划模,10,用于在全芯片版图中规划初始数字版图;

56.信息提取模块20,用于提取初始数字版图中的引脚位置信息和版图尺寸信息,引脚位置信息包括信号传递的引脚位置信息和电源供电的引脚位置信息;

57.脚本转换模块30,用于将版图尺寸信息转换为第一脚本,将信号传递的引脚位置信息转换为第二脚本,将电源供电的引脚信息转换为第三脚本;

58.脚本加载模块40,用于通过加载第一脚本,确定初始数字版图在全芯片版图中的实际区域,通过加载第二脚本,调整初始数字版图中的引脚位置,通过加载第三脚本,确定初始数字版图的电源网络布线,得到数字版图布局。

59.本发明实施例通过提取初始数字版图中的引脚位置信息和版图尺寸信息,并根据该引脚信息和版图尺寸信息分别转换为第一脚本、第二脚本和第三脚本,通过对三个脚本的加载确定数字版图的实际区域、调整数字版图的引脚位置以及实现电源网络布线,从而能够得到精确的数字版图布局,能够有效避免信息的缺漏和误传,从而能够有效减少芯片

设计上的迭代次数。

60.在一个实施例中,本装置还包括:

61.布局优化模块,对数字版图布局的布局状态进行调整,得到优化数字版图布局;

62.签核处理模块,用于在优化数字版图布局满足预设的芯片布局设计时,判断优化数字版图布局是否时序收敛;若否,通过对优化数字版图布局进行签核处理,使得优化数字版图布局的时序收敛,得到最终数字版图布局。

63.在一个实施例中,信息提取模块20,包括用于:

64.提取初始数字版图中的lef文件,通过对lef文件进行编辑和提取,得到数模电路模块中信号传递的引脚位置信息和电源供电的引脚位置信息。

65.在一个实施例中,将版图尺寸信息转换为第一脚本,具体为:

66.获取版图尺寸信息中多边形的各个交点坐标,将交点坐标转换为第一脚本。

67.在一个实施例中,布局状态包括:设计规则是否违例、电源网络是否正确以及引脚摆放位置是否正确。

68.在一个实施例中,判断优化数字版图布局是否时序收敛,具体为:

69.对优化数字版图布局依次进行时钟树综合处理和绕线处理,并分析绕线处理后的优化数字版图布局是否收敛。

70.以上是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也视为本发明的保护范围。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1