解速率匹配的方法及装置、终端设备、芯片及存储介质与流程

1.本技术涉及通信技术领域,具体涉及一种解速率匹配的方法及装置、终端设备、芯片及存储介质。

背景技术:

2.第五代(5th generation,5g)系统或新无线(new radio,nr)系统在物理下行共享信道(physical downlink shared channel,pdsch)上进行信息传输时,需要对数据进行速率匹配,以使传输的比特序列与信道资源相匹配。

3.在通信系统的接收端,需要对接收的数据进行解速率匹配。当接收的数据序列中包含大量的重复数据时,需要设置较大的冗余空间来进行重复数据的缓存,这会导致较大的存储开销,进而导致终端设备成本的增加。

技术实现要素:

4.本技术实施例提供一种解速率匹配的方法及装置、终端设备、芯片及存储介质,以解决上述问题。

5.第一方面,提供一种解速率匹配的方法,所述方法应用于译码端的解速率匹配装置,所述装置包括:第一寄存器,包括与交织矩阵中的多行分别对应的多个移位寄存器;存储器,包括多个存储地址,用于存储解速率匹配后的数据;第二寄存器,存储有多个状态指示符,用于指示所述存储器中的每个所述存储地址是否存有数据;所述方法包括:将输入数据写入所述多个移位寄存器;确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址,所述目标移位寄存器为所述多个移位寄存器中的一个;当所述目标存储地址的状态指示符指示所述目标存储地址没有数据时,将所述待存储数据写入所述目标存储地址;当所述目标存储地址的状态指示符指示所述目标存储地址存有数据时,将所述待存储数据与所述目标存储地址中的数据合并后写入所述目标存储地址。

6.可选地,所述待存储数据为满足第一长度的数据,所述第一长度大于或等于所述存储器的一个读写周期内存入所述多个移位寄存器的数据的长度之和。

7.可选地,所述方法还包括:当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的起始数据,确定所述起始数据的偏移量,将所述起始数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址;当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的末尾数据时,将所述末尾数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址。

8.可选地,所述多个移位寄存器的读写优先级按照所述输入数据的写入顺序依次递减。

9.可选地,所述多个移位寄存器的每个移位寄存器的长度按照所述输入数据的写入顺序依次递增,所述多个移位寄存器中相邻的两个移位寄存器的长度的差值大于或等于所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度。

10.可选地,所述多个移位寄存器中所述读写优先级最高的移位寄存器的长度大于或等于所述第一长度与所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度之和。

11.可选地,所述存储器的宽度大于或等于所述第一长度。

12.可选地,所述输入数据包括有效数据和循环数据;所述确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址包括:根据所述输入数据的长度、所述有效数据的长度、所述第一长度和所述交织矩阵的行数确定所述待存储数据在所述存储器中的目标存储地址。

13.第二方面,提供一种解速率匹配装置,包括:第一寄存器,包括多个移位寄存器,分别与交织矩阵中的多行对应;存储器,包括多个存储地址,用于存储解速率匹配后的数据;第二寄存器,存储有多个状态指示符,用于指示所述存储器中的每个所述存储地址是否存有数据;处理器,用于执行以下操作:将输入数据写入所述多个移位寄存器;确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址,所述目标移位寄存器为所述多个移位寄存器中的一个;当所述目标存储地址的状态指示符指示所述目标存储地址没有数据时,将所述待存储数据写入所述目标存储地址;当所述目标存储地址的状态指示符指示所述目标存储地址存有数据时,将所述待存储数据与所述目标存储地址中的数据合并后写入所述目标存储地址。

14.可选地,所述待存储数据为满足第一长度的数据,所述第一长度大于或等于所述存储器的一个读写周期内存入所述多个移位寄存器的数据的长度之和。

15.可选地,所述处理器还用于:当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的起始数据,确定所述起始数据的偏移量,将所述起始数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址;当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的末尾数据时,将所述末尾数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址。

16.可选地,所述多个移位寄存器的读写优先级按照所述输入数据的写入顺序依次递减。

17.可选地,所述多个移位寄存器的每个移位寄存器的长度按照所述输入数据的写入顺序依次递增,所述多个移位寄存器中相邻的两个移位寄存器的长度的差值大于或等于所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度。

18.可选地,所述多个移位寄存器中所述读写优先级最高的移位寄存器的长度大于或等于所述第一长度与所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度之和。

19.可选地,所述存储器的宽度大于或等于所述第一长度。

20.可选地,所述输入数据包括有效数据和循环数据;所述确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址包括:根据所述输入数据的长度、所述有效数据的长度、所述第一长度和所述交织矩阵的行数确定所述待存储数据在所述存储器中的目标存储地址。

21.第三方面,提供一种终端设备,所述终端设备包括处理器、存储有所述处理器可执行指令的存储器,当所述指令被所述处理器执行时,实现如第一方面及第一方面中任一实

现方式所述的方法。

22.第四方面,提供一种芯片,所述芯片包括可编程逻辑电路和/或程序指令,当所述芯片运行时,实现如第一方面及第一方面中任一实现方式所述的方法。

23.第五方面,提供一种计算机可读存储介质,其上存储有程序,所述程序被处理器执行时,实现如第一方面及第一方面中任一实现方式所述的方法。

24.本技术实施例提供的解速率匹配的方法,利用移位寄存器将输入的数据缓存,通过确定移位寄存器中待存储数据在存储器中的目标地址,根据目标地址的状态指示符来确定目标地址的状态;当目标地址为空时,将移位寄存器中的数据写入目标地址,而当目标地址中存储有数据时,将待存储数据与目标地址中的数据进行合并后写入目标地址。

25.上述方法借助移位寄存器和存储器进行反复的读写操作完成解速率匹配操作,使得存储空间没有冗余,从而能够大大减小存储器的面积,进而降低终端设备的成本。

附图说明

26.图1为本技术实施例应用的无线通信系统的示意性结构图。

27.图2为一种无线通信系统中信息传输的流程示意图。

28.图3为相关技术中的循环缓存器的示意图。

29.图4为本技术实施例中当n

cb

=256、e=320时从循环缓存器上存储的数据中进行比特选择的示意图。

30.图5为从图4中选择出的比特序列的示意图。

31.图6为经过比特选择的数据按行写入到交织矩阵中的示意图。

32.图7为将图6中的数据按列读出的示意图。

33.图8为n

cb

=256、e=320时解速率匹配的示意图。

34.图9为本技术一实施例提供的解速率匹配的装置的示意性结构图。

35.图10为本技术一实施例提供的解速率匹配的方法的示意性流程图。

36.图11为本技术实施例提供的解速率匹配架构的示例图。

37.图12为图11中的第一寄存器在解速率匹配时的读写时序图。

38.图13为本技术实施例提供的终端设备的结构示意图。

具体实施方式

39.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本技术一部分实施例,而不是全部的实施例。

40.本技术实施例可以应用于无线通信系统,例如:第五代(5th generation,5g)系统或新无线(new radio,nr)、长期演进(long term evolution,lte)系统、lte频分双工(frequency division duplex,fdd)系统、lte时分双工(time division duplex,tdd)等。或者该无线通信系统还可以是终端对终端(device to device,d2d)通信系统。或者还可以应用于未来的通信系统,如第六代移动通信系统,又如卫星通信系统等。

41.图1为本技术实施例应用的一种示意性的无线通信系统100。该无线通信系统100可以包括网络设备110和终端设备120。网络设备110可以是与终端设备120通信的设备。网络设备110可以为特定的地理区域提供通信覆盖,并且可以与位于该覆盖区域内的终端设

备120进行通信。可选地,该无线通信系统100还可以包括网络控制器、移动管理实体等其他网络实体,本技术实施例对此不作限定。

42.本技术实施例中的终端设备也可以称为用户设备(user equipment,ue)、接入终端、用户单元、用户站、移动站、移动台(mobile station,ms)、移动终端(mobile terminal,mt)、远方站、远程终端、移动设备、用户终端、终端、无线通信设备、用户代理或用户装置。本技术实施例中的终端设备可以是指向用户提供语音和/或数据连通性的设备,可以用于连接人、物和机,例如具有无线连接功能的手持式设备、车载设备等。本技术的实施例中的终端设备可以是手机(mobile phone)、平板电脑(pad)、笔记本电脑、掌上电脑、移动互联网设备(mobile internet device,mid)、可穿戴设备,虚拟现实(virtual reality,vr)设备、增强现实(augmented reality,ar)设备、工业控制(industrial control)中的无线终端、无人驾驶(self driving)中的无线终端、远程手术(remote medical surgery)中的无线终端、智能电网(smart grid)中的无线终端、运输安全(transportation safety)中的无线终端、智慧城市(smart city)中的无线终端、智慧家庭(smart home)中的无线终端等。可选地,ue可以用于充当基站。例如,ue可以充当调度实体,其在v2x或d2d等中的ue之间提供侧行链路信号。比如,蜂窝电话和汽车利用侧行链路信号彼此通信。蜂窝电话和智能家居设备之间通信,而无需通过基站中继通信信号。

43.本技术实施例中的网络设备可以是用于与终端设备通信的设备,该网络设备也可以称为接入网设备或无线接入网设备,如网络设备可以是基站。本技术实施例中的网络设备可以是指将终端设备接入到无线网络的无线接入网(radio access network,ran)节点(或设备)。基站可以广义的覆盖如下中的各种名称,或与如下名称进行替换,比如:节点b(nodeb)、演进型基站(evolved nodeb,enb)、下一代基站(next generation nodeb,gnb)、中继站、接入点、传输点(transmitting and receiving point,trp)、发射点(transmitting point,tp)、主站menb、辅站senb、多制式无线(msr)节点、家庭基站、网络控制器、接入节点、无线节点、接入点(access point,ap)、传输节点、收发节点、基带单元(base band unit,bbu)、射频拉远单元(remote radio unit,rru)、有源天线单元(active antenna unit,aau)、射频头(remote radio head,rrh)、中心单元(central unit,cu)、分布式单元(distributed unit,du)、定位节点等。基站可以是宏基站、微基站、中继节点、施主节点或类似物,或其组合。基站还可以指用于设置于前述设备或装置内的通信模块、调制解调器或芯片。基站还可以是移动交换中心以及设备到设备d2d、车辆外联(vehicle-to-everything,v2x)、机器到机器(machine-to-machine,m2m)通信中承担基站功能的设备、6g网络中的网络侧设备、未来的通信系统中承担基站功能的设备等。基站可以支持相同或不同接入技术的网络。本技术的实施例对网络设备所采用的具体技术和具体设备形态不做限定。

44.网络设备和终端设备可以部署在陆地上,包括室内或室外、手持或车载;也可以部署在水面上;还可以部署在空中的飞机、气球和卫星上。本技术实施例中对网络设备和终端设备所处的场景不做限定。

45.应理解,本技术中的通信设备的全部或部分功能也可以通过在硬件上运行的软件功能来实现,或者通过平台(例如云平台)上实例化的虚拟化功能来实现。

46.图2为一种无线通信系统中信息传输的流程示意图,下面结合图2对本技术中信息

的传输过程以及存在的问题进行详细的解释说明。图2所示系统包括发送端和接收端。

47.在发送端,原始信息序列依次经过信道编码、速率匹配以及调制后发出。

48.信道编码的目的是抗击传输过程中各种各样的噪声和干扰。通常可以通过人为地增加冗余信息,使得系统具有自动纠正差错的能力,从而保证数据传输的高可靠性,保证通信质量。

49.在5g/nr中,物理下行共享信道(physical downlink shared channel,pdsch)一般采用低密度奇偶校验(low density parity check,ldpc)编码。lpdc是一种线性分组纠错码,是在turbo编码之后出现的又一种重要的编码,其校验矩阵具有稀疏特性,因此其编码和译码方法都可以有简化低复杂度的方法;另外,ldpc的译码天然具有并行特点,有利于高吞吐量的译码器设计。利用ldpc编码器,对经crc附着后的待编码比特序列c0,c1,

…

,c

k-1

进行编码,得到编码后的比特序列d0,d1,

…

,d

n-1

。

50.将上述编码后的比特序列d0,d1,

…

,d

n-1

依序存储于如图3所示的长度为n

cb

的循环缓存器中,循环缓存器的长度n

cb

取决于接收端的译码装置的处理能力。如果循环缓存器的长度n

cb

大于或等于编码后的比特序列的长度n,那么可以直接将编码后的比特序列依序保存在循环缓存器;如果循环缓存器的长度n

cb

小于编码后的信息序列的长度n,则可以在删除编码后的比特序列中大于n

cb

的部分后,将剩余部分d0,d1,

…

,d

ncb-1

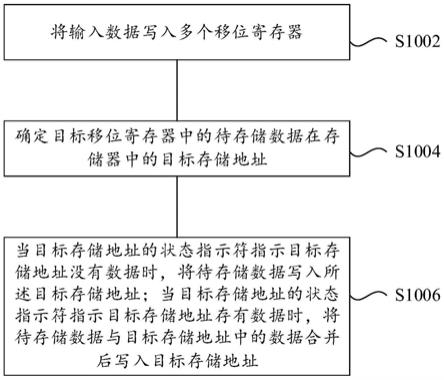

依序存入循环缓存器中。

51.在物理下行共享信道中传输的比特序列的长度需要与信道资源相匹配。因此,在完成了对待传输的比特序列的信道编码之后,还需要进行速率匹配。速率匹配的目的是对信道编码后的比特序列进行由算法控制的重复或打孔,以保证待传输的比特序列的长度与所分配的物理信道资源相匹配。速率匹配的过程包括比特选择和比特交织。

52.比特选择是指从循环缓存器中的选定起始位置k0起,取出预设长度的比特序列段。其中,所述选定起始位置k0可以是接收端的虚拟缓存中某个冗余版本rv

id

的起始位置,在第三代合作伙伴计划(3rd generation partnership project,3gpp)协议(ts 38.212)中对起始位置的确定方法进行了规定,不同冗余版本的起始位置如表1所示,其中zc表示ldpc码基础矩阵扩展因子。

53.表1

[0054][0055]

在取出所述比特序列段的过程中,如果取比特操作达到循环缓存器的末尾时,比特序列段的长度尚未达到预设长度,则需要返回到循环缓存器的头部继续选取,直到所述比特序列段的长度达到所述预设长度,得到输出比特序列e0,e1,

…

,e

e-1

,其中,e表示与信道资源相匹配的输出比特序列的长度。

[0056]

图4和图5分别为当循环缓存器长度n

cb

=256、信道资源长度e=320时从循环缓存器中进行比特选择以及选择出的数据的示意图。如图4所示,长度为n

cb

=256的循环缓存器中包括230个有效比特以及标识为空白的26个填充位。从k0=36的位置开始,跳过上述26个

空白的填充位,依序选择e=320个有效比特,选择出的比特序列如图5所示。由于e》n

cb

,因此图5中所示的数据中包括e0,e1,

…

,e

229

以及重复读出的e0,e1,

…

,e

89

。

[0057]

需要说明的是,在无线通信系统的通信链路中,会存在发生连续突发错误的可能。如果将待传输的比特序列按照原始的顺序发送,那么在传输时如果遇到连续突发错误,将会使大量数据丢失。

[0058]

因此,在相关技术中,可以利用交织编码技术,将待传输的比特序列按照预先设定的规律重新排列。这样使得即使在传输过程中出现连续错误,接收端在对接收到的比特序列进行解交织处理后,也能够将这些错误离散化,而不至于出现连续的误码。再利用相应的译码技术能够较容易的恢复错误的信息位,从而改善传输特性。

[0059]

下面对本技术的场景中使用的交织方法进行简要的介绍。在相关技术中,根据3gpp协议(ts 38.212)的规定,交织前的比特序列e0,e1,

…

,e

e-1

与交织后的比特序列f0,f1,

…

,f

e-1

之间的关系可以根据以下方法确定,其中qm为调制阶数。

[0060][0061]

结合一个示例,对上述交织方法进行举例说明。例如,假设调制方式为16qam时,调制阶数qm=4,有20个输入比特,顺序为0,1,2,3,4

…

18,19,那么在进行比特交织时,在输入比特中每e/qm=5个比特选择一个比特,连续放置这些比特,得到输出序列为:0,5,10,15,1,6,11,16,2,7,12,17,3,8,13,18,4,9,14,19。

[0062]

或者,上述交织方式也可以用矩阵的形式来表现,即将选择出的e个数据写入维度为qm行、e/qm列的矩阵中,写入矩阵后的比特数据如表2所示。将表2所示的矩阵中的数据从第一列开始依序读出得到数据序列e0、、e1、将其记为输出序列f0,f1,

…

,f

e-1

,其中qm为调制阶数。

[0063]

表2

[0064][0065]

下面以图5中所示的经比特选择后的e=320个数据为例,对以上所述比特交织方法进行详细的举例说明。当调制方式为256qam时,qm=8,将图5中的数据写入维度为8行40列的矩阵中,写入该矩阵后的数据如图6所示。

[0066]

将图6所示的交织前按行写入比特序列e0,e1,

…

,e

229

以及重复的部分比特序列e0,e1,

…

,e

89

按照图7中箭头所示的顺序依次读出,将读出的比特序列记为f0,f1,

…

,f

319

,并发送给接收端。

[0067]

对于通信系统中的接收端来说,需要对接收到的比特序列进行解速率匹配,将接收的数据转化为与发送端相同顺序和数量的比特序列。其中解速率匹配可以包括解交织和解绕圈,解交织和解绕圈分别是比特交织和比特选择的逆过程。

[0068]

需要说明的是,为了提高无线通信信号的抗干扰能力,在相关技术中,发送端在完成对待发送比特序列的速率匹配之后,还需要对速率匹配后的比特序列进行数字调制,在5g/nr的下行信道中,一般可以采用正交相移键控(quadrature phase shift keying,qpsk)或正交振幅调制(quadrature amplitude modulation,qam)等方式进行调制。

[0069]

因此,对于接收端而言,首先需要对接收到的信号进行数字解调,确定接收的比特序列中的每个比特对应的一个对数似然比(log-likelihood ratio,llr),称之为软信息,利用该软信息,接收端可以对接收到的信号进行解码。可以理解的是,解调之后的到的软信息序列的顺序与接收端所接收的比特序列的顺序是一致的。因此,解速率匹配的过程也可以理解为是对llr数据序列的操作。

[0070]

如前文中所述,发送端在进行速率匹配时,如果循环缓存器的长度n

cb

大于信道资源的长度e,则需要对循环缓存器中的数据进行打孔操作,剔除部分数据,以使得传输的比特序列的长度能够与信道资源相匹配;而当循环缓存器的长度n

cb

小于信道资源的长度e时,则需要从循环缓存器中重复读取数据,以使得传输的比特序列的长度能够与信道资源相匹配。

[0071]

因此,当e≤n

cb

时,接收端所接收的比特序列中不含重复数据,只需要对其进行解交织处理,将接收的比特序列的顺序还原到与交织前一致,并将解交织后的结果直接写入存储器即可;而当e》n

cb

时,则需要先进行解交织处理,再将解交织处理得到的比特序列中的重复数据合并,使合并后的数据序列为与循环缓存器的长度相同的比特序列,以上操作称之为解绕圈。

[0072]

相关技术中,在进行解速率匹配时,可以将接收的比特序列f0,f1,

…

,f

e-1

按列依次写入到与发送端进行交织处理时的交织矩阵维度相同的矩阵中。如前文所述,当e≤n

cb

时,只需要将按列写入上述矩阵中的数据按行依次读出,按行读出的数据序列即为与交织前相一致的比特序列e0,e1,

…

,e

e-1

,即完成了解速率匹配。

[0073]

而当e》n

cb

时,由于输入的比特序列的长度e超过了接收端的虚拟循环缓存器的长度n

cb

,因而额外的e-n

cb

个比特数据应该与位于缓存器开始的位置进行合并,将e个数据合并为n

cb

个数据。

[0074]

在这种情况下,相关技术中的一种方法是,在接收端将交织矩阵完全还原,再进行重复合并,将完成合并的比特序列e0,e1,

…

,e

e-1

一次性写入存储器中。这种方法控制简单,但是需要较大的存储空间。对于终端设备来说,需要较大面积的ram来进行比特序列的缓存,从而造成较大的设备开销,提高了终端设备的成本。

[0075]

相关技术中另一种方法是:在按列写入的同时先将不需合并的数据直接写入到存储器中;对于e-n

cb

个重复的数据来说,在按列写入的过程中,重复数据可能先被写入缓存器中,而与重复数据相同地址的数据还未被写入,则此时无法立即完成重复合并操作,需要大

量的缓存器将重复数据缓存起来,直到与之地址相同的数据写入缓存器之后才能进行解绕圈合并。当重复数据较多时,接收端仍然需要大量的缓存器将数据缓存起来,再进行解绕圈合并。在一些极端情况下,例如重复循环次数较多时,第一列输入的数据需要存储在缓存器中,直至最后一列数据写入后才能进行合并操作。此时需要消耗较大的缓存空间来存储写入的数据。

[0076]

还以前文中的n

cb

=256、e=320的场景为例,对以上所述问题进行举例说明,图8示出了这种场景下解速率匹配的示意图。将比特序列f0,f1,

…

,f

319

按列写入与交织矩阵维度相同的8行40列的矩阵中;同时,以第一列写入的f0为例,结合图6和图7可知,在进行解速率匹配时,需要将f0与f

245

合并为e0。此时,在第一列数据写入该矩阵时,可以直接将f0写入到存储器中,在若干个读写循环后,f

245

被写入该矩阵,此时可以将f

245

与f0合并为e0后写入存储器。

[0077]

同理,第一列输入的f6和f7则需要分别与f

72

和f

73

合并为e

10

和e

50

;因此当第一列的f0,f2...f7输入时,由于f0,f1...f5在当前读写循环并不需要合并,可以立即写入存储器中;而f6和f7则需要先缓存起来,在9个写入循环之后,f

72

和f

73

才被写入该矩阵中,此时可以分别将f6和f7与f

72

和f

73

合并为e

10

和e

50

后,将e

10

和e

50

写入到存储器中。

[0078]

随着通信技术的发展,尤其是在5g/nr的场景下,信道的传输能力得到了大幅的提升。在极端情况下,信道资源的长度甚至可以达到百万量级,当传输的数据中包含大量的重复数据时,在利用以上所述的方法进行解速率匹配时,通信系统的接收端需要设置大量的冗余空间来缓存接收的比特序列,这会导致非常大的存储开销,进而导致终端设备成本的增加。因此,亟需一种高效的方法和装置来完成解速率匹配,以节约存储空间。

[0079]

为了解决上述问题,本技术实施例提供了一种解速率匹配的方法及装置,下面结合附图对本技术的解速率匹配方法及装置进行详细的描述。

[0080]

本技术实施例提供的解速率匹配的方法应用于通信系统中的译码端的解速率匹配装置。因此,在介绍本技术的方法实施例之前,先对本技术实施例提供的解速率匹配装置进行详细的介绍。

[0081]

图9示出了执行本技术实施例的解速率匹配方法的装置900,所述装置900包括:

[0082]

第一寄存器910,所述第一寄存器910中包括:多个移位寄存器911a、911b...911n,多个移位寄存器911a、911b...911n分别与交织矩阵中的多行相对应;

[0083]

可以理解的是,交织矩阵的行数的多少取决于在通信系统的发送端的编码方式。例如,以图6中所示的情况为例,当调制方式为256qam时,交织矩阵的行数为qm=8。则此时可以将第一寄存器910设置为包括8个移位寄存器911a..911h。

[0084]

存储器920,包括多个存储地址921a...921n,用于存储解速率匹配后的数据。

[0085]

第二寄存器930,存储有多个状态指示符931a...931n,用于指示所述存储器920中的每个所述存储地址是否存有数据。其中,第二寄存器930中存储的状态指示符的数量可以与存储器920中的存储地址的数量相同,以使存储器920中的每一个地址都能够与一个状态指示符相对应。

[0086]

处理器940,用于控制装置900执行解速率匹配操作。

[0087]

下面结合附图详细介绍本技术实施例提供的解速率匹配的方法,如图10所示为本技术一实施例提供的解速率匹配方法的示意性流程图,图10中的方法可以应用于上述解速

率匹配装置900,该方法可以由装置900中的处理器940来执行。图10中的方法包括步骤s1002~s1006。

[0088]

在步骤s1002,将输入数据写入多个移位寄存器。

[0089]

所述移位寄存器可以是前文中所述的第一移位寄存器91中的多个移位寄存器,其中移位寄存器的数量设置为与交织矩阵的行数相同。这样使得交织矩阵的每一行能够与一个移位寄存器唯一对应,从而使每个移位寄存器在不同的写入循环时所写入的数据均为交织矩阵中同一行中的连续数据。

[0090]

在一些实施方式中,输入数据可以是经解调后的llr数据,所述llr数据的数量和排列顺序与发送端进行速率匹配后的比特序列相同。

[0091]

在步骤s1004,确定目标移位寄存器中的待存储数据在存储器中的目标存储地址。其中,目标移位寄存器为第一寄存器中的多个移位寄存器中的一个。

[0092]

本技术实施例中,每个移位寄存器在不同的写入循环时所写入的数据均为交织矩阵中同一行中的连续数据,移位寄存器中的待存储数据在存储器中都具有唯一的目标存储地址。

[0093]

在步骤s1006,当目标存储地址的状态指示符指示目标存储地址没有数据时,将待存储数据写入所述目标存储地址;当目标存储地址的状态指示符指示目标存储地址存有数据时,将待存储数据与目标存储地址中的数据合并后写入目标存储地址。

[0094]

在确定了多个移位寄存器中的目标移位寄存器中所存储的数据的目标地址后,对目标存储地址的状态进行判断,以确定待存储数据是否是需要合并的数据。所述确定目标存储地址的状态可以根据目标存储地址的状态指示符来确定。例如,状态指示符可以为二进制信息,当状态指示符为0时,表示目标存储地址为空;当状态指示符为1时,表示所述目标存储地址存有数据。

[0095]

本技术实施例提供的解速率匹配方法通过移位寄存器将输入的数据缓存,通过确定待存储数据在存储器中的目标地址,根据目标地址的状态指示符来确定目标地址的状态,当目标地址为空时,将移位寄存器中的数据写入目标地址;而当目标地址中存储有数据时,将待存储数据与目标地址中的数据进行合并,将合并后的数据写入目标地址。

[0096]

上述方法借助移位寄存器和存储器进行反复的读写操作完成解速率匹配操作,使得存储空间没有冗余,从而能够大大减小ram的面积。

[0097]

下面结合图11的示例对本技术的解速率匹配的方法进行进一步的说明。图11中的解速率匹配装置包括与交织矩阵行数相同的8个移位寄存器111a...111h以及存储器112。为了方便描述,图11中还示出了交织矩阵,图中的交织矩阵包括8行,其中每行包括e/8个llr数据。

[0098]

图11中最上方示出的是交织矩阵中的一部分,用于示意数据的写入方式。从第0个写入循环开始,分别将llr0...llr7写入到移位寄存器111a...111h中,在若干个(例如图中示出的为32个)写入循环后,移位寄存器111a中存储的数据长度为32llr,确定长度为32llr的待存储数据在存储器112中的目标地址为地址0;根据地址0对应的状态指示符,确定地址0处没有数据,则可以将移位寄存器111a中的32个llr数据写入到存储器的地址0中。

[0099]

对于交织矩阵第6行中虚线部分所示的n

cb

%32个llr数据,在若干个写入循环后,该n

cb

%32个数据被写入到移位寄存器111f中,确定这一部分数据的目标存储地址为地址n;

由地址n对应的状态指示符确定该地址没有存储数据。可以在ncb%32个llr数据后补0,将其长度补齐到32后写入到地址n,其中,a%b表示取a/b的余数。

[0100]

图中所示的交织矩阵的第6行中虚线部分的n

cb

%32之后的32个llr数据为速率匹配时重复读取的数据,这些数据在写入后需要与其目标地址上已经存储的数据进行合并。该32个llr数据在写入到移位寄存器111f后,确定其在存储器中的目标存储地址为地址0;根据前文所述,交织矩阵第一行的前32个llr数据已经写入地址0,因而此时地址0所对应的状态指示符指示该地址已经存有数据,需要已经写入地址0中的数据读出,与该32个llr数据进行合并后将合并的结果写入到地址0中,读取以及写入的过程如图11中113部分所示。

[0101]

在一些实施方式中,目标移位寄存器中的待存储数据可以是满足第一长度的数据。也就是说,可以将输入移位寄存器中的数据先进行缓存,待移位寄存器中的数据满足一定的长度后,再将其读出并写入到存储器中,这样可以减少存储器的读写次数。

[0102]

需要说明的是,在本技术实施例所提供的方法中,将数据写入到移位寄存器和将移位寄存器中的待存储数据写入到存储器中的操作是同步进行的。当确定移位寄存器中的待存储数据需要与目标存储地址中所保存的数据进行合并时,需要先将目标存储地址中的数据读出,再与移位寄存器中的待存储数据进行合并,然后将合并之后的数据写入到目标存储地址,上述读出、合并以及写入的过程称作存储器的一个读写周期。在数据合并读写进行的同时,移位寄存器中还会有新的数据写入,在移位寄存器的长度固定的前提下,为了防止数据溢出,需要确保在一个读写周期内从移位寄存器中读出的数据长度应不小于写入到移位寄存器中的数据的长度。也就是说,移位寄存器中的待存储数据的第一长度应大于或等于存储器的一个读写周期内存入多个移位寄存器的数据的长度之和。

[0103]

例如在图11所示的解速率匹配架构中的第一寄存器包括8个移位寄存器,存储器的一个读写周期内移位寄存器完成了4个写入循环。在存储器一个读写周期内,存入多个移位寄存器中的数据的长度之和为4*8=32llr,因此,移位寄存器中的待存储数据的第一长度应至少为32llr。

[0104]

优选的,移位寄存器中的待存储数据的第一长度等于存储器的一个读写周期内存入多个移位寄存器的数据的长度之和,这样能够最大限度的利用移位寄存器的资源,减少存储空间的冗余。

[0105]

在一些实施方式中,所述存储器的宽度大于或等于所述第一长度。

[0106]

在一些实施方式中,如前文所述,输入数据包括n

cb

个有效数据和e-n

cb

个循环数据,所述确定目标移位寄存器中的待存储数据在存储器中的目标存储地址可以是:根据输入数据的长度,有效数据的长度,第一长度以及交织矩阵的行数来确定目标存储地址。

[0107]

当写入目标移位寄存器的数据为所述交织矩阵中每一行的起始数据,确定所述起始数据的偏移量,将所述起始数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址;

[0108]

当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的末尾数据时,将所述末尾数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址。

[0109]

例如,在图11中,交织矩阵的每一行包括e/qm个llr数据,第一长度为32llr。以交织矩阵中的第一行为例,e/qm个llr数据需要个完整的地址,余下的e/qm%32个llr数据需要与第二行中起始位置的32-e/qm%32个llr数据合并为完整的32llr写入下

一个地址。其中,表示对a向下取整。

[0110]

由于输入数据是按照列的顺序写入移位寄存器中的,因此第二行起始位置的32-e/qm%32个llr数据的写入时间会早于第一行的e/qm%32个llr数据,为了避免占用移位寄存器的资源,可以在第二行的前32-e/qm%32个llr数据前补0,将其长度补齐到32后写入对应的目标存储地址中,如图11中的虚线框114部分所示。当位于第一行末尾的e/qm%32个llr数据被写入到第一行的移位寄存器之后,将先前写入的第二行的前32-e/qm%32个llr数据读出,与第一行末尾的e/qm%32个llr数据合并,将合并结果写入到目标存储地址,读出和写入的过程如图11中114部分所示。交织矩阵中其余行的起始数据和末尾数据的写入方式与第一行和第二行相同,此处不再赘述。

[0111]

交织矩阵中每一行的llr数据在存储器中的写入地址、起始位置llr数量的偏移量以及结束位置剩余llr的数量可以根据表3中的方法计算,其中l为第一长度。

[0112]

表3

[0113][0114]

在一些实施方式中,多个移位寄存器的读写优先级按照输入数据的写入顺序依次递减,所述多个移位寄存器中所述读写优先级最高的移位寄存器的长度大于或等于所述第一长度与所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度之和的总和。

[0115]

当读写优先级最高的移位寄存器中的数据到达第一长度时,需要将第一长度的待存储数据写入到存储器的目标地址中。根据前文中的描述,将移位寄存器中的数据写入到存储器与将接收的数据到移位寄存器的操作是同步进行的。因此,在执行对存储器的读写的同时,移位寄存器还需要不断存入新的数据,为了确保存入的数据不会溢出,需要将移位寄存器中的数据项后移动。

[0116]

还以图11为例,第一长度为32llr,存储器的一个读写周期包括4个写入循环。因此多个移位寄存器中读写优先级最高的第一个移位寄存器的长度为36llr。

[0117]

在一些实施方式中,所述多个移位寄存器的每个移位寄存器的长度按照所述输入数据的写入顺序依次递增,所述多个移位寄存器中相邻的两个移位寄存器的长度的差值大于或等于所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度。

[0118]

当目标移位寄存器和相邻的前一个移位寄存器中的待存储数据均满足第一长度时,根据读写的优先级,相邻的前一个移位寄存器正在进行数据读写时,目标移位寄存器中所存储的数据需要向后移动,为新写入的数据腾出空间,以保证接收的数据不会丢失。直到所述前一个移位寄存器完成对待存储数据的读写,存储器处于读写空闲的状态时,才能将目标移位寄存器中的待存储数据写入存储器中对应的目标存储地址。

[0119]

在一些极端情况下,当多个移位寄存器中的待存储数据均满足第一长度且需要写

入同一地址时,读写优先级在后的移位寄存器需要在存储器的一个读写周期之后才能执行读写操作。因此每个移位寄存器与前一个移位寄存器的长度的差值都至少要大于一个读写周期内写入一个移位寄存器的数据的长度之和。

[0120]

还以图11为例,存储器的读写周期包括4个循环。因此,相邻的移位寄存器的长度的差值应最少为4llr bit,以保证数据不会丢失,图中的8个移位寄存器的长度分别为36、36、40、44、48、52、56和60个llr bits,因此,图11中的第一寄存器共需要372llrbit的移位寄存器资源,此时的解速率匹配的读写时序如图12所示。

[0121]

上文结合图1-图12,详细描述了本技术的方法实施例。下面描述本技术的装置实施例。应理解,装置实施例的描述与方法实施例的描述相互对应,因此,为详细描述的部分可以参见前面的方法实施例。

[0122]

本技术实施例提供了一种解速率匹配的装置,该装置可以为前文中所述的装置900,包括:

[0123]

第一寄存器910,包括:多个移位寄存器分别与交织矩阵中的多行相对应。

[0124]

存储器920,包括多个存储地址用于存储解速率匹配后的数据。

[0125]

第二寄存器930,存储有多个状态指示符,用于指示所述存储器92中的每个所述存储地址是否存有数据。

[0126]

处理器940,用于执行以下操作:将输入数据写入所述多个移位寄存器;

[0127]

确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址,所述目标移位寄存器为所述多个移位寄存器中的一个;

[0128]

当所述目标存储地址的状态指示符指示所述目标存储地址没有数据时,将所述待存储数据写入所述目标存储地址;

[0129]

当所述目标存储地址的状态指示符指示所述目标存储地址存有数据时,将所述待存储数据与所述目标存储地址中的数据合并后写入所述目标存储地址。

[0130]

可选地,所述待存储数据为满足第一长度的数据,所述第一长度大于或等于所述存储器的一个读写周期内存入所述多个移位寄存器的数据的长度之和。

[0131]

可选地,当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的起始数据,确定所述起始数据的偏移量,将所述起始数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址;当写入所述目标移位寄存器的数据为所述交织矩阵中每一行的末尾数据时,将所述末尾数据补齐到所述第一长度后,将所述待存储数据写入所述目标存储地址。

[0132]

可选地,所述多个移位寄存器的读写优先级按照所述输入数据的写入顺序依次递减。

[0133]

可选地,所述多个移位寄存器的每个移位寄存器的长度按照所述输入数据的写入顺序依次递增,所述多个移位寄存器中相邻的两个移位寄存器的长度的差值大于或等于所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度之和。

[0134]

可选地,所述多个移位寄存器中所述读写优先级最高的移位寄存器的长度大于或等于所述第一长度与所述存储器的一个读写周期内存入所述目标移位寄存器的数据的长度之和的总和。

[0135]

可选地,所述存储器的宽度大于或等于所述第一长度。

[0136]

可选地,所述输入数据包括有效数据和循环数据;所述确定所述目标移位寄存器中的待存储数据在所述存储器中的目标存储地址包括:根据所述输入数据的长度、所述有效数据的长度、所述第一长度和所述交织矩阵的行数确定所述待存储数据在所述存储器中的目标存储地址。

[0137]

图13是本技术实施例提供的终端设备的结构示意图。图13所示的装置1300可以是能够执行解速率匹配的终端设备。该装置1300可以是通信系统中的接收端,例如,可以是用户设备(user equipment,ue)、接入终端、用户单元、用户站、移动站、移动台(mobile station,ms)、移动终端(mobile terminal,mt)、远方站、远程终端、移动设备、用户终端、终端、无线通信设备、用户代理或用户装置等。装置1300可以包括处理器1310、和存储器1320,其中存储器1320中存储有所述处理器1310可执行指令,当所述指令被所述处理器1320执行时,实现前文描述的各个方法的步骤。在一些实施方式中,该终端设备1300还可以包括网络接口1330,处理器1320与外部设备的数据交换可以通过该网络接口1330实现。

[0138]

本技术实施例还提供了一种芯片,所述芯片包括可编程逻辑电路和/或程序指令,当所述芯片运行时,实现前文描述的各个方法的步骤。

[0139]

本技术实施例还提供了一种计算机可读存储介质,其上存储有程序,所述程序被处理器执行时,实现前文描述的各个方法的步骤。

[0140]

应理解,在本技术实施例中,“与a相应的b”表示b与a相关联,根据a可以确定b。但还应理解,根据a确定b并不意味着仅仅根据a确定b,还可以根据a和/或其它信息确定b。

[0141]

应理解,本文中术语“和/或”,仅仅是一种描述关联对象的关联关系,表示可以存在三种关系,例如,a和/或b,可以表示:单独存在a,同时存在a和b,单独存在b这三种情况。另外,本文中字符“/”,一般表示前后关联对象是一种“或”的关系。

[0142]

应理解,在本技术的各种实施例中,上述各过程的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本技术实施例的实施过程构成任何限定。

[0143]

在本技术所提供的几个实施例中,应该理解到,所揭露的系统、装置和方法,可以通过其它的方式实现。例如,以上所描述的装置实施例仅仅是示意性的,例如,所述单元的划分,仅仅为一种逻辑功能划分,实际实现时可以有另外的划分方式,例如多个单元或组件可以结合或者可以集成到另一个系统,或一些特征可以忽略,或不执行。另一点,所显示或讨论的相互之间的耦合或直接耦合或通信连接可以是通过一些接口,装置或单元的间接耦合或通信连接,可以是电性,机械或其它的形式。

[0144]

所述作为分离部件说明的单元可以是或者也可以不是物理上分开的,作为单元显示的部件可以是或者也可以不是物理单元,即可以位于一个地方,或者也可以分布到多个网络单元上。可以根据实际的需要选择其中的部分或者全部单元来实现本实施例方案的目的。

[0145]

另外,在本技术各个实施例中的各功能单元可以集成在一个处理单元中,也可以是各个单元单独物理存在,也可以两个或两个以上单元集成在一个单元中。

[0146]

在上述实施例中,可以全部或部分地通过软件、硬件、固件或者其任意组合来实现。当使用软件实现时,可以全部或部分地以计算机程序产品的形式实现。所述计算机程序产品包括一个或多个计算机指令。在计算机上加载和执行所述计算机程序指令时,全部或

部分地产生按照本技术实施例所述的流程或功能。所述计算机可以是通用计算机、专用计算机、计算机网络、或者其他可编程装置。所述计算机指令可以存储在计算机可读存储介质中,或者从一个计算机可读存储介质向另一个计算机可读存储介质传输,例如,所述计算机指令可以从一个网站站点、计算机、服务器或数据中心通过有线(例如同轴电缆、光纤、数字用户线(digital subscriber line,dsl))或无线(例如红外、无线、微波等)方式向另一个网站站点、计算机、服务器或数据中心进行传输。所述计算机可读存储介质可以是计算机能够读取的任何可用介质或者是包含一个或多个可用介质集成的服务器、数据中心等数据存储设备。所述可用介质可以是磁性介质,(例如,软盘、硬盘、磁带)、光介质(例如,数字通用光盘(digital video disc,dvd))或者半导体介质(例如,固态硬盘(solid state disk,ssd))等。

[0147]

以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述1权利要求的保护范围为准。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1