过抹除校正方法及使用该方法的存储器装置与流程

1.本发明关于一种存储器装置,特别是一种过抹除校正方法及使用该方法的存储器装置。

背景技术:

2.闪存广泛应用于各种电子装置以提供非挥发性的数据存储。闪存包含存储器区块,可供编程、抹除及读取,每个存储器区块可设为抹除状态或编程状态。

3.在抹除操作中,通常是以存储器区块为单位,首先被预编程至编程状态以将一存储器区块的所有存储器单元设于已知水平,接着施加抹除脉冲至存储器区块一定时间以除去存储器区块之存储器单元的电荷以将存储器区块设为抹除状态,最后施加过抹除校正至存储器区块以缩小存储器区块中存储器单元的临界值电压的分布。然而闪存于过抹除校正完成前被关闭时,过抹除的存储器单元将保持未校正状态,在电力开启后,由于过抹除的存储器单元会持续抽取背景漏电流,而导致从闪存读取的数据发生错误。例如,对于耦接于同一条位线的512个存储器单元,若位线上有大量被过抹除的存储器单元,而且被过抹除的存储器单元在未被选定时持续抽取漏电流,在位线上累积的电流可能超过存储器单元读取电流,造成从闪存读取的数据发生错误。此外,漏电流可能在编程过程中造成功率损耗及使位线供电过载。

4.因此需要提供一种过抹除校正方法及使用该方法的存储器装置,用以在电力开启后执行快速的过抹除校正,从而减少不必要的功耗损失,减少错误的数据读取及提高编程性能。

技术实现要素:

5.本发明实施例提供一种过抹除校正方法,用于存储器装置中。存储器装置包含多个存储器区块,每个存储器区块包含多行的存储器单元,每行存储器单元耦接于对应位线。过抹除校正方法包含在电力开启序列完成后,检测一组存储器区块中多个对应行的漏电流是否大于预定水平,其中该组存储器区块包含多个存储器区块的(i+1)个存储器区块,i为正整数;及若该组存储器区块中的多个对应行的漏电流大于预定水平时,对多个对应行执行过抹除校正。

6.本发明实施例提供另一种过抹除校正方法,存储器装置包含多个存储器区块,每个存储器区块包含多行的存储器单元,每行存储器单元耦接于对应位线。过抹除校正方法包含在电力开启序列完成后,检测一组存储器区块中的多个对应行的漏电流是否大于预定水平,其中该组存储器区块包含多个存储器区块的(i+1)个存储器区块,i为正整数,若该组存储器区块中的多个对应行的漏电流大于预定水平时,检测组存储器区块中的哪个存储器区块是漏电存储器区块;及对漏电存储器区块的对应行执行过抹除校正。

7.本发明实施例提供另一种存储器装置,包含多条位线、一组存储器区块及控制器。该组存储器区块耦接于多条位线,包含(i+1)个存储器区块,i为正整数,每个存储器区块包

含多行的存储器单元及多个区块选择开关,多个区块选择开关分别耦接于多行的存储器单元,每行存储器单元耦接于对应位线。控制器耦接于该组存储器区块,及用以在电力开启序列完成后,选择多个区块选择开关以检测组存储器区块中多个对应行的漏电流是否大于预定水平。

附图说明

8.图1是根据本发明实施例的存储器装置的方块图。

9.图2显示图1中存储器装置的抹除状态的临界值电压分布曲线。

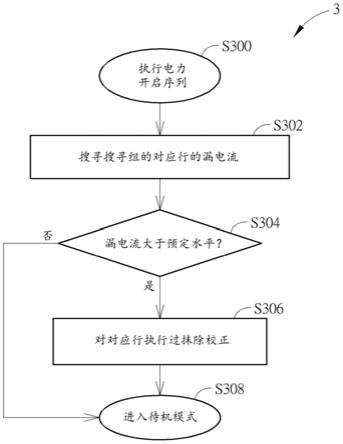

10.图3是图1中存储器装置使用的过抹除校正方法的流程图。

11.图4是图1的存储器装置的存储器区块的示意图。

12.图5是图1中存储器装置中使用的另一过抹除校正方法的流程图。

13.图6是图1中存储器装置中使用的另一过抹除校正方法的流程图。

具体实施方式

14.图1是根据本发明实施例的存储器装置1的方块图。存储器装置1可以是nor型闪存。在电力开启后,存储器装置1可判定是否存在一个或多个过抹除的存储器单元,并且在检测到过抹除的存储器单元后执行过抹除校正,从而防止由于过抹除的存储器单元抽取漏电流而导致存储器装置1的数据读取失败的情况。图2显示存储器装置1中的存储器单元的过抹除状态及过抹除校正状态的临界值电压分布曲线20及22,横轴表示临界值电压,纵轴表示存储器单元的数量。在抹除操作之后,阴影区域200的过抹除存储器单元的临界值电压可低于抹除状态的最小期望临界值电压(例如0v),且电压脉冲可被施加于过抹除存储器单元以使临界值电压回到最小期望临界值电压之上。将过抹除存储器单元的临界值电压带回最小期望临界值电压之上的操作称为过抹除校正程序。

15.参考图1,存储器装置1包含多条区块选择线bsel[0]至bsel[2i+1],多条位线bl0[0]至bl(2i+1)[n],多条全局位线gbla[0]至gbla[n],gblb[0]至gblb[n]及多条字线wl0[0]至wl(2i+1)[m],n和m为正整数。例如,i可以是3,n可以是1023及m可以是127,用于具有8个区块选择线,8192位线和1024字线的存储器装置1。存储器装置1还包含存储器阵列10、控制器12、传感电路14、列解码器16及行解码器18。存储器阵列10耦接于列解码器16及行解码器18。控制器12耦接于列解码器16、行解码器18及传感电路14。传感电路14耦接于行解码器18。

[0016]

存储器阵列10包含以行及列布置的存储器区块blk[0]至blk[2i+1]。例如,1mb的存储器装置1可分成每个128kb的8个存储器区块,每个存储器区块可布置为1k行及128列。区块选择线bsel[0]至bsel[2i+1]上之控制讯号可分别选择存储器区块blk[0]至blk[2i+1]。存储器区块blk[0]至blk[2i+1]可组织为搜寻组100a及100b,其中每个搜寻组包含(i+1)个存储器区块,且i为正整数。例如,i可以是3,即每个搜寻组可含有4个存储器区块。存储器区块blk[0]至blk[2i+1]可包含区块选择开关sw0[0]至sw(2i+1)[n]。多条位线bl0[0]至bl(2i+1)[n]可分为多个组位线bl0[0]至bl0[n];..;bli[0]至bli[n];bl(i+1)[0]至bl(i+1)[n];...;bl(2i+1)[0]至bl(2i+1)[n]。每组位线可用于定址特定存储器区块中的行。例如位线组bli[0]至bli[n]可用于定址存储器区块blk[i]中的行。全局位线gbla[0]至gbla

[n],gblb[0]至gblb[n]可经由位线bl0[0]至bl(2i+1)[n]耦接于搜寻组100a及100b中的对应行。例如全局位线gbla[0]经由位线bl0[0]至bli[0]耦接于搜寻组100a中的对应行。每个存储器区块的区块选择开关可耦接于定址存储器区块的位线组。举例来说,存储器区块blk[0]可包含区块选择开关sw0[0]至sw0[n],分别耦接于位线组bl0[0]至bl0[n]。区块选择开关sw0[0]至sw(2i+1)[n]导通时,对应的存储器区块blk[0]至blk[2i+1]可被选择;当区块选择开关sw0[0]至sw(2i+1)[n]不导通时,对应的存储器区块blk[0]至blk[2i+1]可被取消选择。区块选择开关sw0[0]至sw(2i+1)[n]可分别控制从位线bl0[0]至bl(2i+1)[n]到行解码器18及传感电路14的耦接。例如,区块选择开关sw0[0]至sw0[n]可控制行解码器18及传感电路14到位线bl0[0]至bl0[n]的耦接。

[0017]

列解码器16可经由区块选择线bsel[0]至bsel[2i+1]耦接于区块选择开关sw0[0]至sw(2i+1)[n],用以选择一个或多个存储器区块blk[0]至blk[2i+1]。列解码器16可经由字线wl0[0]至wl(2i+1)[m]另耦接于存储器区块blk[0]至blk[2i+1],用以将适当电位施加于选定列,以对选定的存储器单元执行读取、编程、抹除及过抹除校正。行解码器18可通过位线bl0[0]至bl(2i+1)[n]耦接于存储器区块blk[0]至blk[2i+1]以选择将电流从选定的行传送至传感电路14。传感电路14可使用全局位线gbla[0]至gbla[n],gblb[0]至gblb[n]检测搜寻组内的所有选定行的对应累积漏电流。例如,当行解码器18选定位线bl0[3]至bli[3],传感电路14可通过全局位线gbla[3]检测流经存储器区块blk[0]至blk[i]的所有第四行的累积漏电流。传感电路14可以是16位的传感放大器,能够在操作中检测16个选定行抽取到的16组电流,或可以是多位的传感放大器,能够在操作中检测以16为倍数的选定行抽取到的以16组为倍数的电流,例如16位的倍数可以是32位。例如,当行解码器18分别选择位线bl0[0]至bli[0],...,bl0[15]至bli[15],传感电路14可经由全局位线gbla[0]至gbla[15]检测流经区块blk[0]至blk[i]的前16行的16组累积漏电流。

[0018]

控制器12可控制列解码器16、行解码器18及传感电路14的操作以对选定的存储器单元进行读取、编程、抹除、过抹除验证、过抹除校正,及其他验证操作。

[0019]

虽然实施例中的存储器装置1仅显示2个搜寻组100a和100b,然而存储器阵列10可使用任何数目的搜寻组。存储器装置1的详细操作将在后续段落的过抹除校正方法3、4、5说明。

[0020]

图3是存储器装置1使用的过抹除校正方法3的流程图。过抹除校正方法3包含步骤s300至s308,其中步骤s300及s308分别是过抹除校正方法3的起始步骤及结束步骤,步骤s302至s304用于执行过抹除验证,步骤s306用于执行过抹除校正。任何合理的技术变更或是步骤调整都属于本发明所揭露的范畴。步骤s300至s308的解释如下:

[0021]

步骤s300:执行电力开启序列;

[0022]

步骤s302:检测搜寻组的漏电流;

[0023]

步骤s304:漏电流是否大于预定水平?若漏电流大于预定水平,则执行步骤s306,若否,则执行步骤s308;

[0024]

步骤s306:对对应行执行过抹除校正;

[0025]

步骤s308:进入待机模式。

[0026]

电源开启后,存储器装置1在特定时间区间内执行特定步骤序列用以确保存储器装置1可正确执行后续操作,该特定步骤序列称为电源开启序列(s300)。一旦电源开启序列

完成后,控制器12同时选择搜寻组100a的区块选择开关sw0[0]至swi[n]及位线bl0[n]至bli[n]以搜索搜寻组100a中的第n+1行的漏电流(s302)。接着,传感电路14检测搜寻组100a的第n+1行的漏电流是否大于预定水平(s304)。预定水平的值可基于不引起闪存失效的位线的漏电流而进行选择,并且可以是2ua。若漏电流小于预定水平时,则代表第n+1行并没有过抹除的存储器单元,存储器装置1进入待机模式。在待机模式中,存储器装置1中的数据准备好接受存取(s308)。若漏电流大于预定水平时,则辨识到过抹除状况,且控制器12对搜寻组100a执行过抹除校正,通过对搜寻组100a施加过抹除校正脉冲而将过抹除的存储器单元的临界值电压拉回至抹除状态的最小期望临界值电压以上(s306)。过抹除校正操作可基于搜寻组或存储器区块执行,分别在第5图及第6图中详细说明。在一些实施例中会对搜寻组100a的剩余行及搜寻组100b的每一行重复步骤s302,s304及s306,以校正存储器阵列10中的过抹除单元。过抹除状况被校正之后,存储器装置1进入待机模式(s308)。

[0027]

图4是存储器装置1的存储器区块blk[0]的示意图。存储器区块blk[0]包含多个存储器单元mc(0,0)至mc(n,m)及区块选择开关sw0[0]至sw0[n]。存储器单元mc(0,m)至mc(n,m)分别耦接于位线bl0[0]至bl0[n],且存储器单元mc(n,0)至mc(n,m)分别耦接于字线wl0[0]至wl0[m]。在过抹除验证中的实施例中,控制器12可经由列解码器16对字线wl0[0]至wl0[m]施加抹除状态的最小期望临界值电压,例如0v或几百微伏来选择字线wl0[0]至wl0[m],同时经由行解码器18选择一行或多行以使传感电路14检测选定行内的漏电流。在过抹除校正的实施例中,控制器12可经由行解码器18向选定行施加过抹除校正脉冲,同时经由列解码器16向所有字线wl0[0]到wl0[m]施加最小期望临界值电压。因此仅有过抹除的单元会被导通以接收过抹除校正脉冲,而正确抹除的单元将维持不导通状态而不受过抹除校正脉冲的校正。过抹除校正脉冲的大小可小于编程脉冲。

[0028]

图5是存储器装置1中使用的另一过抹除校正方法5的流程图。过抹除校正方法5用于基于搜寻组来检测及校正过抹除状况。过抹除校正(over-erasure correction,oec)方法5包含步骤s500至s522。步骤s500及s522分别是过抹除校正方法5的开始步骤及结束步骤,步骤s502至s510用以对搜寻组执行过抹除验证,及步骤s512至s520被用以对漏电搜寻组执行过抹除校正。任何合理的技术变更或是步骤调整都属于本发明所揭露的范畴。步骤s500至s522的解释如下:

[0029]

s500:执行电力开启序列;

[0030]

s502:对搜寻组执行过抹除验证;

[0031]

s504:已发现漏电搜寻组?若是,则执行步骤s512,若否,则执行步骤s506;

[0032]

s506:已到达搜寻组的最后一条位线?若是,则执行步骤s508,若否,则执行步骤s507;

[0033]

s507:选择下一条位线;执行步骤s502;

[0034]

s508:已到达最后搜寻组?若是,则执行步骤s522,若否,则执行步骤s510;

[0035]

s510:选择下一个搜寻组;执行步骤s502;

[0036]

s512:对漏电搜寻组执行过抹除校正;

[0037]

s514:对校正后的搜寻组执行过抹除验证;

[0038]

s516:过抹除验证失败?若验证是,则执行步骤s512,若否,执行步骤s518;

[0039]

s518:已到达搜寻组的最后一条位线?若是,则执行步骤s522,若否,执行步骤

s520;

[0040]

s520:选择下一条位线;执行步骤s514;

[0041]

s522:进入待机模式。

[0042]

首先在存储器装置1执行电力开启序列(s500)。电力开启序列完成后,控制器12藉由透过列解码器16选择区块选择开关sw0[0]至sw0[n]及透过行解码器18选择搜寻组100a的前16个对应行进行过抹除验证上以使传感电路14检测搜寻组100a的前16个对应行的16组漏电流(s502),及藉由检测前16个对应行的16组漏电流是否有任何一者大于预定水平来判断搜寻组100a是否是漏电搜寻组。若前16个对应行的16组漏电流中有任何一者大于预定水平,控制器12判断搜寻组100a是漏电搜寻组,若前16个对应行的16个漏电流都没有大于预定水平,控制器12判断搜寻组100a不是漏电搜寻组。预定水平的值可基于不引起闪存失效的位线的漏电流而进行选择,并且可以是2ua。当搜寻组100a不是漏电搜寻组,则控制器12判断是否已经到达搜寻组100a的最后位线(s506),若尚未到达,控制器12选择搜寻组100a的下16个对应行所耦接的下16条位线(s507),并重复步骤s502和s504以搜寻搜寻组100a的下16个对应行的漏电流。若漏电流都没有超过预定水平,控制器12对搜寻组100a的剩余对应行重复步骤s502至s507。若已经到达搜寻组100a的最后位线且尚未发现漏电搜寻组,控制器12进一步判断是否已经到达最后搜寻组100b(s508)。若已经到达最后搜寻组100b,则已搜索过存储器装置1中的所有搜寻组且未发现过抹除单元,存储器装置1进入待机模式,并准备好后续操作(s522)。若尚未到达最后搜寻组100b,则控制器12藉由选择区块选择开关sw(i+1)[0]至sw(i+1)[n]来选择下一个搜寻组100b,及重复步骤s502至s510,直到已对最后搜寻组100b的最后位线bl(2i+1)[n]完成过抹除验证,且在步骤s522存储器装置1进入待机模式。

[0043]

若在步骤s504中,已辨识搜寻组100a中为漏电搜寻组,则控制器12藉由对搜寻组100a的所有区块blk[0]至blk[i]的16个对应行施加过抹除校正脉冲而对漏电搜寻组100a执行过抹除校正(s512),藉由选择搜寻组100a的16个对应行来对搜寻组100a执行过抹除验证以使传感电路14检测16个对应行的漏电流及判断是否仍有漏电流超出预定水平(s514)。接着控制器12依据漏电流大小判断过抹除验证是否失败(s516)。若漏电流超过预定水平,控制器12判断过抹除验证失败,且如果漏电流小于预定水平,则控制器12判断过抹除验证成功。控制器12重复步骤s512到s516,直到过抹除验证成功为止。若过抹除验证成功,则控制器12判断是否已经到达搜寻组100a最后位线(s518),若尚未到达,控制器12选择连接到搜寻组100a的下16个对应行所耦接的下16条位线(s520),并重复步骤s512至s520以对搜寻组100a的下16个对应行执行过抹除验证及过抹除校正。若在步骤s518中控制器12判断已到达搜寻组100a的最后位线bl0[n]至bli[n]时,则控制器12进入待机模式(s522)。

[0044]

图6是存储器装置1中使用的另一过抹除校正方法6的流程图。过抹除校正方法6基于存储器区块检测及校正过抹除状况。过抹除校正方法6包含步骤s600至s630。步骤s600及s630分别是过抹除校正方法6的开始步骤及结束步骤,步骤s602至s610用以对搜寻组执行过抹除验证,步骤s612至s618用以对漏电搜寻组的存储器区块执行过抹除验证,及步骤s620至s628用以对漏电存储器区块执行过抹除校正。任何合理的技术变更或是步骤调整都属于本发明所揭露的范畴。步骤s600至s630的解释如下:

[0045]

s600:执行电力开启序列;

[0046]

s602:对搜寻组执行过抹除验证;

[0047]

s604:已发现漏电搜寻组?若是,则执行步骤s612,若否,则执行步骤s606;

[0048]

s606:已到达搜寻组的最后一条位线?若是,则执行步骤s608,若否,则执行步骤s607;

[0049]

s607:选择下一条位线;执行步骤s602;

[0050]

s608:已到达最后搜寻组?若是,则执行步骤s630,若否,则执行步骤s610;

[0051]

s610:选择下一个搜寻组;执行步骤s602;

[0052]

s612:对存储器区块执行过抹除验证;

[0053]

s614:已发现漏电存储器区块?若是,则执行步骤s620,若否,则执行步骤s616;

[0054]

s616:已到达搜寻组的最后一个存储器区块?若是,则执行步骤s606,若否,则执行步骤s618;

[0055]

s618:选择下一个存储器区块;执行步骤s612;

[0056]

s620:对漏电存储器区块执行过抹除校正;

[0057]

s622:对漏电存储器区块执行过抹除验证;

[0058]

s624:过抹除验证失败?若是,则执行步骤s620,若否,则执行步骤s626;

[0059]

s626:已到达搜索组的最后一条位线?若是,则执行步骤s630,若否,则执行步骤s628;

[0060]

s628:选择下一条位线;执行步骤s622;

[0061]

s630:进入待机模式。

[0062]

步骤s600至s610与步骤s500至s510相同,步骤s630与步骤s522相同,因此不再赘述。一旦检测到漏电搜寻组的对应行,例如搜寻组100a的存储器区块blk[0]至blk[i]的第33行,控制器12藉由选择存储器区块blk[0]的第33对应行耦接的位线bl0[32]同时取消选择搜寻组100a的剩余存储器区块blk[1]至blk[i]的第33对应行耦接的位线bl1[32]至bli[32],以透过位线bl0[32]对存储器区块blk[0]的第33对应行执行过抹除验证,让传感电路10检测位线bl0[32]的漏电流,进而判断搜寻组100a中的存储器区块blk[0]是否为漏电存储器区块(s612)。控制器12接着藉由检测存储器区块blk[0]的第33对应行的漏电流是否大于预定水平来判断存储器区块blk[0]是否为漏电存储器区块(s614)。预定水平的值可基于不引起闪存失效的位线的漏电流而进行选择,并且可以是2ua。若漏电流大于预定水平,控制器12判断存储器区块blk[0]是漏电存储器区块,若漏电流小于预定水平,控制器12判断存储器区块blk[0]不是漏电存储器区块。当存储器区块blk[0]不是漏电存储器区块,控制器12判断是否已经到达搜寻组100a的最后存储器区块blk[i](s616),若否,则控制器12选择搜寻组100a的下一个存储器区块blk[1]耦接到的位线bl1[32](s618),同时取消选择剩余存储器区块blk[0],blk[2]至blk[i]的第33对应行耦接到的位线bl0[32],bl2[32]到bli[32],并重复步骤s612及s614以搜寻存储器区块blk[1]的对应行的漏电流。控制器12对搜寻组100a中剩余存储器区块blk[2]至blk[i]的第33对应行重复步骤s612至s618。若从存储器区块blk[0]至blk[i]的第33对应行都没有找到漏电存储器区块,则控制器12继续步骤s606,以搜索搜寻组100a第33对应行之后的后续对应行的漏电。

[0063]

若在一个存储器区块中检测到漏电流,则代表检测到漏电存储器区块,且控制器12执行步骤s620至s628来校正漏电存储器区块的临界值电压。在一个实施例中,存储器区

块blk[1]已被检测为漏电存储器区块,且控制器12执行步骤s620到s628,以校正漏电存储器区块blk[1]中过抹除行的临界值电压。控制器12藉由对漏电存储器区块blk[1]的对应行施加过抹除校正脉冲而对漏电存储器区块blk[1]执行过抹除校正(s620),及藉由选择存储器区块blk[1]的对应行及判断是否仍有超出预定水平的漏电流而对校正后的存储器区块blk[1]执行过抹除验证(s622)。控制器12依据漏电流大小判断过抹除验证是否失败(s624)。若漏电流超过预定水平,控制器12判断过抹除验证失败,且如果漏电流小于预定水平,则控制器12判断过抹除验证成功。控制器12重复步骤s620到s624,直到漏电存储器区块blk[1]的对应行的漏电流小于预定水平及过抹除验证成功为止。若过抹除验证成功,则控制器12判断是否已经到达存储器区块blk[1]的最后位线(s626),若尚未到达,控制器12选择存储器区块blk[1]的下个对应行所耦接的下条位线(s628),并重复步骤s620至s628以对存储器区块blk[1]的下个对应行执行过抹除验证及过抹除校正。控制器12对漏电存储器区块blk[1]的剩余行重复步骤s620至s628,判断漏电存储器区块blk[1]的对应行之后的漏电存储器区块blk[1]的剩余行是否具有超过预定水平的漏电流,及对漏电存储器区块blk[1]的剩余行施加至少一个过抹除校正脉冲直到剩余行的漏电流小于预定水平为止。若在步骤s626中控制器12判断已到达漏电存储器区块blk[1]的最后位线bl1[n]时,则控制器12进入待机模式(s630)。

[0064]

因此,存储器装置1及过抹除校正方法3、5、6用以基于搜寻组执行过抹除验证及基于搜寻组或存储器区块执行过抹除校正,从而提供快速准确的过抹除校正,减少不必要的功耗损失,减少错误的数据读取及提高编程性能。

[0065]

以上所述仅为本发明的较佳实施例,凡依本发明权利要求书所做的均等变化与修饰,皆应属本发明的涵盖范围。

[0066]

[符号说明]

[0067]

1 存储器装置

[0068]

10 存储器阵列

[0069]

100a及100b 搜寻组

[0070]

12 控制器

[0071]

14 传感电路

[0072]

16 列解码器

[0073]

18 行解码器

[0074]

20、22 临界值电压分布曲线

[0075]

200 阴影区域

[0076]

3、5、6 过抹除校正方法

[0077]

s300至s308、s500至s522、s600至s630 步骤

[0078]

bl0[0]至bl(2i+1)[n] 位线

[0079]

blk[0]至blk[2i+1] 存储器区块

[0080]

bsel[0]至bsel[2i+1] 区块选择

[0081]

gbla[0]至gbla[n]、gblb[0]至gblb[n] 全局位线

[0082]

mc(0,0)至mc(n,m) 存储器单元

[0083]

sw0[0]至sw(2i+1)[n] 区块选择开关

[0084]

wl0[0]至wl(2i+1)[m] 字线

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1