三态内容可寻址存储器及其存储单元的制作方法

1.本发明属于存储技术领域,涉及一种三态内容可寻址存储器及其存储 单元,且特别是有关于一种闪存存储器形式的三态内容可寻址存储器及其 存储单元。

背景技术:

2.在现有技术中,三态内容可寻址存储器常基于静态随机存取存储器的 架构来设置,并常应用在网络交换机上。这种情况下,三态内容可寻址存 储单元需要多个(16个)晶体管来建构,并耗去大量的电路面积,并导致 相对高的电力消耗。如此,造成在有电力消耗限制的应用上的限制。

3.在部分现有技术中,可应用电阻式存储器来建构三态内容可寻址存储 器。在这样的应用下,常由于晶体管的导通及截止电阻的差异不够大,导 致不同状态的匹配信号所具有的电压差异不够明显,而产生的感测结果判 断上的困难。降低了三态内容可寻址存储器的工作效率。

技术实现要素:

4.本发明提供一种三态内容可寻址存储单元及其存储单元,可提高存储 单元的高密度且降低所需的静态功率消秏。

5.本发明的三态内容可寻址存储单元包括第一晶体管以及第二晶体管。 第一晶体管具有栅极端接收选择信号,第一晶体管的第一端耦接至匹配 线,第一晶体管的第二端耦接至源极线。第二晶体管具有栅极端接收反向 选择信号,第二晶体管的第一端耦接至匹配线,第二晶体管的第二端耦接 至源极线。其中,第一晶体管以及第二晶体管都具有电荷储存结构。

6.本发明的三态内容可寻址存储器包括多条选择线、多条匹配线以及存 储单元阵列。存储单元阵列具有多个存储单元,并形成多个存储单元行以 及多个存储单元列。其中,各存储单元具有相互并联的第一晶体管以及第 二晶体管,第一晶体管以及第二晶体管都具有电荷储存结构。其中,存储 单元列分别耦接选择线,存储单元行分别耦接匹配线。

7.基于上述,本发明提供闪存存储单元结构来建构三态内容可寻址存储 单元。由此,三态内容可寻址存储单元的结构有效被简化,可实现高密度 的布局。且本发明实施例的三态内容可寻址存储单元在匹配的条件下可维 持低量的电流消耗,降低静态功率消耗。在非匹配的条件则可以快速反应, 即时提供正确的匹配信号。

附图说明

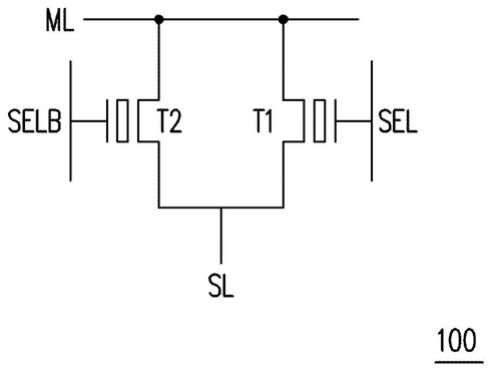

8.图1是本发明实施例的三态内容可寻址存储单元的示意图。

9.图2a为本发明实施的三态内容可寻址存储单元的匹配信号的波形 图。

10.图2b为本发明实施例的三态内容可寻址存储单元中的晶体管的特性 曲线图。

11.图3为本发明实施例的三态内容可寻址存储单元的一实施方式的示意 图。

12.图4为本发明实施例的三态内容可寻址存储单元的另一实施例的示意 图。

13.图5为本发明图4实施例的三态内容可寻址存储单元中的晶体管的特 性曲线图。

14.图6a以及图6b分别为本发明不同实施例的三态内容可寻址存储单 元的示意图。

15.图7为本发明一实施例的三态内容可寻址存储器的示意图。

16.图8为本发明图7实施例的三态内容可寻址存储器的搜寻动作的示意 图。

17.图9为本发明图7实施例的三态内容可寻址存储器的擦除动作的示意 图。

18.【符号说明】

19.100、300、400、600:三态内容可寻址存储单元

20.301、401、601:感测放大器

21.310、410、611:预充电电路

22.700:三态内容可寻址存储器

23.710:存储单元阵列

24.721~72n:预充电电路

25.730:感测放大器

26.740:缓冲器

27.750:源极线驱动器

28.760:编码器

29.eg1:擦除栅极

30.g1~g4:栅极

31.mc11~mcnm:存储单元

32.ml、ml1~mln:匹配线

33.mls1、mls2、201、202、510、520:曲线

34.sa_

out

:感测结果

35.sel、sel1~selm:选择信号

36.selb、sel1b~selmb:反向选择信号

37.sl、sl1~sln:源极线

38.st:启动信号

39.t1、t2、t3、t41、t42、t61~t64、t11、t12、t21、t22:晶体管

40.vm:预充电压

41.vref:参考电压

42.vsh:搜寻电压

43.wl1、wl1’:字线信号

具体实施方式

44.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实 施例,并参照附图,对本发明进一步详细说明。

45.请参照图1,图1是本发明实施例的三态内容可寻址存储单元的示意 图。三态内容可寻址存储单元100包括晶体管t1以及t2。晶体管t1具 有栅极端以接收选择信号sel,晶体管t1的第一端(例如漏极端)耦接 至匹配线ml,晶体管t1的第二端(例如源极端)耦接至源

极线sl。另 外,晶体管t2具有栅极端以接收反向选择信号selb,晶体管t2的第一 端(例如漏极端)耦接至匹配线ml,晶体管t1的第二端(例如源极端) 耦接至源极线sl,其中,晶体管t1、t2形成并联的状态。在本实施例中 晶体管t1、t2都具有电荷储存结构。晶体管t1、t2可形成浮动栅极 (floating gate)闪存存储单元、铁电场效晶体管(ferroelectric field-effecttransistor)存储单元、电荷储存式(sonos)闪存存储单元或浮点(floatingdot)闪存存储单元。

46.在数据储存时,针对三态内容可寻址存储单元100,当所要写入的数 据为逻辑0时,可针对晶体管t2、t1分别写入逻辑0、1;当所要写入的 数据为逻辑1时,可针对晶体管t2、t1分别写入逻辑1、0。另外,若三 态内容可寻址存储单元100所要写入的数据为不在乎(don’t care)时, 则可针对晶体管t2、t1写入逻辑1、1。

47.而在针对三态内容可寻址存储单元100进行数据搜寻动作时,首先可 针对匹配线ml进行预充电动作,并使匹配线ml上的匹配信号为一预充 电压。当要进行逻辑0的搜寻,可使反向选择信号selb为逻辑0,使选 择信号sel为搜寻电压。在此时,若晶体管t2、t1储存的数据分别为逻 辑0、1(表示三态内容可寻址存储单元100储存逻辑0),晶体管t1、t2 均不被导通(均被截止),匹配线ml上的匹配信号可维持预充电压,并 表示此次的搜寻结果为符合(match)。

48.相对的,若晶体管t2、t1储存的数据分别为逻辑1、0(表示三态内 容可寻址存储单元100储存逻辑1),晶体管t1可被导通,并使匹配线 ml上的匹配信号被拉低至为源极线sl上具有相对低电压的源极信号。 此时,匹配线ml上的匹配信号表示此次的搜寻结果为不符合(mismatch)。

49.在本实施例中,搜寻电压可以介于0.5伏特至1.5伏特间,预充电压 则可以介于0.6伏特至1.0伏特间。当然,上述的电压范围可以依据存储 单元实际接收的工作电压以及晶圆的工艺参数来进行设定,没有固定的限 制。

50.在另一方面,当要进行逻辑1的搜寻,可使反向选择信号selb为逻 辑1,使选择信号sel为搜寻电压。在此时,若晶体管t2、t1储存的数 据分别为逻辑1、0(表示三态内容可寻址存储单元100储存逻辑1),晶 体管t1、t2均不被导通(均被截止),匹配线ml上的匹配信号可维持预 充电压,并表示此次的搜寻结果为符合(match)。

51.相对的,若晶体管t2、t1储存的数据分别为逻辑0、1(表示三态内 容可寻址存储单元100储存逻辑0),晶体管t2可被导通,并使匹配线 ml上的匹配信号被拉低至为源极线sl上具有相对低电压的源极信号。 此时,匹配线ml上的匹配信号表示此次的搜寻结果为不符合(mismatch)。

52.另外,若晶体管t2、t1储存的数据分别为逻辑1、1(表示三态内容 可寻址存储单元100储存的数据为不在乎),晶体管t1、t2均会被截止, 匹配线ml上的匹配信号维持为预充电压,并表示此次的搜寻结果为符合 (match)。

53.附带一提的,针对晶体管t1、t2写入逻辑1、0的动作中,可通过针 对晶体管t1、t2进行编程(program)动作或擦除(erase)动作来完成。 其中,上述的编程动作可通过通道热载子注入(channel hot electroninjection,che)、源极端注入(source side injection)或f-n隧穿来完成。 擦除动作则可通过f-n隧穿或带-带热空穴(band-to-band hot hole, btbhh)入射来完成。

54.值得一提的,本发明实施例中,晶体管t1以及晶体管t2的任一个中, 其截止电阻与导通电阻的比值大于106。也因此,在当晶体管t1、t2均被 截止时,匹配线ml上的匹配信号不会因为晶体管t1、t2上的漏电现象 而产生电压值下降的不稳定现象。另外,当晶体管t1、t2的其中之一被 导通时,匹配线ml上的匹配信号也可被快速的拉低,并即时产生正确的 匹配信号。在此,可参照图2a,图2a为本发明实施的三态内容可寻址存 储单元的匹配信号的波形图。其中,当搜寻结果为符合时,匹配信号可为 曲线mls1并维持实质上等于预充电压。相对的,当搜寻结果为不符合时, 匹配信号可为曲线mls2,并快速的被拉低至源极电压。在此,源极电压 可以为参考接地电压。

55.值得注意的,通过判断匹配信号的电压值大于或小于一预设的参考电 压vref,可快速且清楚的判断出搜寻结果是否为符合。

56.另外,请参照图2b,图2b为本发明实施例的三态内容可寻址存储单 元中的晶体管的特性曲线图。其中,曲线201表示晶体管被写入数据0时 的特性曲线,曲线202则表示晶体管被写入数据1时的特性曲线。若针对 晶体管的栅极施加例如为1.5伏特的搜寻电压vsh时,被写入数据0的晶 体管被导通,并可产生相对高的电流ion。被写入数据1的晶体管被截止, 并可产生相对低的电流ioff,其中电流ion/ioff约等于106。

57.以下请参照图3,图3为本发明实施例的三态内容可寻址存储单元的 一实施方式的示意图。在图3中,三态内容可寻址存储单元300通过匹配 线ml耦接至预充电电路310,并耦接至感测放大器301。三态内容可寻 址存储单元300包括并联耦接的晶体管t1以及t2。本实施方式中的三态 内容可寻址存储单元300的架构与动作与图1实施例相同,在此不多赘述。

58.预充电电路310则由晶体管t3所建构。在本实施例中,晶体管t3可 以为p型晶体管,并依据启动信号st,在搜寻动作的初始时间区间中, 被导通以拉升匹配线ml上的匹配信号为预充电压vm。在完成匹配信号 的预充电动作后,晶体管t3可以被截止。

59.感测放大器301用以在搜寻动作中,使匹配线ml上的匹配信号与参 考电压vref进行比较,以产生指示搜寻动作为符合或不符合的感测结果 sa_

out

。其中,当匹配线ml上的匹配信号大于参考电压vref时,搜寻 动作为符合;相对的,当匹配线ml上的匹配信号小于参考电压vref时, 搜寻动作为不符合。

60.感测放大器301可应用本领域技术人员所熟知的任意感测放大电路来 实施。感测放大器301也可利用逻辑反相器来实施。其中,逻辑反相器的 阈值电压可作为参考电压vref。

61.以下请参照图4,图4为本发明实施例的三态内容可寻址存储单元的 另一实施例的示意图。在图4中,三态内容可寻址存储单元400耦接至预 充电电路410以及感测放大器401。三态内容可寻址存储单元400包括晶 体管t41以及t42。晶体管t41以及t42都为双栅极晶体管。晶体管t41 的第一栅极g1为浮动栅极,并接收选择信号sel。晶体管t41的第二栅 极g2则接收字线信号wl1。晶体管t42的第一栅极g3为浮动栅极,并 接收反向选择信号selb。晶体管t42的第二栅极g4则接收字线信号 wl1’。其中,第一栅极g1、g3具有电荷储存结构。

62.晶体管t41、t42的漏极端均耦接至匹配线ml,晶体管t41、t42的 源极端均耦接至源极线sl1。

63.三态内容可寻址存储单元400并具有擦除栅极eg1,用以接收擦除电 压。

64.在执行搜寻动作时,字线信号wl1、wl1’可被拉高,并使晶体管 t41、t42处于可被导通的状态。通过接收选择信号sel以及反向选择信 号selb,晶体管t41、t42可依据所储存的逻辑值以被导通或截止,并 对应产生匹配线ml上的匹配信号。

65.预充电电路410则由晶体管t3所建构。在本实施例中,晶体管t3依 据启动信号st,在搜寻动作的初始时间区间中,被导通以拉升匹配线ml 上的匹配信号为预充电压vm。在完成匹配信号的预充电动作后,晶体管 t3可以被截止。

66.感测放大器401用以在搜寻动作中,使匹配线ml上的匹配信号与参 考电压vref进行比较,以产生指示搜寻动作为符合或不符合的感测结果 sa_

out

。

67.关于晶体管t41、t42的导通或截止的判断机制,与图1实施例中所 陈述的内容相类似,在此不再赘述。

68.另外,请参照图5,图5为本发明图4实施例的三态内容可寻址存储 单元中的晶体管的特性曲线图。其中,曲线510表示晶体管被写入数据0 时的特性曲线,曲线520则表示晶体管被写入数据1时的特性曲线。若针 对晶体管的栅极施加例如为0.5伏特的搜寻电压vsh时,被写入数据0 的晶体管被导通,被写入数据1的晶体管被截止,且两晶体管(被导通的 晶体管与被截止的晶体管)间的电流比值约等于106。

69.在本实施例中,写入数据0的晶体管可通过过度擦除(over erase)的 方式来执行擦除的动作。在此条件下,写入数据0的晶体管的阈值 (threshold)电压可以低于0伏特,例如为-3伏特。

70.以下请参照图6a以及图6b,图6a以及图6b分别为本发明不同实 施例的三态内容可寻址存储单元的示意图。在图6a中,三态内容可寻址 存储单元600包括晶体管t61~t64。三态内容可寻址存储单元600通过匹 配线ml耦接至预充电电路611以及感测放大器601。在三态内容可寻址 存储单元600中,晶体管t61、t62具有电荷储存结构。晶体管t61与晶 体管t63串联耦接在匹配线ml以及源极线sl1间,晶体管t62与晶体 管t64串联耦接在匹配线ml以及源极线sl1间。晶体管t61与晶体管 t63的栅极分别接收选择信号sel以及字线信号wl,晶体管t62与晶体 管t64的栅极则分别接收反向选择信号selb以及字线信号wl’。

71.在搜寻动作被执行时,晶体管t63、t64作为开关,并分别依据字线 信号wl、wl’被导通。此时,晶体管t61、t62可基于所储存的数据, 依据分别接收的选择信号sel以及反向选择信号sleb以被导通或截止, 并在当晶体管t61、t62的其中之一被导通时,拉低匹配线ml上的匹配 信号,或者,并在当晶体管t61、t62接被截止时,维持匹配线ml上的 匹配信号为预充电电压vm。如此一来,感测放大器601可依据比较参考 电压vref以及匹配线ml上的匹配信号来产生感测结果。

72.晶体管t61~t64可沿着与匹配线ml平行的方向进行配置。

73.关于晶体管t61、t62的导通或截止的判断机制,与图1实施例中所 陈述的内容相类似,在此恕不多赘述。

74.预充电电路611则由晶体管t3所建构。在本实施例中,晶体管t3依 据启动信号st,在搜寻动作的初始时间区间中,被导通以拉升匹配线ml 上的匹配信号为预充电压vm。在完成匹配信号的预充电动作后,晶体管 t3可以被截止。

75.在图6b中,与图6a不相同的,晶体管t64以及t62可沿与匹配线 ml正交的方向依序

排列。晶体管t63以及t61同样可沿与匹配线ml正 交的方向依序排列。依据图6a、6b的绘示可以得知,三态内容可寻址存 储单元600可以依据二维或三维的方式进行布局。

76.请参照图7,图7为本发明一实施例的三态内容可寻址存储器的示意 图。三态内容可寻址存储器700包括存储单元阵列710、预充电电路 721~72n、感测放大器730、缓冲器740、源极线驱动器750以及编码器760。 存储单元阵列710包括多个三态内容可寻址的存储单元mc11~mcnm。存 储单元mc11~mcnm可区分为n个存储单元行以及m个存储单元列。存 储单元mc11~mcnm可依据图1、4、6的实施例中的三态内容可寻址存 储单元100、400或600来建构。

77.三态内容可寻址存储器700中并具有多条源极线sl1~sln,分别耦接 至存储单元阵列710中的n个存储单元行。存储单元阵列710中的m个存 储单元列分别通过多条选择线以接收选择信号sel1~selm,分别通过多 条选择线以接收反向选择信号sel1b~selmb。存储单元阵列710中的n 个存储单元行分别耦接多条匹配线ml1~mln,并通过匹配线ml1~mln 耦接至预充电电路721~72m以及感测放大器730。感测放大器730耦接至 编码器760。编码器760用以针对感测放大器730所产生的感测结果进行 编码,并产生一匹配结果。

78.源极线驱动器750耦接源极线sl1~sln。源极线驱动器750用以产生 多个源极驱动信号。缓冲器740耦接存储单元阵列710中的多条选择线, 分别提供多个写入数据或多个选择信号sel1~selm以及反向选择信号 sel1b~selmb至存储单元阵列710中的m个存储单元列。

79.在执行搜寻动作的细节上,请参照图8。图8为本发明图7实施例的 三态内容可寻址存储器的搜寻动作的示意图。其中,在初始状态下,可针 对所有的存储单元mc11~mcnm执行擦除动作。接着,针对存储单元 mc11~mcnm执行编程动作,并例如将逻辑0、1、1的数据分别写入存储 单元mc11、mc12、mc1m;将逻辑1、0、0的数据分别写入存储单元 mc21、mc22、mc2m;以及将逻辑0、1、0的数据分别写入存储单元 mcn1、mcn2、mcnm。

80.在搜寻动作时,预充电电路721~72n可预先使匹配线ml1~mln为预 充电压。例如依据逻辑1、0、0的数据对存储单元阵列710进行搜寻。可 使选择信号sel1、sel2、selm分别为逻辑1、0、0,并使反向选择信 号sel1b、sel2b、selmb分别为逻辑0、1、1。其中,匹配线ml1上 的匹配信号会被产生导通路径的存储单元mc1m所拉低,并产生表示不符 合的匹配信号。匹配线ml2耦接的存储单元mc21、mc22、mc2m的晶 体管都维持截止,匹配线ml2上的匹配信号则可维持为表示为符合的匹 配信号(实质上等于预充电压)。匹配线mln会被产生导通路径的存储单 元mcn1、mcn2所拉低,并产生表示不符合的匹配信号。

81.特别值得一提的,当存储单元中储存的数据为不在乎时,搜寻动作依 然可以正常运作。例如,当存储单元mcn2中储存的数据变更为不在乎时, 在针对逻辑0、1、0的数据进行搜寻时,匹配线mln上的匹配信号则可 维持为表示为符合的匹配信号(实质上等于预充电压)。

82.以下请参照图9,图9为本发明图7实施例的三态内容可寻址存储器 的擦除动作的示意图。在本发明实施例中,存储单元阵列710中的全部存 储单元可通过f-n隧穿的方式,一并擦除为具有低阈值电压的状态。亦即 擦除后的存储单元等同于储存逻辑0的数据。另外,本发明实施例也可针 对特定的存储单元执行擦除动作。例如,存储单元mc11原先储存不在乎 的数据(两晶体管t11、t12均储存逻辑1),存储单元mc22原先储存逻 辑1的数据(两

晶体管t21、t22分别储存逻辑1、0)。通过带-带电空穴 (band-to-band hot hole,btbhh)入射的方式,可逐一的针对存储单元 mc11、存储单元mc22执行擦除动作。其中,通过提供例如为-3v~-10v 的反向选择信号sel1b,为0伏特的选择信号sel1以及例如为3v~10v 的源极信号sl1,可以将晶体管t11中的数据擦除为逻辑0。而通过提供 例如为-3v~-10v的选择信号sel1,为0伏特的反向选择信号sel1b以 及例如为3v~10v的源极信号sl1,可以将晶体管t12中的数据擦除为逻 辑0。针对存储单元mc22,则可提供例如为-3v~-10v的反向选择信号 sel2b,为0伏特的选择信号sel2以及例如为3v~10v的源极信号sl2, 可以将晶体管t21中的数据擦除为逻辑0。

83.依据上述的说明可以得知,本发明实施例中,存储单元阵列710的架 构,可以提供使其中的多个存储单元中的晶体管,逐一的执行擦除的动作, 有效提升三态内容可寻址记忆的存取性能。

84.综上所述,本发明通过具有电荷储存结构的二晶体管来形成三态内容 可寻址存储单元。有效降低匹配线上所可能产生的漏电,稳定指示为符合 的匹配信号。本发明并可加速指示为不符合的匹配信号的拉低速度。如此 一来,三态内容可寻址存储单元的判断出的匹配结果的稳定性可以提升。

85.以上所述的具体实施例,对本发明的目的、技术方案和有益效果进行 了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施例而 已,并不用于限制本发明,凡在本发明的精神和原则之内,所做的任何修 改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1