存储器系统以及信息处理系统的制作方法

存储器系统以及信息处理系统

1.相关申请

2.本技术享受以日本专利申请2020-151960号(申请日:2020年9月10日)为基础申请的优先权。本技术通过参考该基础申请而包括基础申请的全部内容。

技术领域

3.本发明的实施方式涉及存储器系统以及信息处理系统。

背景技术:

4.已知有包括存储器系统和对存储器系统进行控制的主机设备的信息处理系统。存储器系统包括作为半导体存储装置的nand型闪存器和对半导体存储装置进行控制的存储器控制器。

技术实现要素:

5.实施方式提供能够提高巡检处理的控制性的存储器系统以及信息处理系统。

6.实施方式的存储器系统具备:非易失性存储器;以及存储器控制器,构成为根据第1指令集来执行巡检处理。所述存储器控制器构成为,在所述巡检处理中,从所述非易失性存储器读出第1数据,不将所述第1数据输出至所述存储器系统的外部。

附图说明

7.图1是用于说明第1实施方式的包括存储器系统的信息处理系统的结构的框图。

8.图2是用于说明第1实施方式的非易失性存储器的结构的框图。

9.图3是用于说明第1实施方式的非易失性存储器的存储单元阵列的结构的电路图。

10.图4是用于说明第1实施方式的存储单元阵列的阈值电压分布的示意图。

11.图5是用于说明第1实施方式的信息处理系统的巡检管理信息的概念图。

12.图6是用于说明第1实施方式的信息处理系统的巡检管理信息的详细的概念图。

13.图7是用于说明第1实施方式的信息处理系统的巡检管理信息的详细的概念图。

14.图8是用于说明第1实施方式的信息处理系统的巡检结果信息的概念图。

15.图9是用于说明第1实施方式的信息处理系统的巡检进度信息的概念图。

16.图10是用于说明第1实施方式的信息处理系统中的巡检管理动作的流程图。

17.图11是用于说明第1实施方式的信息处理系统中的巡检模式的第1例的登记动作的指令序列。

18.图12是用于说明在第1实施方式的信息处理系统中登记的巡检模式的第1例的示意图。

19.图13是用于说明第1实施方式的信息处理系统中的巡检模式的第2例的登记动作的指令序列。

20.图14是用于说明在第1实施方式的信息处理系统中登记的巡检模式的第2例的示

意图。

21.图15是用于说明第1实施方式的信息处理系统中的巡检模式的第3例的登记动作的指令序列。

22.图16是用于说明在第1实施方式的信息处理系统中登记的巡检模式的第3例的示意图。

23.图17是用于说明第1实施方式的信息处理系统中的巡检模式设定动作的指令序列。

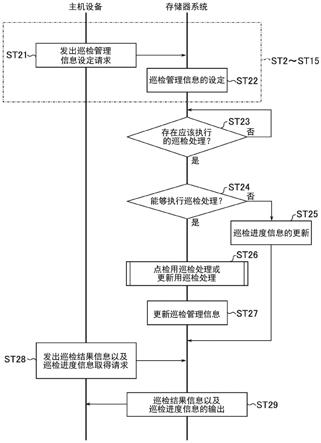

24.图18是用于说明第1实施方式的信息处理系统中的包括巡检处理在内的一系列动作的流程图。

25.图19是用于说明第1实施方式的信息处理系统中的点检用巡检处理的流程图。

26.图20是用于说明第1实施方式的信息处理系统中的更新用巡检处理的流程图。

27.图21是用于说明第1实施方式的信息处理系统中的更新用巡检处理的示意图。

28.图22是用于说明第1实施方式的信息处理系统中的更新用巡检处理与点检用巡检处理的关系的示意图。

29.图23是用于说明第1实施方式的变形例的信息处理的系统巡检管理信息的概念图。

30.图24是用于说明第1实施方式的变形例的信息处理系统中的巡回动作的流程图。

31.图25是用于说明第2实施方式的信息处理系统中的包括巡检处理在内的一系列动作的流程图。

32.图26是用于说明第2实施方式的信息处理系统中的巡检执行动作的指令序列。

33.图27是用于说明第3实施方式的信息处理系统的巡检管理信息的概念图。

34.图28是用于说明第3实施方式的信息处理系统中的巡检模式更新动作的流程图。

35.图29是用于说明第3实施方式的信息处理系统中的巡检模式更新动作的示意图。

36.图30是用于说明第3实施方式的变形例的信息处理系统中的巡检模式输出动作的流程图。

37.图31是用于说明其他变形例的信息处理系统中的更新用巡检处理的流程图。

38.图32是用于说明其他变形例的信息处理系统中的更新用巡检处理的示意图。

具体实施方式

39.以下,参照附图对实施方式进行说明。另外,在以下的说明中,对于具有相同的功能以及结构的构成要素,标注共通的参照附图标记。另外,在区分具有共通的参照附图标记的多个构成要素的情况下,对该共通的参照附图标记标注后缀来进行区别。另外,在对多个构成要素不需要特别区分的情况下,对该多个构成要素仅赋予共通的参照附图标记,不附加后缀。

40.1.第1实施方式

41.对第1实施方式的信息处理系统进行说明。

42.1.1结构

43.1.1.1信息处理系统

44.使用图1对第1实施方式的信息处理系统的结构进行说明。

45.如图1所示,信息处理系统1具备主机设备2及存储器系统3。

46.主机设备2例如是数据中心内的服务器或个人计算机等,存储查找表5。查找表5是将唯一地识别存储在存储器系统3内的数据的地址信息(逻辑地址)与唯一地识别该数据被存储的存储器系统3内的存储区域的地址信息(物理地址)相互建立关联而得到的信息。主机设备2构成为,能够基于该查找表5来指示向存储器系统3内的哪个物理地址写入数据(或者从哪个物理地址读出数据)。

47.存储器系统3例如是soc(system-on-a-chip),响应来自主机设备2的命令,命令对于存储器系统3内的非易失性存储器10指令执行读出处理、写入处理及擦除处理等。

48.1.1.2存储器系统

49.接着,参照图1,对第1实施方式的存储器系统的结构进行说明。

50.存储器系统3包括非易失性存储器10、易失性存储器20及存储器控制器30,并与主机设备2连接。非易失性存储器10、易失性存储器20以及存储器控制器30例如也可以通过它们的组合来构成一个半导体装置,作为其例子,可以举出sd

tm

卡那样的存储卡、ufs(universal flash storage:通用闪存器)、ssd(solid state drive:固态硬盘)等。

51.非易失性存储器10(以下,为nand闪存器10)例如包括分别包括多个存储单元晶体管的多个芯片10-0~10-n,非易失性地存储从主机设备2指示写入的数据(n为1以上的整数)。芯片10-0至10-n既可以具有互不相同的器件id,也可以具有相同的器件id。器件id例如是确定芯片的制造商、型号、批次数等的信息。另外,以下为了方便,有时也将芯片10-0~10-n分别记载为chip0~chipn。

52.易失性存储器20(以下,为dram20)例如是dram(dynamic random access memory:动态随机存取存储器),存储用于管理nand闪存器10的固件、各种管理信息。例如,dram20存储巡检管理信息21、巡检结果信息22以及巡检进度信息23,作为用于控制巡检处理的信息。

53.巡检处理为了以较少的错误比特数读出在nand闪存器10中存储的数据而包括定期或者不定期地执行的读出处理,例如包括点检用巡检处理以及更新用巡检处理。通过巡检处理内的读出处理而从nand闪存器10被读出的数据,不被输出至主机设备2。即,巡检处理在不将从nand闪存器10读出的数据输出至主机设备2这一点上与读出向主机设备2输出的数据的主机读出处理不同。

54.点检用巡检处理具有对是否能够订正从巡检对象读出的数据中包括的错误进行点检的功能。更新用巡检处理具有为了减少从巡检对象读出的数据中包括的错误而将在读出数据时使用的读出电压予以更新的功能。关于巡检处理的详细,在后面叙述。

55.巡检管理信息21包括对nand闪存器10执行的巡检处理的执行范围(物理地址)、类别、频率、优先级等的用于对计划(schedule)进行管理的信息。巡检结果信息22包括巡检处理的结果,例如,包括对在巡检对象的物理地址中存储的数据是否以较少的错误比特数读出、另外在错误比特数多的情况下是否应该刷新该数据进行表示的信息。巡检进度信息23包括表示巡检处理的进度状况的信息,例如包括对巡检处理是否按照存储于巡检管理信息21内的计划而执行进行表示的信息。

56.存储器控制器30包括处理器(cpu)31、缓冲存储器32、主机接口电路33、ecc电路34、nand接口电路35以及dram接口电路36。另外,以下说明的存储器控制器30的各部31~36的功能能够通过硬件结构、或者硬件资源与固件的组合结构中的任意一个来实现。

57.处理器31通过加载存储在rom(read only memory:只读存储器)中的程序来控制存储器控制器30整体的动作。例如,处理器31在从主机设备2接收到读出请求时,响应于此,执行读出处理。写入处理及擦除处理时也是同样的。另外,处理器31在从主机设备2接收到巡检管理信息设定请求时,响应于此,生成巡检处理的计划,并设定为巡检管理信息21。即,处理器31基于与来自主机设备2的请求相应的计划来执行巡检处理。

58.缓冲存储器32例如是sram(static random access memory:静态随机存取存储器),暂时存储存储器控制器30从nand闪存器10读出的数据、从主机设备2接收到的写入数据等。

59.主机接口电路33经由主机总线与主机设备2连接,负责存储器控制器30与主机设备2之间的通信。主机总线例如是遵照sd

tm

接口、sas(serial attached scsi(small computer system interface))、sata(serial ata(advanced technology attachment))或pcie(peripheral component interconnect express)等的总线。

60.ecc电路34进行与存储于nand闪存器10的数据有关的错误检测及错误订正处理。即,ecc电路34在数据的写入时生成错误订正码,并将其赋予写入数据,在数据的读出处理时对其进行解码,检测错误比特的有无。而且,在检测出错误比特时,确定该错误比特的位置,并订正错误。错误订正的方法例如包括硬判定解码(hard bit decoding)以及软判定解码(soft bit decoding)。作为用于硬判定解码的硬判定解码码,例如能够使用bch(bose-chaudhuri-hocquenghem)码、rs(reed-solomon)码等,作为用于软判定解码的软判定解码码,例如能够使用ldpc(low density parity check:低密度奇偶校验)码等。

61.nand接口电路35通过nand总线与nand闪存器10连接,负责与nand闪存器10的通信。nand接口电路35对存储器控制器30与nand闪存器10之间的数据、指令及物理地址的转送进行控制,独立地控制nand闪存器10内的各芯片10-0~10-n。nand接口电路35支持nand接口标准。

62.dram接口电路36与dram20连接,负责存储器控制器30与dram20之间的通信。dram接口电路36支持dram接口标准。

63.1.1.3芯片

64.接着,使用图2对nand闪存器10内的芯片的结构进行说明。在图2中,作为一例而示出芯片10-0内的结构。另外,芯片10-0以外的芯片10-1~10-n具有与芯片10-0同等的结构,因此省略说明。

65.如图2所示,芯片10-0例如包括输入输出电路11、寄存器组12、逻辑控制器13、序列发生器14、就绪/忙碌控制电路15、电压生成电路16、存储单元阵列17、行解码器模块18及读出放大器模块19。

66.输入输出电路11例如在其与存储器控制器30之间收发8比特宽的输入输出信号i/o1~i/o8。输入输出信号i/o能够包括数据dat、状态信息sts、物理地址add、指令cmd等。另外,输入输出电路11在其与读出放大器模块19之间收发数据dat。

67.寄存器组12包括状态寄存器12a、地址寄存器12b和指令寄存器12c。状态寄存器12a、地址寄存器12b以及指令寄存器12c分别存储状态sts、物理地址add、以及指令cmd。

68.状态sts例如基于序列发生器14的动作状态而被更新。另外,状态sts基于来自存储器控制器30的指示从状态寄存器12a被转送至输入输出电路11,并被输出至存储器控制

器30。物理地址add从输入输出电路11被转送至地址寄存器12b,例如可包括芯片地址、块地址、页地址、列地址等。指令cmd从输入输出电路11被转送至指令寄存器12c,包括与芯片10-0的各种动作有关的指令。

69.逻辑控制器13基于从存储器控制器30接收到的控制信号,分别控制输入输出电路11及序列发生器14。作为这样的控制信号,例如使用芯片使能信号cen、指令锁存使能信号cle、地址锁存使能信号ale、写入使能信号wen、读取使能信号ren、以及写入保护信号wpn。

70.芯片使能信号cen是用于使芯片10-0成为能的信号。指令锁存使能信号cle是用于将接收到的输入输出信号i/o为指令cmd这一情况通知至输入输出电路11的信号。地址锁存使能信号ale是用于将接收到的输入输出信号i/o是地址信息add这一情况通知至输入输出电路11的信号。写使能信号wen是用于命令输入输出电路11进行输入输出信号i/o的输入的信号。读取使能信号ren是用于命令输入输出电路11进行输入输出信号i/o的输出的信号。写入保护信号wpn是用于在电源的接通断开时使芯片10-0成为保护状态的信号。

71.序列发生器14控制芯片10-0整体的动作。例如,序列发生器14基于存储于指令寄存器12c的指令cmd和存储于地址寄存器12b的物理地址add,执行读出处理、写入处理、擦除处理等。

72.就绪/忙碌控制电路15基于序列发生器14的动作状态,生成就绪/忙碌信号rbn。就绪/忙碌信号rbn是用于向存储器控制器30通知芯片10-0是就绪状态还是忙碌状态的信号。另外,在本说明书中,“就绪状态”表示芯片10-0是受理来自存储器控制器的指令的状态,“忙碌状态”表示芯片10-0是不受理来自存储器控制器的指令的状态。

73.电压生成电路16生成在读出处理、写入处理、擦除处理等中使用的电压。然后,电压生成电路16将所生成的电压供给至存储单元阵列17、行解码器模块18及读出放大器模块19。

74.存储单元阵列17包括多个块blk0~blkn(n为1以上的整数)。块blk是能够非易失性地存储数据的多个存储单元晶体管的集合,例如被用作数据的擦除单位。各存储单元晶体管与1条位线bl和1条字线wl建立关联。

75.行解码器模块18基于块地址来选择执行各种处理的块blk。然后,行解码器模块18将从电压生成电路16供给的电压转送至所选择的块blk内的字线wl等。

76.读出放大器模块19在读出处理中,从存储单元阵列17读出数据,将该读出数据转送至输入输出电路11。另外,读出放大器模块19在写入处理中,基于从输入输出电路11接收到的数据,对位线bl施加规定的电压。

77.1.1.4存储单元阵列

78.图3是第1实施方式的非易失性存储器内的芯片所包括的存储单元阵列的电路结构的一例,提取1个块blk来进行表示。如图3所示,块blk包括例如4个串单元su0~su3。

79.各串单元su包括分别与位线bl0~blm建立关联的多个nand串ns(m为1以上的整数)。nand串ns例如包括存储单元晶体管mt0~mt7、以及选择晶体管st1及st2。

80.存储单元晶体管mt包括控制栅极及电荷蓄积层,非易失性地存储数据。选择晶体管st1及st2分别用于各种处理时的串单元su的选择。

81.在各nand串ns中,存储单元晶体管mt0~mt7被串联连接。在被串联连接的存储单元晶体管mt0~mt7的一端与建立关联的位线bl之间连接有选择晶体管st1。在串联连接的

状态下的阈值电压为电压vs2以上且小于电压vs3。“s3”状态下的阈值电压为电压vs3以上且小于电压vs4。“s4”状态下的阈值电压为电压vs4以上且小于电压vs5。“s5”状态下的阈值电压为电压vs5以上且小于电压vs6。“s6”状态下的阈值电压为电压vs6以上且小于电压vs7。“s7”状态下的阈值电压为电压vs7以上且小于电压vs8。“s8”状态下的阈值电压为电压vs8以上且小于电压vs9。“s9”状态下的阈值电压为电压vs9以上且小于电压vs10。“s10”状态下的阈值电压为电压vs10以上且小于电压vs11。“s11”状态下的阈值电压为电压vs11以上且小于电压vs12。“s12”状态下的阈值电压为电压vs12以上且小于电压vs13。“s13”状态下的阈值电压为电压vs13以上且小于vs14。“s14”状态下的阈值电压为电压vs14以上且小于vs15。“s15”状态下的阈值电压为电压vs15以上且小于电压vread。

93.上述的16个阈值电压分布通过写入包括低位比特、中位比特、高位比特以及头部比特这4比特(4页)数据而形成。并且,16个阈值电压分布分别对应于不同的4比特的数据。在本实施方式中,对各状态所包括的存储单元晶体管mt,如以下所示地对“头部比特/高位比特/中位比特/低位比特”分配数据。

[0094]“s0”状态所包括的存储单元晶体管mt存储“1111”数据。“s1”状态所包括的存储单元晶体管mt存储“1110”数据。“s2”状态所包括的存储单元晶体管mt存储“1010”数据。“s3”状态所包括的存储单元晶体管mt存储“1000”数据。“s4”状态所包括的存储单元晶体管mt存储“1001”数据。“s5”状态所包括的存储单元晶体管mt存储“0001”数据。“s6”状态所包括的存储单元晶体管mt存储“0000”数据。“s7”状态所包括的存储单元晶体管mt存储“0010”数据。“s8”状态所包括的存储单元晶体管mt存储“0110”数据。“s9”状态所包括的存储单元晶体管mt存储“0100”数据。“s10”状态所包括的存储单元晶体管mt存储“1100”数据。“s11”状态所包括的存储单元晶体管mt存储“1101”数据。“s12”状态所包括的存储单元晶体管mt存储“0101”数据。“s13”状态所包括的存储单元晶体管mt存储“0111”数据。“s14”状态所包括的存储单元晶体管mt存储“0011”数据。“s15”状态所包括的存储单元晶体管mt存储“1011”数据。

[0095]

低位页读出将区分“s0”状态和“s1”状态的电压vs1、区分“s3”状态和“s4”状态的电压vs4、区分“s5”状态和“s6”状态的电压vs6、以及区分“s10”状态和“s11”状态的电压vs11用作读出电压。将使用电压vs1、vs4、vs6及vs11的读出处理分别称为读出处理1r、4r、6r及11r。

[0096]

中位页读出将区分“s2”状态和“s3”状态的电压vs3、区分“s6”状态和“s7”状态的电压vs7、区分“s8”状态和“s9”状态的电压vs9以及区分“s12”状态和“s13”状态的电压vs13用作读出电压。将使用电压vs3、vs7、vs9及vs13的读出处理分别称为读出处理3r、7r、9r及13r。

[0097]

高位页读出将区分“s1”状态和“s2”状态的电压vs2、区分“s7”状态和“s8”状态的电压vs8、以及区分“s13”状态和“s14”状态的电压vs14用作读出电压。将使用电压vs2、vs8及vs14的读出处理分别称为读出处理2r、8r及14r。

[0098]

头部页读出将区分“s4”状态和“s5”状态的电压vs5、区分“s9”状态和“s10”状态的电压vs10、区分“s11”状态和“s12”状态的电压vs12以及区分“s14”状态和“s15”状态的电压vs15用作读出电压。将使用电压vs5、vs10、vs12及vs15的读出处理分别称为读出处理5r、10r、12r及15r。

[0099]

另外,上述的数据分配是一个例子,也可以应用其他的数据分配。

[0100]

1.1.6巡检管理信息

[0101]

接着,对第1实施方式的巡检管理信息的结构进行说明。图5是用于说明第1实施方式的巡检管理信息的结构的一例的概念图。图6以及图7是用于说明第1实施方式的巡检管理信息的详细的概念图。在图6中,示出巡检管理信息中包括的物理地址的一例。在图7的(a)、图7的(b)、图7的(c)以及图7的(d)中,分别示出巡检管理信息中包括的优先级、类别、周期以及管理标志的一例。

[0102]

以下,沿着图5对巡检管理信息21的概念进行说明,并且适当参照图6或图7对各种要素的详细的信息进行说明。

[0103]

如图5所示,巡检管理信息21可以具有与互不相同的优先级建立对应的多个队列。在图5的例子中,在与某优先级对应的队列中,与该某优先级对应的多个巡检指定单元pu按照执行顺序排列。具体而言,多个巡检指定单元pu00、pu01、pu02、

…

、pu0x的组、pu10、pu11、pu12、

…

、pu1x的组、以及pu20、pu21、pu22,

…

pu2x的组分别由与3个互不相同的优先级建立对应的队列来管理。

[0104]

多个巡检单元pu分别是巡检处理的执行单位,例如包括<物理地址>、<优先级>、<类别>、<周期>、以及<管理标志>的信息。

[0105]

首先,参照图6对巡检单元pu内的物理地址add进行说明。物理地址add指定成为与该巡检单元pu对应的巡检处理的对象的nand闪存器10内的存储区域。

[0106]

如图6所示,物理地址add指定巡检对象的物理地址的范围和在该范围内成为巡检对象的要素。更具体而言,物理地址add指定nand闪存器10内的芯片chip、块blk、字线wl、串单元su及页p作为范围。例如指定了全部芯片chip内的全部块blk中的、与全部字线wl及全部串单元su对应的存储单元晶体管mt的全部页p的情况下的物理地址add成为<allchip-allblk-allwl-allsu-allp>。另外,例如,指定了芯片chipxc内的块blkxb中的、与字线wlxw及串单元suxs对应的存储单元晶体管mt的页pxp的情况下的物理地址add成为<chipxc-blkxb-wlxw-suxs-pxp>(xc是0以上且n以下的整数,xb是0以上且n以下的整数,xw是0以上且7以下的整数,xs是0以上且3以下的整数,xp是0以上且3以下的整数)。另外,在图6中,xp在为“0”的情况下表示为低位页,在为“1”的情况下表示为中位页,在为“2”的情况下表示为高位页,在为“3”的情况下表示为首页的情况作为一例来表示。

[0107]

接着,参照图7的(a)对巡检指定单元pu内的优先级pr进行说明。优先级pr指定相对于在存储器控制器30内执行的预定的巡检处理以外的处理而言的巡检处理的优先顺序。

[0108]

如图7的(a)所示,在优先级pr为<pr0>的情况下,表示最优先地执行与该巡检指定单元pu对应的巡检处理。在优先级pr为<pr1>的情况下,表示将对应的巡检处理的优先顺序设定得高、为紧接着主机读出处理之后,而该巡检处理紧接着主机读出处理之后优先执行。在优先级pr为<pr2>的情况下,表示将对应的巡检处理的优先顺序设定为相对于其他全部的处理而言较低、而该巡检处理最后执行。在优先级pr为<pr3>的情况下,表示在对来自主机设备2的请求(主机指令)进行了规定数的处理之后执行对应的巡检处理。

[0109]

接着,参照图7的(b)对巡检指定单元pu内的类别w进行说明。类别w指定与该巡检指定单元pu对应的巡检处理的类别。

[0110]

如图7的(b)所示,在类别w为<wcheck>的情况下,表示在与该巡检指定单元pu对

应的巡检处理中应用点检用巡检处理。在类别w为<wupdate>的情况下,表示在该巡检处理中应用更新用巡检处理。

[0111]

接着,参照图7的(c)对巡检指定单元pu内的周期pe进行说明。周期pe表示与该巡检指定单元pu对应的巡检处理被设定于巡检管理信息21的频率。

[0112]

如图7的(c)所示,在周期pe为<pe12h>、<pe1d>、<pe2d>、<pe4d>及<pe8d>的情况下,表示与该巡检指定单元pu对应的巡检处理分别按每12小时、每1天、每2天、每4天、及每8天执行。这样,被设定了周期pe的巡检指定单元pu,在对应的巡检处理被执行之后,在从执行了该巡检指定单元pu的时刻起在时序上周期pe之后的位置,作为新的巡检指定单元pu被重新设定。

[0113]

另外,虽然在图7的(c)中省略了图示,但在周期pe被设定了《pe2d》、《pe4d》以及《pe8d》的情况下,也可以包括进一步指定对应的巡检处理在该周期pe的第几天执行的信息。具体而言,例如,在周期pe分别为《pe4d-1》、《pe4d-2》、《pe4d-3》以及《pe4d-0》的情况下,对应的巡检处理能够分别设定为在4天周期的第1天、第2天、第3天以及第4天执行。

[0114]

接着,参照图7的(d)对巡检指定单元pu内的管理标志f进行说明。管理标志f表示对与该巡检指定单元pu对应的巡检处理特别赋予的标志。

[0115]

如图7的(d)所示,在管理标志f为<freset>的情况下,表示对与该巡检指定单元pu对应的巡检处理赋予的标志为复位状态(未赋予标志)。另外,在管理标志f为<fpatrol>的情况下,表示强制地执行与该巡检指定单元pu对应的巡检处理。

[0116]

通过以上那样的巡检管理信息21,存储器控制器30能够管理对nand闪存器10执行的巡检处理的计划。

[0117]

另外,在图5的例子中,示出了多个巡检指定单元pu按每个优先级由不同的队列来管理的情况,但不限于此。例如,多个巡检指定单元pu可以由1个队列集中管理。

[0118]

1.1.7巡检结果信息

[0119]

接着,对第1实施方式的巡检结果信息的结构进行说明。图8是用于说明第1实施方式的巡检结果信息的结构的一例的概念图。

[0120]

如图8所示,巡检结果信息22针对nand闪存器10内的全部芯片10-0~10-n的每一个,存储表示应该对哪个块blk实施刷新处理的刷新标志。刷新处理是通过将写入到nand闪存器10内的数据改写到新的物理地址、或者盖写到写入有将该数据的物理地址,从而减少数据中包括的错误比特数的处理。

[0121]

在图8的例子中,存储有芯片10-0的块blk0的刷新标志为“真(true)”、应该执行刷新处理的意思。另外,存储有芯片10-0的块blk0以外的全部块blk的刷新标记为“假”、也可以不执行刷新处理的意思。

[0122]

例如,在巡检处理的结果判明了从巡检对象读出的数据中包括的错误比特数多于阈值的情况下,在巡检结果信息22内的与包括该巡检对象的块blk对应的刷新标志中存储“真”。因此,存储器控制器30通过参照巡检结果信息22,能够掌握是否需要刷新处理。

[0123]

1.1.8巡检进度信息

[0124]

接着,对第1实施方式的巡检进度信息的结构进行说明。图9是用于说明第1实施方式的巡检进度信息的结构的一例的概念图。

[0125]

如图9所示,巡检进度信息23例如是在按照巡检管理信息21推进巡检处理时,根据

主机指令等与其他处理的优先级,存储了无法处理的巡检指定单元pu的信息。如上所述,在巡检指定单元pu中,根据状况来设定不同的优先级pr。因此,在优先级pr未被设定为最优先(<pr0>)的情况下,该巡检指定单元pu的执行有时由于主机读出处理等其他处理而被妨碍。存储器控制器30通过参照巡检进度信息23,能够掌握这样的巡检处理的进展的延迟。

[0126]

此外,如上所述,巡检进度信息23也可以不仅存储无法处理的巡检指定单元pu,还可以针对每个队列存储无法处理的巡检指定单元pu的数量。由此,存储器控制器30能够容易地掌握在每个队列中巡检处理延迟了何种程度。

[0127]

1.2动作

[0128]

接着,对第1实施方式的信息处理系统中的动作进行说明。

[0129]

1.2.1巡检管理信息设定动作的流程图

[0130]

首先,对第1实施方式的信息处理系统中的巡检管理信息设定动作进行说明。

[0131]

图10是表示第1实施方式的信息处理系统中的巡检管理信息设定动作的流程图。在图10中,示出了基于来自主机设备2的请求的巡检管理信息21的设定动作的几个方式。

[0132]

另外,图10的步骤st3、st5、st7、st9、st11、st13以及st15中的存储器系统3的处理意味着分别按照来自步骤st2、st4、st6、st8、st10、st12、以及st14中的主机设备2的请求来执行,并不意味着依次执行步骤st2、st4、st6、st8、st10、st12、以及st14中的来自主机设备2的请求。

[0133]

如图10所示,在步骤st1中,存储器系统3被启动。当存储器系统3启动时,处理器31加载存储在rom中的程序(上电读出处理),开始存储器控制器30的控制。另外,在刚刚进行上电读出处理之后,dram20内也可以未存储有巡检管理信息21。因此,存储器控制器30也可以不具有用于在刚刚进行上电读出处理之后执行巡检处理的计划。

[0134]

在步骤st2中,主机设备2发出巡检模式登记请求“setpatcom”,并发送至存储器系统3。巡检模式被定义为对某个物理地址的范围(例如1块blk的范围)设定的多个巡检处理的定型。巡检模式登记请求“setpatcom”是用于将由主机设备2预先定义的巡检模式通知至存储器系统3的指令。

[0135]

在步骤st3中,当接收到巡检模式登记请求时,存储器控制器30登记巡检模式。通过使用该巡检模式,存储器控制器30能够以更少的指令数高效地将多个巡检指定单元pu设定至巡检管理信息21。

[0136]

在步骤st4中,主机设备2发出针对nand闪存器10内的已写入有数据的存储区域(已写入区域)的巡检管理信息设定请求“patrolset”,并发送至存储器控制器30。巡检管理信息设定请求“patrolset”是向存储器控制器30指示在巡检管理信息21中设定1个或多个巡检指定单元pu的动作的指令。步骤st4中的巡检管理信息设定请求“patrolset”中包括指定已写入区域的物理地址add。

[0137]

在步骤st5中,存储器控制器30在接收到巡检管理信息设定请求时,将对已写入区域执行的巡检处理设定至巡检管理信息21。由此,巡检管理信息21被初始化,存储器控制器30能够执行沿着计划的巡检处理。

[0138]

在步骤st6中,主机设备2发出写入请求“write”,并发送至存储器控制器30。写入请求“write”包括向nand闪存器10写入的数据和写入该数据的nand闪存器10内的物理地址(写入对象区域)add。

[0139]

在步骤st7中,存储器控制器30基于写入请求将数据写入到nand闪存器10。

[0140]

在步骤st8中,主机设备2发出针对写入对象区域的巡检管理信息设定请求“patrolset”,并发送至存储器控制器30。步骤st8中的巡检管理信息设定请求“patrolset”中包括对与写入对象区域相同的存储区域进行指定的物理地址add。

[0141]

在步骤st9中,存储器控制器30在接收到巡检管理信息设定请求时,将对写入对象区域执行的巡检处理设定至巡检管理信息21。由此,与通过步骤st7的写入处理新写入的数据对应的巡检处理被追加到巡检管理信息21。这样,存储器控制器30能够根据伴随写入请求而发送的巡检管理信息设定请求,对于存储器系统3启动后新成为已写入区域的存储区域也设定巡检处理的计划。

[0142]

在步骤st10中,主机设备2发出针对已写入区域的新的巡检管理信息设定请求“patrolset”,并发送至存储器控制器30。

[0143]

在步骤st11中,存储器控制器30在接收到该新的巡检管理信息设定请求时,将对已写入区域执行的巡检处理设定至巡检管理信息21。由此,巡检管理信息21通过该新的巡检管理信息设定请求而被更新。这样,存储器控制器30能够通过最新的巡检管理信息设定请求来将执行的巡检处理的计划更新。

[0144]

在步骤st12中,主机设备2发出擦除或无效化请求,并发送至存储器控制器30。擦除或无效化请求包括存储有成为擦除或无效化的对象的数据的nand闪存器10内的物理地址(擦除或无效化对象区域)add。

[0145]

在步骤st13中,存储器控制器30基于擦除或无效化请求,将nd闪存器10的数据擦除或无效化。

[0146]

在步骤st14中,主机设备2发出针对擦除或无效化对象区域的巡检管理信息删除请求“patrolunset”,并发送至存储器控制器30。巡检管理信息删除请求“patrolunset”是向存储器控制器30指示从巡检管理信息21中删除1个或多个巡检指定单元pu的动作的指令。在巡检管理信息删除请求“patrolunset”中包括对擦除或无效化对象区域进行指定的物理地址add。

[0147]

在步骤st15中,存储器控制器30在接收到巡检管理信息删除请求时,从巡检管理信息21中删除针对擦除或无效化对象区域的巡检处理的计划。这样,存储器控制器30能够通过巡检管理信息删除请求,适当地删除不必要的巡检处理的计划,仅选择性地执行必要的巡检处理。

[0148]

通过以上,巡检管理信息设定动作结束。另外,与图10所示的步骤st6~st15中示出的写入处理相伴的巡检管理信息21的追加、巡检管理信息21的变更、以及与擦除或者无效化处理相伴的巡检管理信息21的删除的处理,不限于存储器系统3的系统启动时的紧后,而在系统动作中的任意的定时以不同的顺序执行。由此,能够遍及存储器系统3启动着的期间地、将巡检管理信息21保持为最新的信息。

[0149]

1.2.2巡检模式登记动作

[0150]

接着,对第1实施方式的信息处理系统中的巡检模式登记动作的几个例子进行说明。如以下所示,存储器控制器30能够基于来自主机设备2的指令来指定物理地址add、优先级pr、类别w、周期pe以及管理标志f,由此设定巡检处理的计划。

[0151]

1.2.2.1第1例(巡检模式a)

p0><pr1><pe4d-0><wcheck>”、“patrolset<allwl-su2-p1><pr1><pe4d-0><wcheck>”、以及“patrolset<allwl-su3-p2><pr1><pe4d-0><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与全部字线wl有关的串单元su0的首页、串单元su1的低位页、串单元su2的中位页、以及串单元su3的高位页作为对象,识别出在巡检模式a中包括在4天周期的第4天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图11的第14行~第17行的指令与图12中的阴影图案(d)对应。

[0159]

通过以上,存储器控制器30能够登记如图12那样的巡检模式的第1例。

[0160]

1.2.2.2第2例(巡检模式b)

[0161]

接着,对巡检模式的第2例进行说明。在第2例中,设定为在一个块blk的量的范围内散布有周期相等且执行日互不相同的4种点检用巡检处理、和以高于该点检用巡检处理的频率设定的更新用巡检处理。

[0162]

图13是表示第1实施方式的信息处理系统中的巡检模式的第2例的登记动作的指令序列。图14是表示在第1实施方式的信息处理系统中登记的巡检模式的第2例的示意图。在图13中,示出了来自将巡检模式的第2例登记所用的主机设备2的指令集的具体例。图14将按照图13所示的指令序列设定的4种点检用巡检处理以及1种更新用巡检处理通过5个阴影模式(a’)~(d’)以及(e)在视觉上分类而进行表示。

[0163]

如图13的第1行中所示,主机设备2发出巡检模式登记指令“setpatcom patrolmode-b12”。存储器控制器30在接收到该指令时,识别为由后续的12个指令的组表现的一组巡检处理被定义为巡检模式b。

[0164]

接着,如图13的第2行以及第3行所示,主机设备2发出2个巡检管理信息设定指令“patrolset<allwl-su0-p0><pr1><pe4d-1><wcheck>”、以及“patrolset<allwl-su1-p1><pr1><pe4d-1><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与全部字线wl有关的串单元su0的低位页、以及串单元su1的中位页作为对象,识别出在巡检模式b中包括在4天周期的第1天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。

[0165]

接着,如图13的第4行~第6行所示,主机设备2发出3个巡检管理信息设定指令“patrolset<allwl-su0-p1><pr1><pe4d-2><wcheck>”、“patrolset<allwl-su2-p3><pr1><pe4d-2><wcheck>”、以及“patrolset<allwl-su3-p0><pr1><pe4d-2><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与全部字线wl有关的串单元su0的中位页、串单元su2的首页以及串单元su3的低位页作为对象,识别出在巡检模式b中包括在4天周期的第2天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。

[0166]

接着,如图13的第7行及第8行所示,主机设备2发出2个巡检管理信息设定指令“patrolset<allwl-su2-p0><pr1><pe4d-3><wcheck>”、及“patrolset<allwl-su3-p1><pr1><pe4d-3><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与全部字线wl有关的串单元su2的低位页、以及串单元su3的中位页作为对象,识别出在巡检模式b中包括在4天周期的第3天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。

su1-p2><pr1><pe8d-2><wcheck>”、“patrolset<evenwl-su2-p3><pr1><pe8d-2><wcheck>”、及“patrolset<evenwl-su3-p0><pr1><pe8d-2><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与偶数字线wl有关的串单元su0的中位页、串单元su1的高位页、串单元su2的首页以及串单元su3的低位页作为对象,识别出在巡检模式c中包括在8天周期的第2天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第4行和第5行的指令与图16中的阴影图案(b_e)对应。

[0177]

接着,如图15的第6行及第7行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<evenwl-su0-p2><pr1><pe8d-3><wcheck>”、“patrolset<evenwl-su1-p3><pr1><pe8d-3><wcheck>”、“patrolset<evenwl-su2-p0><pr1><pe8d-3><wcheck>”、及“patrolset<evenwl-su3-p1><pr1><pe8d-3><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与偶数字线wl有关的串单元su0的高位页、串单元su1的首页、串单元su2的低位页、以及串单元su3的中位页作为对象,识别出在巡检模式c中包括在8天周期的第3天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第6行和第7行的指令与图16中的阴影图案(c_e)对应。

[0178]

接着,如图15的第8行及第9行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<evenwl-su0-p3><pr1><pe8d-4><wcheck>”、“patrolset<evenwl-su1-p0><pr1><pe8d-4><wcheck>”、“patrolset<evenwl-su2-p1><pr1><pe8d-4><wcheck>”、及“patrolset<evenwl-su3-p2><pr1><pe8d-4><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与偶数字线wl有关的串单元su0的首页、串单元su1的低位页、串单元su2的中位页、以及串单元su3的高位页作为对象,识别出在巡检模式c中包括在8天周期的第4天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第8行和第9行的指令与图16中的阴影图案(d_e)对应。

[0179]

接着,如图15的第10行及第11行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<oddwl-su0-p0><pr1><pe8d-5><wcheck>”、“patrolset<oddwl-su1-p1><pr1><pe8d-5><wcheck>”、“patrolset<oddwl-su2-p2><pr1><pe8d-5><wcheck>”、及“patrolset<oddwl-su3-p3><pr1><pe8d-5><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与奇数字线wl有关的串单元su0的低位页、串单元su1的中位页、串单元su2的高位页、以及串单元su3的首页作为对象,识别出在巡检模式c中包括在8天周期的第5天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第10行和第11行的指令对应于图16中的阴影图案(a_o)。

[0180]

接着,如图15的第12行及第13行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<oddwl-su0-p1><pr1><pe8d-6><wcheck>”、“patrolset<oddwl-su1-p2><pr1><pe8d-6><wcheck>”、“patrolset<oddwl-su2-p3><pr1><pe8d-6><wcheck>”、以及“patrolset<oddwl-su3-p0><pr1><pe8d-6><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与奇数字线wl有关的串单元su0的中位页、串单元su1的高位页、串单元su2的首页以及串单元su3的低位页作为对象,识

别出在巡检模式c中包括在8天周期的第6天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第12行和第13行的指令对应于图16中的阴影图案(b_o)。

[0181]

接着,如图15的第14行及第15行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<oddwl-su0-p2><pr1><pe8d-7><wcheck>”、“patrolset<oddwl-su1-p3><pr1><pe8d-7><wcheck>”、“patrolset<oddwl-su2-p0><pr1><pe8d-7><wcheck>”、及“patrolset<oddwl-su3-p1><pr1><pe8d-7><wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与奇数字线wl有关的串单元su0的高位页、串单元su1的首页、串单元su2的低位页、以及串单元su3的中位页作为对象,识别出在巡检模式c中包括在8天周期的第7天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第14行及第15行的指令对应于图16中的阴影图案(c_o)。

[0182]

接着,如图15的第16行及第17行所示,主机设备2发出4个巡检管理信息设定指令“patrolset<oddwl-su0-p3><pr1><pe8d-0><wcheck>”、“patrolset<oddwl-su1-p0><pr1><pe8d-0><wcheck>”、“patrolset<oddwl-su2-p1><pr1><pe8d-0><wcheck>”、及“patrolset<oddwl-su3-p2><pr1><pe8d-0<wcheck>”。当接收到该指令时,存储器控制器30将巡检模式登记对象的块blk的与奇数字线wl有关的串单元su0的首页、串单元su1的低位页、串单元su2的中位页、以及串单元su3的高位页作为对象,识别出在巡检模式c中包括在8天周期的第8天执行且具有紧接着主机读出处理之后的高的优先级的点检用巡检处理。上述图15的第16行和第17行的指令对应于图16中的阴影图案(d_o)。

[0183]

因此,存储器控制器30可以登记如图16所示的巡检模式的第3例。

[0184]

1.2.3巡检管理信息设定动作的指令序列

[0185]

接着,使用图17所示的指令序列,对使用如上述那样登记的巡检模式a~c来设定巡检管理信息21的动作的例子进行说明。

[0186]

如图17的第1行所示,主机设备2发出2个巡检管理信息设定指令“patrolset<chip0-blk0><patrolmode-a”以及“patrolset<chip0-blkn><patrolmode-c>”。当接收到该指令时,存储器控制器30对芯片10-0的块blk0及blkn分别设定巡检管理信息21,以执行由巡检模式a及c规定的一组巡检处理。这样,基于来自主机设备2的指令,存储器控制器30针对不同的块blk,能够以执行频率不同的计划执行巡检处理。作为设定这样的计划的情况,设想例如块blkn被用作块blk0的复制区域,只要正确地读出块blk0的数据,对于块blkn也可以降低巡检处理的执行频率的情况等。

[0187]

接着,如图17的第2行所示,主机设备2发出写入请求“write<chip0-blk1>“及巡检管理信息设定指令“patrolset<chip0-blk1><patrolmode-a>”。当接收到该指令时,存储器控制器30将巡检管理信息21设定为,向芯片10-0的块blk1写入数据,并且以对该写入对象区域执行由巡检模式a规定的一组巡检处理。这样,通过使用预先登记的巡检模式,能够通过主机设备2与存储器系统3之间的2个指令来实现图10的步骤st6~st9所示的一系列的处理。

[0188]

接着,如图17的第3行所示,主机设备2发出巡检管理信息设定指令“patrolset<chip0-blk1><patrolmode-b>”。当接收到该指令时,存储器控制器30更新巡检管理信息21,以将对芯片10-0的块blk1设定的巡检模式从巡检模式a变更为巡检模式b。这样,通过使

用预先登记的巡检模式,能够通过主机设备2与存储器系统3之间的1个指令来实现图10的步骤st10以及st11所示的一系列的处理。

[0189]

接着,如图17的第4行所示,主机设备2发出擦除或无效化请求“erase<chip0-blk1>“、以及巡检管理信息删除指令“patrolunset<chip0-blk1><patrolmode-b>“。当接收到该指令时,存储器控制器30将巡检管理信息21设定为,将被写入到芯片10-0的块blk1的数据擦除或无效化,并且对该擦除或无效化对象区域删除由所设定的巡检模式b规定的一组巡检处理。这样,通过使用预先登记的巡检模式,能够通过主机设备2与存储器系统3之间的2个指令来实现图10的步骤st12~st15所示的一系列的处理。

[0190]

1.2.4包括巡检处理在内的一系列操作

[0191]

接着,对第1实施方式的信息处理系统中的包括巡检处理在内的一系列的动作进行说明。

[0192]

1.2.4.1流程图

[0193]

图18是表示第1实施方式的信息处理系统中的包括巡检处理在内的一系列动作的流程图。在图18中,示出了包括基于在图10等中说明的巡检管理信息设定动作而执行的巡检处理在内的一系列动作的流程。

[0194]

如图18所示,在步骤st21中,主机设备2发出巡检管理信息设定请求(指令集),并发送至存储器系统3。在步骤st22中,存储器系统3在接收到巡检管理信息设定请求时,设定巡检管理信息21。步骤st21及st22例如相当于图10中的步骤st2~st15。

[0195]

在步骤st23中,存储器控制器30参照巡检管理信息21,判定是否存在应该执行的巡检处理。在存在应该执行的巡检处理的情况下(步骤st23;是),处理进入到步骤st24,在不存在应该执行的巡检处理的情况下(步骤st23;否),处理返回到步骤st23。这样,直到在巡检管理信息21中设定的巡检指定单元pu应该执行的定时为止保留巡检处理的执行,在成为应该执行的定时时,处理进入到步骤st24。

[0196]

在步骤st24中,存储器控制器30判定是否能够执行判定为应该执行的巡检处理。在能够执行巡检处理的情况下(步骤st24;是),处理进入到步骤st26,在不能够执行巡检处理的情况下(步骤st24;否),处理进入到步骤st25。作为处理进入到步骤st25的情况的例子,例如,设想在应该执行巡检处理的定时,存储器控制器30从主机设备2接受到优先级比该巡检处理高的处理(例如,主机读出处理)等执行请求的情况等。

[0197]

在步骤st25中,存储器控制器30将与被判定为不能够执行的巡检处理对应的巡检指定单元pu的标识符存储在巡检进度信息23中。由此,直到执行该巡检处理为止,在巡检进度信息23中存储该巡检处理延迟的意思。在步骤st25之后,处理省略步骤st26和st27。

[0198]

在步骤st26中,存储器系统3基于判定为能够执行的巡检处理的类别,执行点检用巡检处理或更新用巡检处理中的任一个。存储器控制器30将点检用巡检处理或更新用巡检处理的结果存储于巡检结果信息22。关于点检用巡检处理以及更新用巡检处理的详细,在后面叙述。

[0199]

在步骤st27中,存储器控制器30更新巡检管理信息21。具体而言,例如,根据所执行的巡检处理的周期,重新设定巡检管理信息21内的对应的巡检指定单元pu。

[0200]

在步骤st28中,主机设备2发出巡检结果信息以及巡检进度信息的取得请求(指令集)。

[0201]

在步骤st29中,存储器控制器30将巡检结果信息22以及巡检进度信息23输出至主机设备2。

[0202]

通过以上,包括巡检处理在内的一系列的动作结束。

[0203]

1.2.4.2点检用巡检处理

[0204]

接着,对第1实施方式的信息处理系统中的点检用巡检处理进行说明。图19是表示第1实施方式的信息处理系统中的点检用巡检处理的流程图。

[0205]

如图19所示,在步骤st31中,存储器系统3执行巡检读出处理。具体而言,存储器控制器30发出读出指令,并发送至nand闪存器10。读出指令例如包括对巡检对象的页进行指定的物理地址add、和对在该巡检读出处理中施加的读出电压进行指定的dac(digital to analogue convertor)值。nand闪存器10在接受到读出指令时,从巡检对象的页读出数据,并输出至存储器控制器30。这样,点检用巡检处理中的巡检读出处理将1页作为巡检对象的单位来执行。

[0206]

此外,读出指令中包括的dac值,例如对应于读出电压的从初始值起的变化量。存储器控制器30基于在步骤st31之前执行的更新用巡检处理的结果,预先存储该dac值。由此,存储器系统3能够使用基于最新的更新用巡检处理的结果的读出电压,来执行巡检读出处理。

[0207]

在步骤st32中,存储器控制器30内的ecc电路34对通过巡检读出处理从nand闪存器10读出的数据执行错误订正处理。

[0208]

在步骤st33中,存储器控制器30判定错误订正处理是否成功。在错误订正处理成功的情况下(步骤st33;是),处理进入到步骤st34,在错误订正处理失败的情况下(步骤st34;否),处理进入到步骤st35。

[0209]

在步骤st34中,存储器控制器30判定通过错误订正处理检测出的错误比特数是否为阈值n1以上。在错误比特数为阈值n1以上的情况下(步骤st34;是),处理进入到步骤st35,在错误比特数小于阈值n1的情况下(步骤st34;否),点检用巡检处理结束。

[0210]

在步骤st35中,存储器控制器30将巡检结果信息22中的与包括巡检对象的块blk对应的刷新标志更新为“真”。由此,存储器控制器30能够存储从巡检对象读出的数据所包括的错误比特数为阈值n1以上、且对于包括该巡检对象的块blk而言需要刷新处理这样的内容。

[0211]

通过以上,点检用巡检处理结束。

[0212]

1.2.4.3更新用巡检处理

[0213]

接着,对第1实施方式的信息处理系统中的更新用巡检处理进行说明。图20是表示第1实施方式的信息处理系统中的更新用巡检处理的流程图。

[0214]

如图20所示,在步骤st41中,存储器系统3执行巡检读出处理。关于巡检读出处理的概要,与在图19的步骤st31中说明的巡检读出处理相同,因此省略说明。

[0215]

在步骤st42中,存储器控制器30判定是否从巡检对象的全部页读出了数据。在从巡检对象的全部页读出了数据的情况下(步骤st42;是),处理进入到步骤st43,在巡检对象的页中存在未读出数据的页的情况下(步骤st42;否),处理返回到步骤st41。

[0216]

在更新用巡检处理中,与点检用巡检处理不同,使用从同一单元组cu内的1个或多个页读出的数据,执行后述的读出电压更新处理。例如,在图13和图14所示的巡检模式b中,

更新用巡检处理全部使用从同一单元组cu的4页读出的数据,执行读出电压更新处理。因此,存储器控制器30按照读出电压更新处理中使用的规定的页数的量,重复步骤st41。

[0217]

在步骤st43中,存储器控制器30中的ecc电路34对在步骤st41中读出的数据执行错误订正处理。由此,存储器控制器30取得通过巡检读出处理读出的数据的错误订正后数据。

[0218]

在步骤st44中,存储器控制器30确定错误订正处理是否成功。在针对全部页的错误订正处理成功的情况下(步骤st44;是),处理进入到步骤st45,在错误订正处理失败的页至少有1个的情况下(步骤st45;否),处理进入到步骤st48。

[0219]

在步骤st45中,存储器控制器30执行读出电压更新处理。由此,存储器控制器30计算读出电压的更新值,并存储与该计算出的更新后的读出电压对应的dac值。关于读出电压更新处理,在后面叙述。

[0220]

在步骤st46中,存储器控制器30判定通过错误订正处理检测出的错误比特数是否为阈值n1以上。在错误比特数为阈值以上的情况下(步骤st46;是),处理进入到步骤st48,在错误比特数小于阈值n1的情况下(步骤st46;否),处理进入到步骤st47。

[0221]

在步骤st47中,存储器控制器30基于在步骤st41中读出的数据和在步骤st43中取得的错误订正后数据,判定相邻的状态间(例如“er”状态与“a”状态之间的)的阈值电压分布的重复程度(错误比特数)是否为阈值n2以上。在相邻的状态间的阈值电压分布的重复的程度为阈值n2以上的情况下(步骤st47;是),处理进入到步骤st48,在小于阈值n2的情况下(步骤st47;否),更新用巡检处理结束。

[0222]

在步骤st48中,存储器控制器30将巡检结果信息22中的与包括巡检对象的块blk对应的刷新标志更新为“真”。由此,存储器控制器30能够存储从巡检对象读出的数据中包括的错误比特数为阈值n1以上、或者巡检对象中的阈值电压分布的扩展的程度为阈值n2以上、且对于包括该巡检对象的块blk而言需要刷新处理的内容。

[0223]

通过以上,更新用巡检处理结束。

[0224]

另外,在图20的例子中,对于在对巡检对象的全部页的数据执行巡检读出处理之后执行错误订正处理的情况进行了说明,但不限于此。例如,ecc电路34也可以在每次以页为单位从nand闪存器10读出数据时执行错误订正处理。

[0225]

图21是表示第1实施方式的信息处理系统中的读出电压更新处理的示意图。在图21中,作为一个例子,示出了与“s0”状态以及“s1”状态对应的2个阈值电压分布,示出了根据其重复的程度更新读出电压vs1的情况。

[0226]

在图21的(a)中,示出读出电压vs1和与“s0”状态以及“s1”状态对应的2个阈值电压分布交叉的阈值电压vopt相等的情况。在图21的(a)的情况下,将“s1”状态错误地读出为“s0”状态的存储器单元数e10(相当于图21的(a)中的区域(a)的面积)、与将“s0”状态错误地读出为“s1”状态和错误读出的存储器单元数e01(图21的(a)中的区域(b))相等。在该情况下,错误比特数e(存储器单元数e01与存储器单元数e10的和)可望成为最小,因此存储器控制器30判定为不需要更新读出电压vs1。

[0227]

在图21的(b)中,示出了读出电压vs1位于比与“s0”状态以及“s1”状态对应的2个阈值电压分布交叉的阈值电压vopt靠高电压侧的情况。在图21的(b)的情况下,存储器单元数e10比存储器单元数e01多。在该情况下,错误比特数e比图21的(a)的情况下的错误比特

数e多,不优选。因此,存储器控制器30使读出电压vs1以接近电压vopt的方式向低电压侧移位。

[0228]

在图21的(c)中,示出了读出电压vs1位于比与“s0”状态以及“s1”状态对应的2个阈值电压分布交叉的阈值电压vopt靠低电压侧的情况。在图21的(c)的情况下,“存储器单元数e10比存储器单元数e01少。在该情况下,错误比特数e比图21的(a)的情况下的错误比特数e多,不优选。因此,存储器控制器30使读出电压vs1以接近电压vopt的方式向高电压侧移动。

[0229]

此外,读出电压vs1越远离阈值电压vopt则存储器单元数e01与存储器单元数e10之差的绝对值可望越大。因此,存储器控制器30根据区域(a)与区域(b)之比的大小来决定读出电压vs1的移位量。由此,能够根据阈值电压分布的重复程度决定适当的移位量,能够以接近理想的电压vopt的方式更新读出电压vs1。

[0230]

1.2.4.4更新用巡检处理结果向点检用巡检处理的反映

[0231]

通过上述的更新用巡检处理而更新后的读出电压被应用于以后续执行的方式进行了计划的点检用巡检处理。

[0232]

图22是表示第1实施方式的信息处理系统中的更新用巡检处理与点检用巡检处理的关系的示意图。在图22中,作为一例,示出巡检模式b中的更新用巡检处理结果向点检用巡检处理的反映例。具体而言,图22的(a)示出在巡检模式b中分别应用更新用巡检处理以及点检用巡检处理的物理地址。图22的(b)示出在巡检模式b中的更新用巡检处理以及点检用巡检处理的前后应用于读出处理的读出电压的模式。

[0233]

如图22的(b)所示,在4天周期的第1天,依次执行点检用巡检处理以及更新用巡检处理。如上所述,点检用巡检处理不更新读出电压。因此,在点检用巡检处理的前后,应用于巡检读出处理的读出电压的模式保持“a”不变地不发生变化。因此,后续的更新用巡检处理应用模式“a”的读出电压。然后,通过更新用巡检处理将模式“a”更新为模式“b”。

[0234]

接着,在4天周期的第2天,依次执行点检用巡检处理和更新用巡检处理。在4天周期的第2天执行点检用巡检处理的物理地址与在第1天执行了更新用巡检处理的物理地址不同。然而,在第2天的点检用巡检处理中,能够应用模式“b”的读出电压。另外,第2天的更新用巡检处理也同样地应用模式“b”的读出电压。然后,通过更新用巡检处理将模式“b”更新为模式“c”。在第3天以后也是同样的。

[0235]

这样,通过更新用巡检处理而更新后的读出电压的模式也适用于在与更新用巡检处理不同的物理地址中执行的点检用巡检处理。由此,在将阈值电压分布的变动的趋势视为相同程度的范围内,能够共享能够期待进一步减少错误比特数的读出电压的模式,能够降低刷新处理的发生频率。

[0236]

1.3本实施方式的效果

[0237]

根据第1实施方式,主机设备2发出巡检管理信息设定请求,并发送至存储器系统3。巡检管理信息设定请求包括物理地址add、优先级pr、类别w以及周期pe的信息。由此,主机设备2能够任意地设定由存储器系统3执行的巡检处理的计划。因此,能够提高主机设备2的巡检处理的控制性。

[0238]

具体而言,主机设备2发出巡检模式登记请求“setpatcom”,并发送至存储器系统3。由此,主机设备2以及存储器系统3能够在块blk等特定的范围内,共享对字线wl、串单元

su、以及页p这样的个别的存储区域指定了不同的周期、不同的优先级、不同的类别的一组巡检处理的定型。由此,能够以巡检模式来指定每个块blk的巡检处理的设定。因此,能够以较少的指令数设定复杂的计划。

[0239]

此外,主机设备2发出巡检管理信息删除请求,并发送至存储器系统3。巡检管理信息设定请求包括与删除对象的巡检处理对应的物理地址add。由此,主机设备2能够向存储器系统3指示不执行判定为不需要的巡检处理的意思。因此,能够提高主机设备2的巡检处理的控制性。

[0240]

此外,主机设备2发出巡检结果信息以及巡检进度信息取得请求,并发送至存储器系统3。由此,主机设备2作为巡检处理的结果,能够适当地取得应该刷新的块blk的信息、延迟的巡检处理的信息等。因此,主机设备2能够基于该信息来判定是否需要执行刷新处理、是否需要变更巡检处理的优先级pr以及周期pe。因此,能够提高主机设备2的控制性。

[0241]

1.4第1实施方式的变形例

[0242]

第1实施方式不限于上述的例子,能够应用各种变形。

[0243]

例如,在上述的第1实施方式中,对在巡检管理信息21中以队列结构存储巡检处理的计划的情况进行了说明,但不限于此。例如,巡检管理信息21中也可以以表形式存储巡检处理的计划。在以下的说明中,省略与第1实施方式相同的结构以及动作的说明,主要对与第1实施方式不同的结构以及动作进行说明。

[0244]

图23是表示第1实施方式的变形例的信息处理系统的巡检管理信息21的概念图。在图23中,示出了以表形式存储巡检管理信息21的情况的一例。

[0245]

如图23所示,在巡检管理信息21中,例如针对每个块blk将巡检模式、周期pe以及执行标识符建立关联地存储。在图23的例子中,在块blk0以及块blkn中设定有以4天周期重复的巡检模式a。在块blk1中设定有以8天周期重复的巡检模式c。另外,在块blk2中没有设定任何巡检模式。

[0246]

执行识别符与巡检处理的执行日对应,在将块blk内分割为几个存储区域(物理地址add)的情况下,被分配给该分割后的每个物理地址。在图23的例子中,示出了块blk内分割为8个物理地址add1~add8的情况。因此,作为与块blk0及blkn对应的执行识别符,对在4天周期的第1天执行巡检处理的物理地址add1及add5分配执行识别符“1”。同样地,对在4天周期的第2天执行巡检处理的物理地址add2以及add6分配执行识别符“2”。对在4天周期的第3天执行巡检处理的物理地址add3以及add7分配执行识别符“3”。对在4天周期的第4天执行巡检处理的物理地址add4和add8分配执行识别符“0”。这样,执行识别符被分配与基于巡检处理的执行日的基于周期pe的余数相等的值。

[0247]

存储器控制器30定期地反复进行包罗性地参照上述那样的巡检管理信息21内的执行识别符的情况,执行巡回动作。由此,能够确定应该执行的巡检处理的物理地址add以及巡检模式,并在适当的定时执行该应该执行的巡检处理。

[0248]

图24是表示第1实施方式的变形例的信息处理系统中的巡回动作的流程图。

[0249]

如图24所示,在步骤st51中,存储器控制器30使计数值cnt递增。计数值是针对每个巡回动作递增的整数。

[0250]

在步骤st52中,存储器控制器30将变量k初始化为0。

[0251]

在步骤st53中,存储器控制器30参照巡检管理信息21,判定在块blkk内是否存在

设定了执行识别符的物理地址add。在存在设定了执行识别符的物理地址add的情况下(步骤st53;是),处理进入到步骤st54,在不存在设定了执行识别符的物理地址add的情况下(步骤st53;否),处理进入到步骤st56。

[0252]

在步骤st54中,存储器控制器30选择与计数值cnt的基于周期pe的余数(cnt%pe)相等的执行识别符对应的物理地址addi。例如,在k=1以及cnt=5的情况下,块blkk的巡检模式为巡检模式c(周期pe=8),因此cnt%pe=5,选择物理地址add5。

[0253]

在步骤st55中,存储器系统3对所选择的物理地址addi执行巡检处理。

[0254]

在步骤st56中,存储器控制器30判定是否巡回了全部的块blk。

[0255]

在存在未巡回到的块blk的情况下(步骤st56;否),处理进入到步骤st57。在步骤st57中,存储器控制器30使变量k递增。然后,处理返回到步骤st53。由此,重复步骤st53~st57,直到巡回了全部的块blk为止。

[0256]

然后,在已巡回了全部块blk的情况下(步骤st56;是),巡回动作结束。

[0257]

另外,在上述的例子中,说明了以升序对块blk进行巡回的情况,但不限于此。例如,在巡回动作的中途,某个块blk的优先级被变更为高优先级的情况下,也可以优先巡回该块。另外,即使是在步骤st54中选择出的物理地址addi,在被设定了较低的优先级的情况下,针对该物理地址addi的巡检处理也可以根据状况而跳过。

[0258]

根据第1实施方式的变形例,存储器控制器30能够基于表形式的信息而不是队列结构来控制巡检处理的计划。

[0259]

2.第2实施方式

[0260]

接着,对第2实施方式的信息处理系统进行说明。在第2实施方式中,主机设备2发出不指定周期pe的指令。存储器系统3与第1实施方式的不同点在于,根据该指令仅执行1次巡检处理这一点上。在以下的说明中,对与第1实施方式相同的结构以及动作,省略说明,主要对与第1实施方式不同的结构以及动作进行说明。

[0261]

2.1包括巡检处理在内的一系列操作

[0262]

图25是表示第2实施方式的信息处理系统中的包括巡检处理在内的一系列动作的流程图,与第1实施方式中的图18对应。在图25中,代替图18的步骤st21和st22,执行步骤st21a。

[0263]

在步骤st21a中,主机设备2发出巡检请求“patrolrunrequest”,并发送至存储器系统3。巡检执行请求“patrolrunrequest”中包括指定物理地址add、优先级pr、类别w以及管理标志f的信息,但不包括指定周期pe的信息。存储器系统3若接受巡检执行请求(指令集),则执行步骤st24~st27的处理。步骤st24~st27的处理与图18的情况相同,因此省略说明。

[0264]

在步骤st28中,主机设备2发出巡检结果信息以及巡检进度信息的取得请求。

[0265]

在步骤st29中,存储器控制器30将巡检结果信息22以及巡检进度信息23输出至主机设备2。

[0266]

通过以上,包括巡检处理在内的一系列的动作结束。

[0267]

图26是表示第2实施方式的信息处理系统中的巡检执行请求的指令序列的一例。

[0268]

如图26所示,主机设备2例如发出巡检执行请求“patrolrunrequest<chip0-blk0-wlk-su0><pr0><wupdate>”。当接收到该指令时,存储器控制器30对属于芯片

10-0的块blk0的字线wlk及串单元su0的单元组cu执行更新用巡检处理。这样,由于在巡检执行请求“patrolrunrequest”中不包括<周期>的信息,所以存储器控制器30仅执行1次该巡检处理,之后并不周期性地反复执行。

[0269]

2.2本实施方式的效果

[0270]

根据第2实施方式,主机设备2发出不包括《周期》的信息的巡检执行请求“patrolrunrequest”,并发送至存储器系统3。由此,存储器系统3能够基于来自主机设备2的指示,不周期性地重复地而点式地执行巡检处理。因此,能够提高使存储器系统3执行巡检处理时的主机设备2的控制性。

[0271]

此外,在上述的例子中,说明了主机设备2发出巡检执行请求作为与巡检管理信息设定请求不同的指令由此指示被执行仅1次的巡检处理的情况,但不限于此。例如,主机设备2也可以通过发出巡检管理信息设定请求来指示被执行仅1次的巡检处理。

[0272]

具体而言,巡检管理信息设定请求也可以在周期pe的项目中定义用于对仅执行1次巡检处理的意思进行指定的信息(例如,<peonce)。由此,能够抑制主机设备2使用的指令的数量的增加。

[0273]

3.第3实施方式

[0274]

接着,对第3实施方式的信息处理系统进行说明。第3实施方式与第1实施方式及第2实施方式的不同点在于,将存储器系统3推荐的巡检模式输出至主机设备2。在以下的说明中,省略与第1实施方式的变形例同等的结构以及动作的说明,主要对与第1实施方式的变形例不同的结构以及动作进行说明。即,在第3实施方式中,为了便于说明,对以表形式存储巡检管理信息21的情况进行说明。

[0275]

3.1巡检管理信息

[0276]

图27是表示第3实施方式的信息处理系统的巡检管理信息的概念图。在图27中,关于第1实施方式的变形例中的图23所示的周期及执行识别符,省略了图示。

[0277]

如图27所示,在巡检管理信息21中,针对各块blk存储指定巡检模式和推荐巡检模式。指定巡检模式是由主机设备2指定的巡检模式。与此相对,推荐巡检模式是相对于指定巡检模式独立地设定且被判定为优选在存储器系统3中设定的巡检模式。

[0278]

存储器系统3例如基于巡检处理的结果、nand闪存器10的状态等,来设定推荐巡检模式。另一方面,主机设备2从存储器系统3取得推荐巡检模式,并使用该推荐巡检模式,作为判定是否更新指定巡检模式时的参考信息。主机设备2既可以将指定巡检模式更新为与推荐巡检模式同等的巡检模式,也可以将指定巡检模式更新为与推荐巡检模式不同的巡检模式。

[0279]

在图27的例子中,对于块blk0,主机设备2指定同一巡检模式b0,存储器系统3推荐同一巡检模式b0。然而,对于块blk1,主机设备2指定巡检模式b2,但存储器系统3推荐巡检模式b1。此外,对于块blk2,主机设备2不指定巡检模式,但存储器系统3推荐巡检模式b1。这样,对于同一块blk,存储器系统3可能存在推荐主机设备2指定的巡检模式的情况和推荐主机设备2不指定的巡检模式的情况。

[0280]

存储器控制器30例如根据优先级pr的高度以及周期pe的长度(执行频率)将指定巡检模式以及推荐巡检模式进行排序并存储。在以下的说明中,对于图27所示的巡检模式b0~b3,在巡检模式b0中设定优先顺序最高的优先级pr,并且设定执行频率多的周期pe。接

着,在巡检模式b1、b2以及b3中,按照该顺序设定优先顺序低的优先级pr,并且设定执行频率少的周期pe。并且,对将巡检模式的优先级pr变更为优先顺序更高的优先级pr或者将将周期pe变更为执行频率更多的周期pe的情况,表现为“提高巡检模式的等级”。另外,对将巡检模式的优先级pr变更为优先顺序更低的优先级pr或者将周期pe变更为执行频率更多的周期pe的情况,表现为“降低巡检模式的等级”。

[0281]

3.2巡检模式更新操作

[0282]

图28是表示第3实施方式的信息处理系统中的巡检模式更新动作的流程图。

[0283]

如图28所示,在步骤st61中,存储器系统3例如随着系统的启动,将推荐巡检模式初始化。

[0284]

在步骤st62中,主机设备2发出指定巡检模式设定请求,并发送至存储器系统3。指定巡检模式设定请求例如是与在第1实施方式中说明的巡检管理信息设定请求“patrolset”同等的指令,包括请求设定的巡检模式和作为该巡检模式的对象区域的nand闪存器10内的物理地址add。

[0285]

在步骤st63中,存储器系统3在接收到指定巡检模式设定请求时,参照巡检管理信息21,将与该指定巡检模式设定请求内所包括的物理地址add对应的指定巡检模式,设定为该指定巡检模式设定请求内所包括的巡检模式。

[0286]

在步骤st64中,存储器系统3判定写入处理时的温度是否小于阈值n3。具体而言,例如,nand闪存器10在执行写入处理时,基于来自在nand闪存器10内设置的温度传感器(未图示)的输出,向存储器控制器30输出温度信息。存储器控制器30基于来自nand闪存器10的温度信息,判定写入处理时的温度是否小于阈值n3。在温度为阈值n3以上的情况下(步骤st64;否),处理进入到步骤st67,在温度小于阈值n3的情况下(步骤st64;是),处理省略步骤st67。

[0287]

在步骤st65中,存储器系统3判定通过读出处理读出的数据(读出数据)的错误比特数是否小于阈值n4。具体而言,例如,nand闪存器10将读出数据输出至存储器控制器30。存储器控制器30内的ecc电路34对读出数据执行错误订正处理,算出错误比特数。存储器控制器30判定计算出的错误比特数是否小于阈值n4。在错误比特数为阈值n4以上的情况下(步骤st65;否),处理进入到步骤st67,在错误比特数小于阈值n4的情况下(步骤st65;是),处理省略步骤st67。

[0288]

在步骤st66中,存储器系统3判定基于更新用巡检处理的读出电压的更新量是否小于阈值n5。具体而言,例如,存储器控制器30基于在巡检管理信息21中设定的计划或者来自主机设备2的巡检执行请求“patrolrunrequest”,对nand闪存器10执行更新用巡检处理。由此,存储器控制器30将在nand闪存器10的巡检对象区域中被应用的读出电压更新。存储器控制器30将更新后的读出电压与更新前的读出电压进行比较,判定该读出电压的更新量是否小于阈值n5。在读出电压的更新量为阈值n5以上的情况下(步骤st66;否),处理进入到步骤st67,在读出电压的更新量小于阈值n5的情况下(步骤st66;是),处理省略步骤st67。

[0289]

在步骤st67中,存储器控制器30参照巡检管理信息21,提高针对对象区域的推荐巡检模式的等级。具体而言,在步骤st64中判定为温度为阈值n3以上的情况下,存储器控制器30针对写入对象区域提高设定的推荐巡检模式的等级。在步骤st65中判定为错误比特数为阈值n4以上的情况下,存储器控制器30针对读出对象区域提高所设定的推荐巡检模式的

等级。在步骤st66中判定为读出电压的更新量为阈值n5以上的情况下,存储器控制器30针对更新用巡检处理的对象区域提高设定的推荐巡检模式的等级。此外,在步骤st67中,由于指定巡检模式不被变更,因此后续执行的巡检处理的巡检模式的等级不变化。

[0290]

在步骤st68中,主机设备2发出推荐巡检模式输出请求(指令集),并发送至存储器系统3。推荐巡检模式输出请求例如包括请求输出的推荐巡检模式的对象区域即nand闪存器10内的物理地址add。

[0291]

在步骤st69中,存储器系统3在接收到推荐巡检模式输出请求时,参照巡检管理信息21,输出与该推荐巡检模式输出请求内包括的物理地址add对应的推荐巡检模式。

[0292]

在步骤st70中,主机设备2发出指定巡检模式设定请求,并发送至存储器系统3。在指定巡检模式设定请求中,例如包括在主机设备2与存储器系统3之间共享的巡检模式。

[0293]

此外,主机设备2也可以将在其与存储器系统3之间未被供给的新的巡检模式作为指定巡检模式包括在指定巡检模式设定请求中。在该情况下,主机设备2也可以如图11、图13及图15所示,在定义了新的巡检模式之后,发出指定巡检模式设定请求。另外,主机设备2也可以将构成巡检模式的多个巡检管理信息设定请求直接送出至存储器控制器30。

[0294]

在步骤st71中,存储器系统3在接收到指定巡检模式设定请求时,参照巡检管理信息21,将与该指定巡检模式设定请求内所包括的物理地址add对应的指定巡检模式更新为在该指定巡检模式设定请求内包括的巡检模式。

[0295]

通过以上,巡检模式更新动作结束。

[0296]

另外,在图28的例子中,对步骤st64~st66以此顺序执行的情况进行了说明,但不限于此。即,步骤st64~st66分别是根据对应的写入处理、读出处理及更新用巡检处理而执行的处理,因此图28所示的步骤st64~st66的执行顺序是任意的。

[0297]

图29是表示第3实施方式的信息处理系统中的巡检模式更新动作的示意图。图29的(a)表示例如图28的步骤st63的执行后的状态下的巡检管理信息21。图29的(b)表示例如图28的步骤st67的执行后的状态下的巡检管理信息21。图29的(c)表示例如图28的步骤st71的执行后的状态下的巡检管理信息21。

[0298]

如图29的(a)所示,存储器控制器30作为初始状态,对全部块blk的推荐巡检模式设定相同的巡检模式b1。另一方面,主机设备2根据块blk的使用状态(例如,擦除次数),指定不同的巡检模式。

[0299]

具体而言,例如,主机设备2对擦除次数比较多的块blk0指定巡检模式b1,对擦除次数比较少的块blk1指定更低等级的巡检模式b2。主机设备2对作为复制区域使用的块blkn指定比其他块blk低的等级的巡检模式b3。另外,主机设备2对未使用的块blk2不指定特定的巡检模式。

[0300]

如图29的(b)所示,通过执行对nand闪存器10的写入处理、读出处理及更新用巡检处理,存储器控制器30取得各种信息。

[0301]

例如,存储器控制器30基于对块blk0执行的写入处理时的nand闪存器10的温度为阈值n3以上这一情况,判定为处于块blk0中的阈值电压分布容易变动的状况。因此,存储器控制器30对块blk0的推荐巡检模式设定比指定巡检模式b1高1级别的等级的巡检模式b0。

[0302]

另外,例如,存储器控制器30基于来自块blk1的读出数据的错误比特数为阈值n4以上的情况,判定为块blk1中的阈值电压分布发生了变动。因此,存储器控制器30对块blk0

的推荐巡检模式设定比指定巡检模式b2高1级别的等级的巡检模式b1。在图29的(b)的情况下,结果为块blk1的推荐巡检模式的等级不变。

[0303]

另外,例如,存储器控制器30基于对块blkn执行的更新用巡检处理时的读出电压的更新量为阈值n5以上这一情况,判定为块blkn中的阈值电压分布发生了变动。因此,存储器控制器30对块blkn的推荐巡检模式设定比指定巡检模式b3高1级别的等级的巡检模式b2。

[0304]

如图29的(c)所示,主机设备2基于从存储器控制器30接受到的推荐巡检模式,更新指定巡检模式。

[0305]

例如,主机设备2对于块blk0及blk1,按照推荐巡检模式分别指定巡检模式b0及b1。另一方面,主机设备2对于块blkn,因为是复制区域,因此判定为不需要提高巡检模式的等级,继续指定巡检模式b3。

[0306]

通过如以上那样进行动作,主机设备2能够将来自存储器系统3的推荐巡检模式作为参考,并且总是自主地指定巡检模式。

[0307]

3.3本实施方式的效果

[0308]

根据第3实施方式,主机设备2发出推荐巡检模式输出请求。存储器系统3根据推荐巡检模式输出请求,将与从主机设备2指定的巡检模式独立地设定的推荐巡检模式向主机设备2输出。由此,主机设备2能够取得与指定巡检模式不同的、存储器系统3推荐的巡检模式,能够将该推荐巡检模式作为在存储器系统3中指定巡检模式时的参考。因此,能够提高主机设备2的巡检处理中的控制性。

[0309]

另外,存储器控制器30基于向nand闪存器10的写入处理时的温度、读出数据的错误比特数、或读出电压的更新量,设定推荐巡检模式。由此,存储器控制器30在检测到读出电压比设想更容易变动的状况的情况下,能够设定比指定巡检模式高的等级的推荐巡检模式。因此,在主机设备2设定指定巡检模式时,主机设备2能够将基于不相关的信息的有益的信息提供给主机设备2。

[0310]

3.4第3实施方式的变形例

[0311]

第3实施方式不限于上述的例子,能够应用各种变形。

[0312]

例如,在上述的第3实施方式中,对存储器控制器30不论有无来自主机设备2的请求,都根据写入处理时的温度、读出数据的错误比特数、以及读出电压的更新量等信息,适当设定推荐巡检模式的情况进行了说明,但不限于此。例如,存储器控制器30也可以根据来自主机设备2的请求,向nand闪存器10询问用于设定推荐巡检模式的信息。在以下的说明中,对于与第3实施方式相同的结构以及动作省略说明,主要对与第3实施方式不同的结构以及动作进行说明。

[0313]

图30是表示第3实施方式的变形例的信息处理系统中的推荐巡检模式输出动作的流程图。

[0314]

如图30所示,在步骤st68中,主机设备2发出推荐巡检模式输出请求,并发送至存储器控制器30。

[0315]

在步骤st81中,当接收到推荐巡检模式输出请求时,存储器控制器30向nand闪存器10询问推荐巡检模式。

[0316]

在步骤st82中,nand闪存器10根据来自存储器控制器30的询问,回答nand闪存器

10推荐的巡检模式。

[0317]

在步骤st69中,存储器控制器30将从nand闪存器10接受到的推荐巡检模式向主机设备2输出。

[0318]

通过如以上那样进行动作,存储器控制器30能够将反映了来自nand闪存器10的要求的推荐巡检模式向主机设备2输出。

[0319]

另外,在图30的例子中,对nand闪存器10相对于存储器控制器30具体地定义巡检模式的情况进行了说明,但不限于此。

[0320]

例如,nand闪存器10也可以根据来自存储器控制器30的询问,将构成自身的多个芯片10-0~10-n各自的器件id送出至存储器控制器30。由此,即使在芯片10-0~10-n各自具有互不相同的结构(例如互不相同的块blk、串单元su、字线wl、及位线bl的数量)的存储单元阵列17的情况下,存储器控制器30也能够根据该结构而设定最佳的巡检模式。

[0321]

另外,例如,nand闪存器10也可以根据来自存储器控制器30的询问,将不良的块blk的信息送出至存储器控制器30。由此,存储器控制器30能够针对各块blk的好坏获得更详细的信息。因此,存储器控制器30能够设定精度高的推荐巡检模式。

[0322]

4.其他

[0323]

在上述的第1实施方式至第3实施方式中,对根据阈值电压分布的重复程度来更新读出电压的情况进行了说明,但不限于此。例如,读出电压也可以通过推定出重复的阈值电压分布彼此交叉的阈值电压来更新。

[0324]

图31是表示其他变形例的信息处理系统中的更新用巡检处理的流程图。

[0325]

如图31所示,在步骤st91中,存储器系统3执行巡检读出处理。步骤st91中的巡检读出处理与图19的步骤st31中的巡检读出处理同样地,可以读出单元组cu内的特定页的数据,也可以仅使用1个读出电压来读出数据。

[0326]

在步骤st92中,存储器控制器30使用不同的读出电压,判定是否执行了规定数量的巡检读出处理。在执行了规定数量的巡检读出处理的情况下(步骤st92;是),处理进入到步骤st93,在未执行规定数量的巡检读出处理的情况下(步骤st92;否),处理返回到步骤st91。由此,存储器控制器30使在巡检读出处理中使用的读出电压一点一点地移位,直到该巡检读出处理被执行规定次数为止。

[0327]

在步骤st93中,存储器控制器30使用在步骤st91中一边使读出电压移位一边读出了规定数的数据,执行读出电压更新处理。例如,存储器控制器30在读出电压更新处理中,针对规定数量的读出电压的每一个,计算成为导通状态的存储单元的数量(导通单元数)。存储器控制器30基于导通单元数的变化量(区间单元数)计算读出电压的更新值,并存储与该计算出的更新后的读出电压对应的dac值。关于读出电压更新处理,在后面叙述。

[0328]

在步骤st94中,判定区间单元数的极小值是否为阈值n6以上。在区间单元数的极小值为阈值n6以上的情况下(步骤st94;是),处理进入到步骤st95,在区间单元数的极小值小于阈值n6的情况下(步骤st94;否),更新用巡检处理结束。

[0329]

在步骤st95中,存储器控制器30将巡检结果信息22中的与包括巡检对象的块blk对应的刷新标志更新为“真”。由此,存储器控制器30能够存储巡检对象的区间单元数为阈值n6、且对于包括该巡检对象的块blk而言需要刷新处理的内容。

[0330]

通过以上,更新用巡检处理结束。

[0331]

图32是表示其他变形例的信息处理系统中的读出电压更新处理的示意图。在图32的(a)中,作为一个例子,示出了与“s0”状态以及“s1”状态对应的2个阈值电压分布。在图32的(b)中,示出了导通单元数的推移。在图32的(c)中,示出了2个读出电压间的导通单元数变化量、即区间单元数的推移。另外,图32的(b)以及32(c)是与具有图32的(a)所示的阈值电压分布的单元组cu对应地描绘的图。

[0332]

如图32的(b)所示,若使读出电压向低电压侧移位,则在比作为“s1”状态的最频值的电压v1mid稍高的电压下,导通单元数急剧减少,|dm/dr|成为极大。在此,最频值是在图32的(a)中阈值电压的分布概率最高的电压,m是导通单元数,r是读出电压。如果进一步降低读出电压,则导通单元数的减少率变小,在某个值的读出电压下,导通单元数的减少率变得极小。在属于“s1”状态的阈值电压分布与属于“s0”状态的阈值电压分布不重叠的情况下,导通单元数的减少率的极小值为零。另一方面,在属于“s1”状态的阈值电压分布与属于“s0”状态的阈值电压分布重叠的情况下,导通单元数的减少率的极小值为不是零的值(>0)。而且,若进一步降低读出电压,则导通单元数的减少率再次变大,在比作为“a”状态的最频值的电压vs0mid稍高的电压下,|dm/dr|再次成为极大。

[0333]

通过上述的导通单元数的变化,能够检测2个状态间的阈值电压分布的重叠最小的读出电压(即,与2个状态的阈值电压分布的交点对应的读出电压)。例如,首先,使用读出电压r0进行巡检读出处理。将此时的导通单元数设为m0。接着,使用比电压r0低δv的电压r1进行巡检读出处理。将此时的导通单元数设为m1。于是,在读出电压从r0降低至r1时新断开的存储单元晶体管mt的数量为c1=m0-m1个。即,阈值电压为[r0,r1]间的区间单元数为c1个。

[0334]

接着,使用比电压r1低δv的电压r2进行巡检读出处理。将此时的导通单元数设为m2。于是,在读出电压从r1降低到r2时新截止的存储单元晶体管mt的数量为c2=m1-m2个。即,阈值电压为[r1,r2]间的区间单元数为c2个。而且,认为如果设为c1>c2,则|dm/dr|成为最小的电压至少位于比电压r1靠低电压侧的位置。

[0335]

接着,使用比电压r2低δv的电压r3进行巡检读出处理。将此时的导通单元数设为m3。于是,在读出电压从r2降低至r3时新断开的存储单元晶体管mt的数量为c3=m2-m3。即,阈值电压为[r2,r3]间的区间单元数为c3个。在此,如果是c3>c2,则得到图32的(c)那样的直方图。

[0336]

根据以上的结果,根据区间单元数,能够推定图32的(c)中的点划线所示那样的阈值电压分布。并且,能够推定出属于“s0”状态的阈值电压分布与属于“s1”状态的阈值电压分布的重叠最小的读出电压存在于电压r1与电压r2之间(区间单元数为极小值的区间)。

[0337]

存储器控制器30将读出电压更新为该区间单元数为极小值的区间内的电压值。由此,能够以接近理想的电压值vopt的方式更新读出电压。

[0338]

以上,对本发明的几个实施方式进行了说明,但这些实施方式是作为例子进行提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

[0339]

附图标记说明

[0340]1…

信息处理系统、2

…

主机设备、3

…

存储器系统、5

…

查找表、10

…

非易失性存储

器、11

…

输入输出电路、12

…

寄存器组、12a

…

状态寄存器、12b

…

地址寄存器、12c

…

指令寄存器、13

…

逻辑控制器、14

…

序列发生器、15

…

就绪/忙碌控制电路、16

…

电压生成电路、17

…

存储单元阵列、18

…

行解码器模块、19

…

读出放大器模块、20

…

易失性存储器、21

…

巡检管理信息、22

…

巡检结果信息、23

…

巡检进度信息、30

…

存储器控制器、31

…

处理器、32

…

缓冲存储器、33

…

主机接口电路、34

…

ecc电路、35

…

nand接口电路、36

…

dram接口电路。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1