一种SRAM芯片安全性能的测试方法

一种sram芯片安全性能的测试方法

技术领域

1.本发明涉及测试技术领域,尤其涉及一种sram芯片安全性能的测试方法。

背景技术:

2.在sram芯片投入使用前,需要对其进行安全性能的测试。为了保护数据安全,现有的安全芯片系统一旦检测到未授权的非法访问,会切断sram芯片的电源以避免攻击者窃取数据。但是,sram芯片存在信息残留问题,会部分恢复掉电前存储的信息。即利用某一存储单元长期存储固定数据时,对称的两个mos管将发生不同程度的bti老化效应,产生永久性阈值电压失配,导致该单元上电后有一定概率(约10%~20%)读出与原存储数值相反的上电初值。

3.现有技术测试sram芯片老化时存在变量单一的问题,目前,只考虑了电压对老化的影响。此外,通过比较图片的差异判断很难准确地评估sram芯片的老化情况。

技术实现要素:

4.鉴于上述的分析,本发明实施例旨在提供一种sram芯片安全性能的测试方法,用以解决现有技术评估变量过于单一、无法准确衡量老化程度的问题。

5.一方面,本发明实施例提供了一种sram芯片安全性能的测试方法,包括如下步骤:

6.对多个待测sram芯片上电,对其存储阵列的背栅电压进行初始化,获得每一待测sram芯片初始化后的一次上电初值;

7.向所有sram芯片写入统一数据,将写入统一数据后的sram芯片分组,每组设置不同的背栅电压,并分别在不同辐照环境中保持预定时间后断电;

8.对所有sram芯片重新上电,获得每一sram芯片重新上电后的二次上电初值;

9.分别将不同辐照环境下的每组中的每一sram芯片的二次上电初值、对应的一次上电初值输入至老化压印力度模型,获得不同辐照环境下每组中每一sram芯片的老化压印力度;

10.根据上述不同辐照环境下的每组中每一sram芯片的老化压印力度,得到所述待测sram芯片的安全性能测试结果。

11.上述技术方案的有益效果如下:提出了一种多变量且便于定量化的sram老化压印力度测试方法。考虑通过背栅电压以及辐照效应的引入,解决了现有技术测试sram芯片老化时变量单一的问题,同时通过试验测量的数据,以及自定义的老化压印力度模型,不再需要通过肉眼比较图片模糊程度判断老化情况,解决了老化压印力度难以定量评估的问题。通过比较一批sram芯片的抗老化压印能力,同时兼顾背栅与辐照等多个变量的影响因素,使最终对待测sram芯片安全性能达标的评估结果更加全面可信。上述方法能直接应用于已经投入使用的sram芯片,定量分析其安全性能是否达标,评估对应的安全系统是否存在安全漏洞。经大量试验验证,结果可信。

12.基于上述方法的进一步改进,所述上电初值为上电后待测sram芯片中值为1的存

储单元数量与值为0的存储单元数量的比值;

13.所述对多个待测sram芯片上电,并对其存储阵列的背栅电压进行初始化,获得每一待测sram芯片初始化后的一次上电初值的步骤,包括:

14.分别将每一待测sram芯片接入测试系统,通过测试系统对sram芯片上电;

15.将sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压均置为0v,完成初始化,统计初始化后存储阵列中1、0的个数与比例;

16.将上述过程重复n次,按照下式计算rate1,作为每一待测sram芯片初始化后的一次上电初值

[0017][0018]

式中,n

1i

为第i次测试中存储阵列单元为1的个数,n

0i

为第i次测试中存储阵列单元为0的个数,n为重复上电初始化的次数,也是测试次数。

[0019]

上述进一步改进方案的有益效果是:控制sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压,排除电压波动带来的干扰。重复统计上电初值,减小强抖动节点带来的影响。

[0020]

进一步,所述测试系统包括依次连接的测试板和fpga芯片;

[0021]

测试板,用于接入待测sram芯片,根据fpga芯片的控制对其存储阵列中所有nmos晶体管与pmos晶体管的背栅电压进行调节;以及,将sram芯片的存储阵列存储的信息输出至fpga芯片;

[0022]

fpga芯片,用于测试时向测试板发送初始化指令,所述初始化指令用于将sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压均置为0v;以及,初始化完成后,向测试板发送读写指令,并接收测试板反馈的存储阵列存储的信息;所述信息包括存储阵列中1、0的个数与比例。

[0023]

上述进一步改进方案的有益效果是:待测sram芯片-测试板-fpga芯片的连接形式简单方便,能够实现快速测试,获得数据(存储阵列存储的信息)。

[0024]

进一步,所述分组至少包括以下5组:

[0025]

nmos晶体管负偏且pmos晶体管负偏的分组;

[0026]

nmos晶体管负偏且pmos晶体管正偏的分组;

[0027]

nmos晶体管零偏且pmos晶体管零偏的分组;

[0028]

nmos晶体管正偏且pmos晶体管负偏的分组;

[0029]

nmos晶体管正偏且pmos晶体管正偏的分组;

[0030]

并且,每组至少包括15个sram芯片。

[0031]

上述进一步改进方案的有益效果是:考量了各种背栅的偏置情况,以确定老化压印的背栅最劣偏置条件。设置多组sram芯片进行测试,以保证数据的可信度。每组至少包括15个sram芯片,才能保证安全性能测试结果可信。

[0032]

进一步,所述辐照环境至少包括三种,每两种辐照环境的辐射剂量之间的跨度不小于100krad(si),最高辐射剂量大于300krad(si)。

[0033]

上述进一步改进方案的有益效果是:引入了辐照环境的考量,安全性能测试结果纳入了多种辐照环境对老化压印的影响。

[0034]

进一步,所述统一数据为全0或全1;

[0035]

辐射环境的辐射剂量率为50rad/s时,预定时间大于等于2000s。

[0036]

上述进一步改进方案的有益效果是:进一步保证每两种辐照环境的辐射剂量之间的跨度不小于100krad(si)。

[0037]

进一步,每个sram芯片的测试次数不少于3次。

[0038]

上述进一步改进方案的有益效果是:多次测试以确保数据的可信度。

[0039]

进一步,所述老化压印力度模型为

[0040][0041][0042]

式中,φ()为标准正态累积分布函数,ratio1为一次上电初值中1、0的比例,ratio3为二次上电初值中1、0的比例,σ

noise

为噪声影响因子,t为预定时间;fj表示第j次测试获得的老化压印力度fj,α为辐照环境系数,dose为辐照环境中的辐射剂量,v

p

、vn分别是测试时pmos晶体管与nmos晶体管的背栅电压。

[0043]

上述进一步改进方案的有益效果是:通过上述老化压印力度模型计算老化压印力度,该模型综合考虑了背栅电压、辐照剂量、上电初值以及噪声等多种变量,使获得的老化压印力度结果更加完善、可信。

[0044]

进一步,所述根据上述不同辐照环境下的每组中每一sram芯片的老化压印力度,得出该待测sram芯片的安全性能测试结果的步骤包括:

[0045]

将每组所有sram芯片测试的老化压印力度fj进行平均,作为该组芯片在对应辐射环境下的老化压印力度;

[0046]

根据m组sram芯片的老化压印力度,获得该待测sram芯片的最终老化压印力度评估指标f

total

;

[0047]

若最终老化压印力度f

total

在预设范围内,则输出该待测sram芯片的安全性能合格的测试结果。

[0048]

上述进一步改进方案的有益效果是:选取m组sram芯片的老化压印力度作为最终的老化压印力度评估指标,提高了评估结果的可信度,能够排除偶然情况的干扰。

[0049]

进一步,所述f

total

通过下面公式获得

[0050][0051]

式中,m为sram芯片的组数。

[0052]

上述进一步改进方案的有益效果是:以平均的方式计算获得待测sram芯片的最终老化压印力度评估指标,在保证数据可信度的前提下,简化计算过程,节省了计算资源。

[0053]

本发明中,上述各技术方案之间还可以相互组合,以实现更多的优选组合方案。本

发明的其他特征和优点将在随后的说明书中阐述,并且,部分优点可从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过说明书以及附图中所特别指出的内容中来实现和获得。

附图说明

[0054]

附图仅用于示出具体实施例的目的,而并不认为是对本发明的限制,在整个附图中,相同的参考符号表示相同的部件。

[0055]

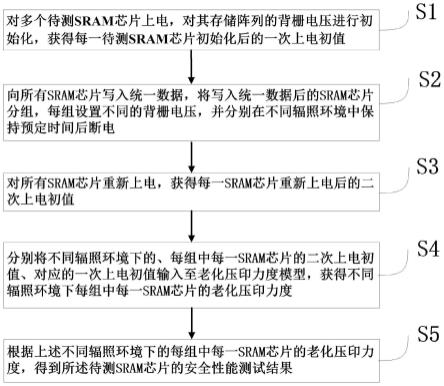

图1为本发明实施例1sram芯片安全性能的测试方法步骤示意图。

具体实施方式

[0056]

下面结合附图来具体描述本发明的优选实施例,其中,附图构成本技术一部分,并与本发明的实施例一起用于阐释本发明的原理,并非用于限定本发明的范围。

[0057]

实施例1

[0058]

本发明的一个具体实施例,公开了一种sram芯片安全性能的测试方法,如图1所示,包括如下步骤:

[0059]

s1.对多个待测sram芯片上电,并对其存储阵列的背栅电压进行初始化,通过统计获得每一待测sram芯片初始化后的一次上电初值;

[0060]

s2.向所有sram芯片写入统一数据,将写入统一数据后的sram芯片分组,每组设置不同的背栅电压,并分别在不同辐照环境中保持预定时间后断电;

[0061]

s3.对所有sram芯片重新上电,通过统计获得每一sram芯片重新上电后的二次上电初值;

[0062]

s4.分别将不同辐照环境下的、每组中的每一sram芯片的二次上电初值、对应的一次上电初值输入至老化压印力度模型,获得不同辐照环境下每组中每一sram芯片的老化压印力度;

[0063]

s5.根据上述不同辐照环境下每组中每一sram芯片的老化压印力度,得到该待测sram芯片的安全性能测试结果。

[0064]

实施时,首先对待测进行不同辐射环境、不同背栅电压的测试,然后对获得的测试结果通过老化压印力度模型进行综合分析,最终获得待测sram芯片的安全性能测试结果。

[0065]

与现有技术相比,本实施例提出了一种多变量且便于定量化的sram老化压印力度测试方法。考虑通过背栅电压以及辐照效应的引入,解决了现有技术测试sram芯片老化时变量单一的问题,同时通过试验测量的数据,以及自定义的老化压印力度模型,不再需要通过肉眼比较图片模糊程度判断老化情况,解决了老化压印力度难以定量评估的问题。通过比较一批sram芯片的抗老化压印能力,同时兼顾背栅与辐照等多个变量的影响因素,使最终对待测sram芯片安全性能达标的评估结果更加全面可信。上述方法能直接应用于已经投入使用的sram芯片,定量分析其安全性能是否达标,评估对应的安全系统是否存在安全漏洞。

[0066]

实施例2

[0067]

在实施例1的基础上进行优化,上电初值采用上电后sram芯片中值为1的存储单元数量与值为0的存储单元数量的比值表征。

[0068]

步骤s1进一步包括:

[0069]

s11.分别将每一待测sram芯片接入测试系统,通过测试系统对sram芯片上电;

[0070]

s12.将sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压v

bn

与v

bp

均置为0v,完成初始化,统计初始化后存储阵列中1、0的个数与比例;

[0071]

s13.重复上述步骤s11~s12的过程完成n次测试,依次获得n次测试结果中该sram芯片初始化后存储阵列中1、0的个数与比例,对所有1、0的个数n

1i

、n

0i

与比例求取平均,获得每一待测sram芯片初始化后的一次上电初值rate1[0072][0073]

式中,n

1i

、n

0i

分别为第i次测试该sram芯片初始化后存储阵列中1、0的个数。

[0074]

优选地,所述测试系统包括依次连接的测试板和fpga芯片。

[0075]

测试板,用于接入待测sram芯片,根据fpga芯片的控制对其存储阵列中所有nmos晶体管与pmos晶体管的背栅电压进行调节;以及,将sram芯片的存储阵列存储的信息输出至fpga芯片。

[0076]

fpga芯片,用于测试时向测试板发送初始化指令,所述初始化指令用于将sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压均置为0v;以及,初始化完成后,向测试板发送读写指令,并接收测试板反馈的存储阵列存储的信息;所述信息包括存储阵列中1、0的个数与比例。

[0077]

优选地,分组至少为5组,包括nmos晶体管负偏/pmos晶体管负偏、nmos晶体管负偏/pmos晶体管正偏、nmos晶体管零偏/pmos晶体管零偏、nmos晶体管正偏/pmos晶体管负偏、nmos晶体管正偏/pmos晶体管正偏各一组,见表1;每组至少包括15个sram芯片。

[0078]

表1

[0079][0080]

优选地,辐照环境至少包括三种。可设置为低/无/高三种,每两种辐照环境的辐射剂量之间的跨度不小于100krad(si),最高辐射剂量大于300krad(si)。统一数据为全0或全1。辐射环境的辐射剂量率为50rad/s时,预定时间大于等于2000s。每个sram芯片的测试次数不少于3次。多次上电-取平均,以降低极端特殊情况的干扰因素。

[0081]

优选地,步骤s2之后断电等待一段时间,排除数据残留干扰,再重新对sram芯片上电。

[0082]

优选地,老化压印力度模型为

[0083][0084]

式中,φ()为标准正态累积分布函数,ratio1为初始化后的一次上电初值中1、0的比例,ratio3为二次上电初值中1、0的比例,σ

noise

为噪声影响因子,取决于环境因素和实际设备情况,通过标定获得,t为预定时间;fj表示第j次测试获得的老化压印力度fj,α为辐照环境系数,dose为辐照环境中的辐射剂量,v

p

、vn分别是测试时pmos晶体管与nmos晶体管的背栅电压。

[0085]

优选地,步骤s5进一步包括:

[0086]

s51.将每组所有sram芯片n次测试(每个芯片的测试次数相同)的老化压印力度fj进行平均,作为该组芯片在对应辐射环境下的老化压印力度;

[0087]

s52.根据m组sram芯片的老化压印力度,获得该待测sram芯片的最终老化压印力度评估指标f

total

;所述f

total

通过下面公式获得

[0088][0089]

式中,m为sram芯片的组数。

[0090]

s53.根据上述f

total

判断最终老化压印力度是否在预设范围内,若在,判定该待测sram芯片安全性能达标,输出该待测sram芯片的安全性能合格的测试结果;否则,判定该类待测sram芯片的安全性能无法满足使用需求。

[0091]

具体地,预设范围根据sram实际应用场景的安全等级而定,取决于安全系统的防护能力以及sram内部存储信息的数据量与机密程度。

[0092]

与实施例1相比,本实施例提供的方法同时考虑了时间、背栅电压与总剂量效应,能更加全面地测试待测sram芯片的老化压印力度,并从多角度分析哪些因素会影响老化压印力度;采用写入全“0”或全“1”的方法来统计sram受老化压印以后数据的变化情况,能定量地分析老化压印力度,便于后续的数据处理。

[0093]

实施例3

[0094]

本发明还提供了一种与实施例1或2对应的sram芯片安全性能的评估系统,包括依次连接的测试板、fpga芯片和上位机。fpga芯片和上位机之间可通过无线通信。

[0095]

测试板,用于接入待测sram芯片,根据fpga芯片的控制对其存储阵列中所有nmos晶体管与pmos晶体管的背栅电压进行调节;以及,将待测sram芯片的存储阵列存储的信息输出至fpga芯片。

[0096]

通过上述测试板,将待测sram芯片的各个端口引出。

[0097]

fpga芯片,用于测试时向测试板发送初始化指令,所述初始化指令用于将待测sram芯片的存储阵列中所有nmos晶体管与pmos晶体管的背栅电压均置为0v;以及,初始化完成后,向测试板发送读写指令,并接收测试板反馈的存储阵列存储的信息;所述信息包括存储阵列中1、0的个数与比例。

[0098]

上位机,用于控制fpga芯片对sram芯片上电;以及,通过fpga芯片读取待测sram芯片存储阵列存储的内部数据信息,所述信息包括初始化后的一次上电初值、重新上电后的二次上电初值;并且,将所述一次上电初值、二次上电初值输入自定义的老化压印力度模型,获得各辐照环境下sram芯片的老化压印力度,根据上述所有辐照环境下待测sram芯片的老化压印力度,获得待测sram芯片安全性能是否良好的评估结果。

[0099]

值得注意的是,上电针对的是sram芯片的存储阵列的每一个内部单元,上电完成后,sram芯片的存储阵列应完成稳态的建立。

[0100]

sram芯片包含背栅信号端口,接入fpga芯片的io端口,通过控制io端口的电平电压进而控制背栅电压,实现背栅电压的0v设置。

[0101]

本领域技术人员可以理解,实现上述实施例方法的全部或部分流程,可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于计算机可读存储介质中。其中,所述计算机可读存储介质为磁盘、光盘、只读存储记忆体或随机存储记忆体等。

[0102]

以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1