记忆体装置的制作方法

1.本案是关于一种记忆体装置,特别是关于一种具有配置于列中的选择开关的三维记忆体装置。

背景技术:

2.在与较低功率消耗及较高速度需求组合的下一代半导体技术节点中制造的微电子装置内的增加的记忆体容量要求已驱动记忆体阵列内的每位元线记忆体单元的数目的增加。三维记忆体结构经利用于较高的记忆体单元密度。

技术实现要素:

3.根据本案的一实施例,提供记忆体装置。记忆体装置包括彼此并联耦接的多个阵列。阵列中的第一阵列包括配置于第一列中的第一开关及多个第一记忆体单元、配置于第二列中的第二开关及多个第二记忆体单元、第一数据线及第二数据线。第一数据线耦接至第一记忆体单元及第二记忆体单元。第二数据线耦接连接至第一记忆体单元及第二记忆体单元。第一开关响应于控制信号而在第一数据线中传输数据信号。第二开关响应于控制信号而输出自第二数据线接收的数据信号。

附图说明

4.当与随附附图一起阅读时,根据以下详细描述更好地理解本案的态样。应注意,根据工业中的标准实践,各种特征未按比例描绘。实际上,出于论述的清晰性可任意地增加或减少各种特征的尺寸。

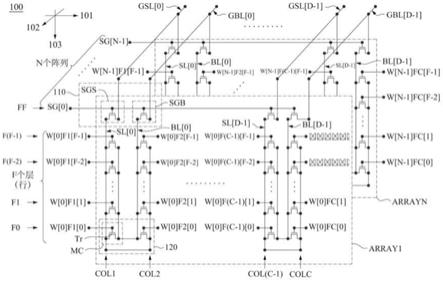

5.图1为根据本案一实施例的记忆体装置的部分的示意图;

6.图2为根据本案一实施例的图1中的记忆体装置的部分的示意图;

7.图3为根据本案一实施例的记忆体装置的部分的示意图;

8.图4为根据本案一实施例的图1中的记忆体装置的部分的平面图中的布置图;

9.图5为根据本案一实施例的图1中的记忆体装置的部分的平面图中的布置图;

10.图6a为根据本案一实施例的图1中的记忆体装置的部分的横截面图;

11.图6b为根据本案一实施例的图1中的记忆体装置的部分的横截面图;

12.图7为根据本案一实施例的记忆体装置的部分的示意图;

13.图8为根据本案的一些实施例的操作记忆体装置的方法的流程图。

14.【符号说明】

15.100:记忆体装置

16.101:方向

17.102:方向

18.103:方向

19.110:区域

20.120:区域

21.211:解码器

22.212:反向器

23.213:解码器

24.214:反向器

25.300:记忆体装置

26.411:导电部分

27.412:栅极氧化物部分

28.413:晶体管通道区

29.414:导电线

30.415:导电线

31.416:导电线

32.417:导电线

33.418:氧化物区

34.511:导电部分

35.611:通孔

36.612:导电线

37.613:通孔

38.614:导电线

39.700:记忆体装置

40.800:方法

41.810

‑

820:操作

42.array1

‑

arrayn:记忆体阵列

43.bl0.‑

bl[d

‑

1]:位元线

[0044]

sl0.‑

sl[d

‑

1]:来源线

[0045]

bl0.‑

bl[c

‑

1]:位元线

[0046]

sl0.‑

sl[c

‑

1]:来源线

[0047]

col1

‑

colc,col1

‑

col2c:列

[0048]

gbl0.‑

gbl[d

‑

1]:全域位元线

[0049]

gsl0.‑

gsl[d

‑

1]:全域来源线/来源线

[0050]

gbl0.‑

gbl[c

‑

1]:全域位元线

[0051]

gsl0.‑

gsl[c

‑

1]:全域来源线/来源线

[0052]

gw[0]f10.‑

gw[0]f1[f

‑

1],gw[0]f20.‑

gw[0]f2[f

‑

1]:全域字元线

[0053]

mc:记忆体单元

[0054]

tr:晶体管

[0055]

w[0]f10.‑

w[0]f1[f

‑

1]:字元线

[0056]

w[0]f20.‑

w[0]f2[f

‑

1]:字元线

[0057]

w[0]f(c

‑

1)0.‑

w[0]f(c

‑

1)[f

‑

1]:字元线

[0058]

w[0]fc0.‑

w[0]fc[f

‑

1]:字元线

[0059]

w[n

‑

1]f10.‑

w[n

‑

1]f1[f

‑

1]:字元线

[0060]

w[n

‑

1]f20.‑

w[n

‑

1]f2[f

‑

1]:字元线

[0061]

w[n

‑

1]f(c

‑

1)0.‑

w[n

‑

1]f(c

‑

1)[f

‑

1]:字元线

[0062]

w[n

‑

1]fc0.‑

w[n

‑

1]fc[f

‑

1]:字元线

[0063]

w[0]f(d

‑

1)0.‑

w[0]f(d

‑

1)[f

‑

1]:字元线

[0064]

w[n

‑

1]f10.‑

w[n

‑

1]f1[f

‑

1]:字元线

[0065]

w[n

‑

1]f(d

‑

1)0.‑

w[n

‑

1]f(d

‑

1)[f

‑

1]:字元线

[0066]

gsl0.‑

gsl[d

‑

1]:全域来源线/来源线

[0067]

sgs,sgb:选择开关

[0068]

sg0.‑

sg[n

‑

1]:选择线

[0069]

sti:浅沟槽隔离

[0070]

f0

‑

ff:层

具体实施方式

[0071]

以下揭示案提供用于实行所提供主题的不同特征的许多不同实施例或实例。以下描述组件及配置的特定实例以简化本案。当然,这些仅为实例且不欲为限制。例如,以下描述中的第二特征上方或第二特征上的第一特征的形成可包括其中第一特征及第二特征是直接接触地形成的实施例,且可亦包括其中额外特征可形成在第一特征与第二特征之间,使得第一特征及第二特征可不直接接触的实施例。另外,本案可在各种实例中重复元件符号及/或字母。此重复是用于简单性及清晰性的目的且实质上并不规定所论述的各种实施例及/或组态之间的关系。

[0072]

本说明书中使用的术语通常具有这些术语在本领域中及在使用每个术语的特定情境下的普通意义。本说明书中的实例的使用,包括本文所论述的任何术语的实例的使用,仅为例示性的,且决不限制本案的一实施例的范畴及意义或任何示范的术语的范畴及意义。同样地,本案不限于本说明书中给出的各种实施例。

[0073]

此外,为便于描述可在本文中使用诸如“在

……

下方”、“在

……

以下”、“下”、“在

……

以上”、“上”等的空间相对术语,以描述如图中所例示的一个元件或特征与另一元件(多个)或特征(多个)的关系。除附图中所描绘的定向之外,空间相对术语意欲涵盖使用或操作中的装置的不同定向。设备可以其他方式定向(旋转90度或以其他定向)且同样可据此解释本文使用的空间相对描述符。如本文所使用,术语“及/或”包括相关联的列表项目中的一或多个的任何及所有组合。

[0074]

如本文所使用,“大约”、“约”、“近似”或“大体上”通常应代表给定值或范围的任何近似值,其中其取决于其所属的各种技术而变化,且其范畴应符合其所属的技术中的技术者所理解的最广泛解释,以便涵盖所有此类修改及类似结构。在一些实施例中,其将通常意味在给定值或范围的20%内,较佳地在10%内,且更佳地在5%内。本文给出的数值量为近似的,从而意味术语“大约”、“约”、“近似”或“大体上”若未明确陈述,则可经推断,或意味其他近似值。

[0075]

传统记忆体阵列为配置在半导体基板的表面上的二维(two

‑

dimensional;2d)结构。为增加用于给定区域的记忆体容量,且为降低成本,单独记忆体单元的大小已降低。然

而,存在对单独记忆体单元的大小的减少,及因此对2d记忆体阵列的记忆体密度的技术限制。作为回应,诸如三维(three

‑

dimensional;3d)nand/nor快闪架构半导体记忆体装置的3d记忆体结构正经开发以进一步增加记忆体密度且降低记忆体成本。

[0076]

在三维架构半导体记忆体技术中,随着记忆体装置的阶层/层的数目增加,诸如通过堆叠垂直结构,位元线及来源线的rc负载增加且造成更坏的预充电及感测速度。例如,每个记忆体阵列中的记忆体单元耦接至一个记忆体阵列内的局部位元线及来源线。全域位元线耦接至所有记忆体阵列的局部位元线,且全域来源线耦接至所有记忆体阵列的局部来源线。当写入/读取操作经选择性地对特定记忆体阵列中的记忆体单元执行时,全域位元线中的一个将信号发射至连接至该全域位元线的所有局部位元线。为以另一方式解释,记忆体单元愈多,位元线/来源线在操作期间遭受的总rc负载愈大。在一些方法中,制造位元线/来源线柱的制程挑战上升。此外,位元线、来源线,及字元线的增加的数目导致巨大的面积惩罚。在其他方法中,字元线驱动器的数目响应于字元线的增加的数目而增加,且正努力在包括良好数量的字元线驱动器的受限装置面积中获得良好的面积效率。

[0077]

根据本案的一些实施例,新的三维记忆体阵列结构经提供来降低位元线及来源线的rc负载。记忆体单元配置在若干记忆体阵列中的多个列中。在一些实施例中,记忆体单元中的一部分及两个选择开关配置在记忆体阵列中的两个列中且耦接至局部位元线及局部来源线。选择开关用以响应于控制信号而导通。当选择开关导通时,全域位元线通过选择开关中的一个耦接至局部位元线且全域来源线通过选择开关中的另一个耦接至局部来源线。换言之,在操作期间,全域位元线连接至一个记忆体阵列中的一个局部位元线,而未连接至其他记忆体阵列中的其他局部位元线,且全域来源线的组态类似于全域位元线的彼组态。因此,位元线/来源线的rc负载降低。

[0078]

在本案的另一实施例中,用以传输用于启动不同记忆体阵列的相同行及相同列中的记忆体单元的字元线信号的字元线耦接在一起。换言之,多个字元线彼此耦接且用以接收来自字元线解码器的字元线信号。在选择开关导通以选择性地使特定位元线及来源线导电时,对应的记忆体单元经选择性地启动,甚至启动字元线信号经传输至若干记忆体单元。因此,与包括用于每个字元线的字元线解码器的一些方法相比,需要的字元线解码器的数目减少。因此,用于彼等字元线解码器的面积消耗降低。

[0079]

现参考图1,图1为根据本案一实施例的记忆体装置100的部分的示意图。在一些实施例中,记忆体装置100表示通常见于区块、装置,或其他记忆体单位中的较大数目的类似结构的一部分。如图1中例示性地所示,记忆体装置100包括若干记忆体阵列array1

‑

arrayn。记忆体阵列array1

‑

arrayn在方向102,亦即,y方向上彼此分离。为例示,记忆体阵列array1

‑

arrayn中的每一个包括配置在行及列col1

‑

colc中的记忆体单元mc的多个串。行在方向101(亦即,x方向)上延伸,且在一些实施例中,行中的记忆体单元mc称为配置在记忆体装置100的层fl0

‑

fl(f

‑

1)中。换言之,记忆体单元在方向103,亦即,z方向上堆叠,或垂直地堆叠在层中。c个列col1

‑

colc在方向103上延伸,其中c为正整数。在一些实施例中,记忆体单元mc包括具有源极、漏极及控制栅极的晶体管tr,如图1中所示。在各种实施例中,晶体管tr为电荷储存晶体管,且在其他实施例中,晶体管tr具有电荷捕捉结构或其他形式的储存结构。图1中的记忆体单元mc的组态经给出来用于例示性目的。记忆体单元mc的各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,记忆体单元mc进一步包括电阻性

元件。在各种实施例中,记忆体单元mc具有任何合适类型的记忆体架构。

[0080]

为例示,记忆体阵列array1

‑

arrayn中的每一个包括记忆体结构的多个层,包括存取线。如图1中所示,记忆体阵列array1具有例如耦接至列col1中的记忆体单元mc的控制栅极的字元线w[0]f10.‑

w[0]f1[f

‑

1]、耦接至列col2中的记忆体单元mc的控制栅极的字元线w[0]f20.‑

w[0]f2[f

‑

1],等等。类似地,记忆体阵列arrayn具有例如耦接至列col1中的记忆体单元mc的字元线w[n

‑

1]f10.‑

w[n

‑

1]f1[f

‑

1]、耦接至列col2中的记忆体单元mc的字元线w[n

‑

1]f20.‑

w[n

‑

1]f2[f

‑

1],等等。

[0081]

在一些实施例中,包括在记忆体阵列array1

‑

arrayn中的字元线位于记忆体装置100的分离层处。例如,字元线w[0]f1[f

‑

1]

‑

w[0]fc[f

‑

1]位于层fl(f

‑

1)中,且字元线w[0]f1[f

‑

2]

‑

w[0]fc[f

‑

2]沿方向103位于第一层下方的层fl(f

‑

2)中。如图1中所示,记忆体装置100包括f个层,其中f为正整数,诸如8、16、32、64等。

[0082]

为例示,记忆体阵列array1

‑

arrayn进一步包括多个数据线,例如,包括来源线sl0.‑

sl[d

‑

1]及位元线bl0.‑

bl[d

‑

1]。在一些实施例中,数目d为数目c的一半。如图1中例示性地所示,位元线bl[0]耦接至配置在列col1

‑

col2中的记忆体单元的端子,且来源线sl[0]耦接至配置在列col1

‑

col2中的记忆体单元的其他端子。具体而言,在一些实施例中,位元线bl[0]包括在方向103上延伸的第一部分及第二部分及在方向101上延伸的第三部分。来源线sl[0]亦包括三个部分,第一部分及第二部分在方向103上延伸且第三部分在方向101上延伸。换言之,来源线sl[0]及位元线bl[0]具有u形结构。在各种实施例中,来源线sl[0]的第三部分沿方向103位于位元线bl[0]的第三部分下方。来源线sl[1]

‑

sl[d

‑

1]及位元线bl[1]

‑

bl[d

‑

1]的组态类似于来源线sl[0]及位元线bl[0]的彼组态。因而,在此省略重复的描述。

[0083]

如图1中所示,记忆体阵列array1

‑

arrayn进一步包括多个选择开关sgs及sgb。在一些实施例中,选择开关sgs及sgb在方向103上配置在记忆体单元mc上方。具体而言,选择开关sgs及sgb位于层flfl(f

‑

1)上方的层flf中。选择开关sgs配置在奇数列中,包括例如列col1、col3等等。选择开关sgb配置在偶数列中,包括例如列col2、col4等等。为例示,相同记忆体阵列的相同层中的选择开关sgs及sgb的控制栅极一起耦接至控制线,例如,选择线sg0.‑

sg[n

‑

1]中的一个。作为一个实例,记忆体阵列array1的列col1中的选择开关sgs的一个端子耦接至来源线sl[0],且记忆体阵列array1的列col2中的选择开关sgb的一个端子耦接至位元线bl[0]。记忆体阵列array1

‑

arrayn中的其他选择开关的组态类似于记忆体阵列array1的列col1

‑

col2中的选择开关的彼组态。因而,在此省略重复的描述。

[0084]

记忆体装置100进一步包括多个数据线,例如,全域来源线gsl0.‑

gsl[d

‑

1]及全域来源线gbl0.‑

gbl[d

‑

1]。作为一实例,全域来源线gsl[0]耦接至记忆体阵列array1

‑

arrayn的列col1中的选择开关sgs的其他端子,且全域位元线gbl[0]耦接至记忆体阵列array1

‑

arrayn的列col2中的选择开关sgb的其他端子。在一些实施例中,全域来源线gsl0.‑

gsl[d

‑

1]及全域来源线gbl0.‑

gbl[d

‑

1]中的每一个具有在方向102上延伸的部分。

[0085]

继续参考图1,在一些实施例中,施加至图1中的选择线sg0.‑

sg[n

‑

1]及字元线的信号组合限定对记忆体单元mc中的选定的一个的诸如读取/规划操作的操作。选定的记忆体单元mc响应于字元线信号而经启动且用以通过位元线及来源线传输表示记忆体单元mc的状态的数据信号。

[0086]

具体而言,例如,在操作期间,记忆体阵列array1

‑

arrayn中的选择开关sgs及sgb分别用以响应于收到的控制信号cs0.‑

cs[n

‑

1]而导通。在一些实施例中,耦接至记忆体阵列array1中的选择线sg[0]的选择开关sgs及sgb响应于具有逻辑高值,亦即,1的控制信号cs[0]而导通。其他记忆体阵列array2

‑

arrayn中的选择开关sgs及sgb响应于具有逻辑低值,亦即,0的控制信号cs[1]

‑

cs[n

‑

1]而关断。因此,全域来源线gsl0.‑

gsl[d

‑

1]通过记忆体阵列array1中的选择开关sgs电气地耦接至记忆体阵列array1中的来源线gsl0.‑

gsl[d

‑

1]。全域位元线gbl0.‑

gbl[d

‑

1]通过记忆体阵列array1中的选择开关sgb电气地耦接至记忆体阵列array1中的位元线bl0.‑

bl[d

‑

1]。例如,全域来源线gsl[0]通过记忆体阵列array1的列col1中的选择开关sgs耦接至记忆体阵列array1中的来源线sl[0]。类似地,全域位元线gbl[0]通过记忆体阵列array1的列col2中的选择开关sgb耦接至记忆体阵列array1中的来源线bl[0]。

[0087]

此外,在以上提到的实施例中,例如,具有逻辑高值(亦即,1)的启动字元线信号经传输至字元线w[0]f1[f

‑

1],记忆体阵列array1的层fl(f

‑

1)中的个别记忆体单元mc响应于字元线信号而经启动。同时,具有逻辑低值(亦即,0)的字元线信号经传输至记忆体装置100中的其余字元线。因此,耦接至字元线w[0]f1[f

‑

1]的记忆体单元mc经选择以操作来通过选择开关sgb、位元线bl[0]、来源线sl[0],及选择开关sgb传输对应于选定的记忆体单元mc的逻辑状态的数据信号。换言之,选择开关sgs用以将来源线sl[0]中的数据信号传输至全域来源线gsl[0]。选择开关sgb用以将自位元线bl[0]接收的数据信号输出至全域位元线gbl[0]。选择开关sgs及sgb通过控制信号cs[0]控制。在一些实施例中,全域位元线gbl[0]将数据信号传输至感测放大器(未示出)以决定记忆体单元mc的所储存状态。

[0088]

如以上提到的,在图1的实施例中,在行方向(亦即,方向101)上彼此邻近地配置的记忆体单元mc中的两个用以响应于不同字元线信号而启动。例如,记忆体阵列array1的层fl(f

‑

1)中的字元线彼此隔离。因此,耦接至层fl(f

‑

1)中的字元线的记忆体单元响应于不同字元线信号而启动。具体而言,耦接至来源线sl[0]及位元线bl[0]的记忆体单元响应于自字元线w[0]f10.‑

w[0]f1[f

‑

1]及w[0]f20.‑

w[0]f2[f

‑

1]接收的不同字元线信号而启动。记忆体装置100中的其他记忆体单元mc的组态类似于记忆体阵列array1中的示范性记忆体单元mc的该组态。因而,在此省略重复的描述。

[0089]

在一些方法中,每个记忆体阵列的每个列中的记忆体单元耦接至来源线及位元线的对。所有记忆体阵列的相同列(例如,第一列)中的来源线一起耦接至全域来源线,且所有记忆体阵列的相同列中的位元线一起耦接至全域位元线。换言之,当记忆体阵列中存在c个列时,在记忆体装置中需要总数2c个全域来源线及全域位元线。相反,在如图1中所示的本案的一实施例的组态的情况下,用于两个列的来源线与一个全域来源线耦接在一起且用于两个列的位元线与一个全域位元线耦接在一起。因此,记忆体装置仅具有总数c个全域来源线及全域位元线,该数目为一些方法中的该数目的一半。因此,选路资源经保留在本案的一实施例中的记忆体装置中。

[0090]

此外,在一些前面提到的方法中,全域来源线/全域位元线直接耦接至来源线/位元线,而不具有如图1中所示的选择开关。因而,例如,当一个全域来源线经选择且导通时,该全域来源线与耦接至该全域来源线的所有所有来源线电气地导通。以另一方式陈述该状况,一个全域来源线经历由所有耦接的来源线贡献的rc负载。来源线响应于包括在记忆体

装置中的更多层变得愈久,全域来源线具有愈大的负载。例如,存在具有f个层的n个记忆体阵列(亦即,耦接至一个全域来源线的总数n个来源线),且因此,由一个全域源极位元经历的总rc负载与数目n乘f成正比。

[0091]

在本案的一实施例的组态的情况下,当一个全域来源线经选择且导通时,该全域来源线通过一个选择开关sgs与仅一个来源线电气地导通。因此,与一些方法相比,一个全域来源线经历由来源线贡献的较小rc负载。例如,在一些方法中,贡献给具有16个记忆体阵列而无选择开关的记忆体装置中的全域来源线的来源线的电容为100个单位。在本案的一实施例的组态的情况下,贡献给全域来源线的来源线的电容削减至6.3个单位。在各种方法中,贡献给具有64个记忆体阵列而无选择开关的记忆体装置中的全域来源线的来源线的电容为800个单位。在本案的一实施例的组态的情况下,贡献给全域来源线的来源线的电容削减至6.4个单位。如以上所论述,具有本案的一实施例的组态的记忆体装置的预充电制程/速度及感测速度改良。

[0092]

给出图1的组态用于例示性目的。各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,具有逻辑低值的控制信号用以将选择开关导通。各种合适的信号经利用来根据实际应用替代地实行本案的一实施例。

[0093]

在各种实施例中,方向103及101分别为用于限定布置平面的x方向及y方向。方向102为z方向。换言之,本案的一实施例的记忆体阵列在x

‑

y平面中延伸,且全域来源线及全域位元线在z方向上延伸。

[0094]

现参考图2,图2为根据本案一实施例的图1中的记忆体装置100的部分的示意图。如图2中说明性地所示,记忆体装置100进一步包括若干全域字元线gw[0]f10.‑

gw[0]f1[f

‑

1]及gw[0]f20.‑

gw[0]f2[f

‑

1]、解码器211、反向器212、解码器213,及反向器214。为例示,全域字元线gw[0]f1[f

‑

1]耦接至配置在记忆体阵列array1

‑

arrayn中的层(亦即,行)flf及列col1中的记忆体单元。解码器211通过反向器212耦接至全域字元线gw[0]f1[f

‑

1]。记忆体装置100中的其他解码器211、反向器212,及全域字元线的组态类似于以上提到的彼等组态。因而,在此省略重复的描述。解码器213通过反向器214耦接至选择线sg0.‑

sg[n

‑

1]。为简单起见,在此省略耦接至包括在记忆体装置100中的字元线且具有图2中的说明的元件的类似组态的若干解码器、反向器,及全域字元线。

[0095]

在操作中,例如,解码器211用以接收字元线地址且通过反向器212将字元线信号输出至gw[0]f1[f

‑

1]。字元线信号进一步通过字元线w[0]f10.‑

w[0]f1[f

‑

1]传输至记忆体单元,以启动记忆体单元mc。解码器213用以通过反向器214将控制信号cs0.‑

cs[n

‑

1]传输至选择线sg0.‑

sg[n

‑

1]。在前面提到的实施例中,耦接至选择线sg[0]的选择开关sgs及sgb响应于启动控制信号cs[0]而导通,且耦接至字元线w[0]f1[f

‑

1]的记忆体单元mc经启动。记忆体单元mc通过记忆体阵列array1中的全域来源线gsl[0]、全域位元线gbl[0],及来源线sl[0]传输数据信号,如图2中所示。换言之,通过选择性地导通选择开关sgs及sgb,耦接至相同全域字元线的记忆体单元之中的特定一个记忆体单元mc经启动以传输数据信号。

[0096]

在无选择开关的组态的一些方法中,配备一个解码器用于不同记忆体阵列的不同层中的记忆体单元中的一个。例如,记忆体装置在4个记忆体阵列中的每一个中具有32个层,且需要总共128个解码器来选择性地启动记忆体单元。相反,在本案的一实施例中的选择开关的组态的情况下,每层一个解码器211与4个记忆体阵列共享。因此,需要总共36个解

码器(亦即,用于32个层的全域字元线的32个解码器及用于4个记忆体阵列中的选择开关的4个系列的解码器)。换言之,与一些方法相比,本案的一实施例将记忆体装置中的解码器的用量削减大约71.8%。在各种方法中,记忆体装置在8个记忆体阵列中的每一个中具有64个层,且需要总共512个解码器。相反,在本案的一实施例中的选择开关的组态中,需要总共72个解码器(亦即,用于64个层的全域字元线的64个解码器及用于8个记忆体阵列中的选择开关的8个系列的解码器)。换言之,与一些方法相比,本案的一实施例将记忆体装置中的解码器的用量削减大约85.9%。

[0097]

给出图2的组态用于例示性目的。各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,省略反向器212及214。

[0098]

现参考图3,图3为根据本案一实施例的记忆体装置300的部分的示意图。相对于图1至图2,为便于理解,图3中的相同元件以相同元件符号指定。除非需要介绍与图3中所示的元件的合作关系,否则本文为简洁起见省略了已在以上段落中详细论述的类似元件的特定操作。

[0099]

与图1相比,记忆体装置300包括两倍数量的全域来源线、全域位元线、来源线,及位元线及一半数目的层。为例示,记忆体装置300包括2c个列col1

‑

col2c及f/2个层中的全域来源线gsl0.‑

gsl[c

‑

1]、全域位元线gbl0.‑

gbl[c

‑

1]、来源线sl0.‑

sl[c

‑

1],及位元线bl0.‑

bl[c

‑

1]。在图3中,作为一实例,字元线w[0]f1[f/2]

‑

w[0]f1[f

‑

1]耦接至配置于记忆体阵列array1的列col1中的记忆体单元mc,且字元线w[0]f1[f/2

‑

1]

‑

w[0]f1[0]耦接至配置于记忆体阵列array1的列col2中的记忆体单元mc。记忆体装置300中的其他字元线的组态类似于字元线w[0]f10.‑

w[0]f1[f

‑

1]的彼组态。因而,在此省略重复的描述。

[0100]

给出图3的组态用于例示性目的。各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,与图1中的实施例相比,记忆体装置包括具有一半数个层的更多记忆体阵列,而非具有双倍数个列。

[0101]

现参考图4,图4为根据本案一实施例的如在图1中的区域110中圈出的记忆体装置100的部分的平面图中的布置图。相对于图1至图3,为便于理解,图4中的相同元件以相同元件符号指定。

[0102]

如图4中例示性地所示,在一些实施例中,导电部分411对应于图1中的选择线sg[0]。导电部分411的一部分、栅极氧化物部分412,及晶体管通道区413中的一部分包括在对应于图1中的选择栅极sgs的半导体结构中。导电部分411的另一部分、另一栅极氧化物部分412,及另一晶体管通道区413包括在对应于图1中的选择栅极sgb的半导体结构中。导电线414对应于图1中的来源线sl[0]。导电线415对应于图1中的全域来源线gsl[0]。导电线416对应于图1中的位元线bl[0]。导电线417对应于图1中的全域位元线gbl[0]。

[0103]

为例示,导电部分411、栅极氧化物部分412、晶体管通道区413在方向101上延伸。栅极氧化物部分412在方向101上彼此分离,且晶体管通道区413在方向101上彼此分离。导电线414

‑

415附接至包括在选择开关sgs中的晶体管通道区413。导电线416

‑

417附接至包括在选择开关sgb中的晶体管通道区413。导电部分411、栅极氧化物部分412、晶体管通道区413,及导电线414

‑

417由氧化物区418包围。

[0104]

在一些实施例中,当控制信号cs[0]以电压传输至选择线sg[0]以将选择开关sgs及sgb导通时,表示数据信号的电流通过晶体管通道区413在导电线414

‑

417中流动。

[0105]

现参考图4,图4为根据本案一实施例的如在图1中的区域120中圈出的记忆体装置100的部分的平面图中的布置图。相对于图1至图4,为便于理解,图5中的相同元件以相同元件符号指定。为简单起见,在图5中未示出对应的记忆体单元结构。

[0106]

如图5中例示性地所示,在一些实施例中,导电部分511对应于图1中的字元线w[0]f1[0]及w[0]f2[0]。浅沟槽隔离(shallow trench isolation;sti)配置于两个导电部分511之间。在一些实施例中,导电部分511、栅极氧化物部分412,及晶体管通道区413包括在对应于图1中的晶体管tr的半导体结构中。对应于图1中的来源线sl[0]的导电线414紧挨着导电线415配置,对应于导电线416对应图1中的位元线bl[0]。

[0107]

在一些实施例中,导电部分411、511、导电线414

‑

417包括例如选自由多晶硅(poly

‑

si)、多晶硅锗(poly

‑

sige)、金属材料等组成的群组的导电材料。例如,金属材料可包括钽、钛、钼、钨、铜、其组合等等。栅极氧化物部分412包括用于隔离的材料,例如,氮化物、氧化铝,及具有用于如记忆体单元mc的基于电荷的记忆体应用的陷阱特性的任何高k,及钙钛矿、钽酸锶铋(sbt)、钛酸铅锆(pzt)、氧化铪锆(hfzrox)、氧化铪(hfo)及用于如记忆体单元mc的基于铁电的记忆体应用的任何铁电特性。晶体管通道区413包括例如多晶硅(poly

‑

si)、低温多晶硅(ltps)、非晶硅、氧化铟镓锌的导电材料及任何半导体特性材料。

[0108]

现参考图6a,图6a为根据各种实施例的图1中的记忆体装置的部分的横截面图。相对于图1至图5,为便于理解,图6a中的相同元件以相同元件符号指定。为简单起见,在图6a中未示出对应的记忆体单元结构、选择开关、字元线及位元线。

[0109]

如图6a中所示,导电线414具有u形结构,该u形结构包括在方向103上延伸的第一部分及第二部分及在方向101上延伸的用来耦接导电线414的第一部分及第二部分的第三部分。在一些实施例中,导电线417、通孔611,及导电线612包括在对应于全域位元线bl[0]的结构中。导电线414及417、通孔611,及导电线612沿方向101以重复方式配置。

[0110]

现参考图6b,图6b为根据各种实施例的图1中的记忆体装置的部分的横截面图。相对于图1至图6a,为便于理解,图6b中的相同元件以相同元件符号指定。为简单起见,在图6b中未示出对应的记忆体单元结构、选择开关、字元线及来源线。

[0111]

如图6b中所示,导电线416具有u形结构,该u形结构包括在方向103上延伸的第一部分及第二部分及在方向101上延伸的用来耦接导电线416的第一部分及第二部分的第三部分。在一些实施例中,导电线415、通孔613,及导电线614包括在对应于全域来源线sl[0]的结构中。导电线415

‑

416、通孔613,及导电线614沿方向101以重复方式配置。

[0112]

给出图4至图6b的组态用于例示性目的。各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,来源线及位元线的大小及几何形状为不同的。

[0113]

现参考图7,图7为根据本案一实施例的记忆体装置700的部分的示意图。相对于图1至图6b,为便于理解,图7中的相同元件以相同元件符号指定。

[0114]

与图1的实施例相比,例如,记忆体装置700的记忆体阵列array1中的来源线sl[0]耦接至配置于四个列col1

‑

col4中的记忆体单元mc,而非一个源极/位元线耦接两个列中的记忆体单元。类似地,位元线bl[0]耦接至配置于四个列col1

‑

col4中的记忆体单元mc。此外,如图7中所示,位元线bl[0]及来源线bl[0]进一步具有在方向101上延伸的用来耦接列col2

‑

col3中的记忆体单元mc的第四部分。

[0115]

如图7中所示,记忆体装置700具有在全域来源线gsl[0]及全域位元线gbl[0]所延

伸到的第一列及最后列中的选择开关,而非具有每个列中的选择开关。换言之,与图1及图3中的实施例相比,选择开关的数目减少。

[0116]

记忆体阵列array2

‑

arrayn的组态类似于记忆体阵列array1的彼组态。因而,在此省略重复的描述。

[0117]

给出图7的组态用于例示性目的。各种实行在本案的一实施例的设想范畴内。例如,在一些实施例中,一个源极/位元线耦接至记忆体单元mc的多于四个列。

[0118]

现参考图8,图8为根据本案的一些实施例的操作包括例如记忆体装置100、300的记忆体装置的方法800的流程图。应理解,额外操作可提供在由图8所示的处理之前、期间,和之后,且对于方法的额外实施例,以下所描述的操作中的一些可经替换或消除。操作/处理的顺序可为可互换的。贯穿各种视图及例示性实施例,相同元件符号用来指定相同元件。方法800包括以下参考图1的记忆体装置100描述的操作810

‑

820。

[0119]

在操作810中,根据一些实施例,响应于控制信号cs[0],导通耦接至记忆体阵列array1中的选择线sg[0]的选择开关sgs及sgb。例如,选择开关sgs将来源线sl[0]耦接至全域来源线gsl[0],且选择开关sgb将位元线bl[0]耦接至全域位元线gbl[0]。如图1中所示,记忆体单元mc具有耦接至来源线sl[0]的第一端子及耦接至位元线bl[0]的第二端子。

[0120]

在操作820中,响应于字元线信号,对记忆体阵列array1中的记忆体单元mc中的一个执行操作(亦即,读取操作),以通过全域来源线gsl[0]、来源线sl[0]、位元线bl[0],及全域位元线gbl[0]传输数据信号。例如,耦接至字元线w[0]f1[f

‑

1]的记忆体单元mc在操作期间响应于在全域字元线gw[0]f1[f

‑

1]及字元线w[0]f1[f

‑

1]中传输的字元线信号而经存取。

[0121]

在一些实施例中,当耦接至记忆体阵列array1中的选择线sg[0]的选择开关sgs及sgb导通时,方法800进一步包括导通另一系列选择开关的操作,该另一系列的选择开关例如耦接至记忆体阵列arrayn中的选择线sg[n

‑

1]的选择开关sgs及sgb。具体而言,选择开关sgs将记忆体阵列arrayn中的来源线sl[0]耦接至全域来源线gsl[0]。选择开关sgb将记忆体阵列arrayn中的位元线bl[0]耦接至全域位元线gbl[0]。

[0122]

在一些实施例中,将耦接至记忆体阵列arrayn中的选择线sg[n

‑

1]的选择开关sgs及sgb导通。方法800进一步包括响应于字元线信号,对耦接至记忆体arrayn中的来源线sl[0]及位元线bl[0]以传输另一数据信号的记忆体单元mc中的一个执行操作的操作。字元线信号在全域字元线gw[0]f1[f

‑

1]及字元线w[n

‑

1]f1[f

‑

1]中传输。

[0123]

在一些实施例中,另一字元线信号在全域字元线gw[0]f1[f

‑

2]及字元线w[n

‑

1]f1[f

‑

2]中传输。方法800进一步包括响应于另一字元线信号,通过记忆体阵列arrayn中的来源线sl[0]及位元线bl[0]传输来自记忆体阵列arrayn的层fl(f

‑

1)中的记忆体单元mc的又一数据信号。

[0124]

如以上所描述,本案的记忆体装置包括选择开关,这些选择开关耦接在全域数据线与局部数据线之间且用以选择性地传输来自多个记忆体阵列之中的特定阵列的数据信号。局部数据线具有用来连接配置于邻近列中的记忆体单元的u形/w形结构。此外,各种记忆体阵列的相同列中的记忆体单元耦接至相同全域字元线。因此,字元线解码器/驱动器的数目减少。

[0125]

在一些实施例中,揭示记忆体装置,记忆体装置包括彼此并联耦接的多个阵列。阵

列中的第一阵列包括配置于第一列中的第一开关及多个第一记忆体单元、配置于第二列中的第二开关及多个第二记忆体单元、第一数据线及第二数据线。第一数据线耦接至第一记忆体单元及第二记忆体单元。第二数据线耦接连接至第一记忆体单元及第二记忆体单元。第一开关响应于控制信号而在第一数据线中传输数据信号。第二开关响应于控制信号而输出自第二数据线接收的数据信号。在一些实施例中,数据信号对应于第一记忆体单元及第二记忆体单元中的一个记忆体单元的逻辑状态。在一些实施例中,第一记忆体单元中的一个及第二记忆体单元中的一个配置于第一层中。第一开关及第二开关配置于第一层垂直上方的第二层中。在一些实施例中,第一开关及第二开关的控制端子并联耦接以接收控制信号。在一些实施例中,第一记忆体单元中的一个及第二记忆体单元中的一个在行方向上彼此邻近地配置且用以响应于不同的字元线信号而启动。在一些实施例中,第一数据线包括在列方向上延伸的第一部分及第二部分及在行方向上延伸的第三部分。第三部分的第一端子及第二端子分别耦接至第一记忆体单元中的一个及第二记忆体单元中的一个。在一些实施例中,记忆体装置进一步包括多个字元线,这些多个字元线各自用以分别将多个字元线信号中的一个传输至第一记忆体单元及第二记忆体单元中的一个。在一些实施例中,第一开关及第二开关、第一记忆体单元及第二记忆体单元,及第一数据线及第二数据线配置于记忆体阵列中。记忆体装置进一步包括多个记忆体阵列。记忆体阵列的第一行、第一列中的记忆体单元用以响应于字元线信号而启动。

[0126]

亦揭示记忆体装置,该记忆体装置包括多个记忆体阵列,这些记忆体阵列各自包括多个列中的多个开关及多个记忆体单元,及第一字元线。开关用以响应于控制信号而选择性地导通。第一字元线耦接至配置于记忆体阵列中的第n行及第m列中的第一记忆体单元,其中n及m为正整数。第一记忆体单元中的一个用以响应于自第一字元线接收的字元线信号而操作,以通过经导通的开关传输数据信号。在一些实施例中,记忆体阵列中的每一个进一步包括至少一个第一数据线及至少一个第二数据线。至少一个第一数据线耦接至开关中的第一开关及记忆体单元的第一端子,且用以接收数据信号。至少一个第二数据线耦接至开关中的第二开关及记忆体单元的第二端子,且用以输出数据信号。在一些实施例中,记忆体单元配置于四个列中,且开关中的第一开关及第二开关配置于四个列中的第一列及第二列中。在一些实施例中,开关配置于第一层中,且记忆体单元配置于第一层垂直下方的第二层中。在一些实施例中,记忆体阵列中的每一个进一步包括耦接至记忆体单元的第一数据线及第二数据线。记忆体装置进一步包括第三数据线及第四数据线。第三数据线用以通过开关中的第一开关选择性地耦接至第一数据线中的一个。第四数据线用以通过开关中的第二开关选择性地耦接至第二数据线中的一个。在一些实施例中,第一数据线及第二数据线具有在第一方向上延伸的第一部分及在不同于第一方向的第二方向上延伸的第二部分,及在不同于第一方向及第二方向的第三方向上延伸的第三数据线及第四数据线。在一些实施例中,开关通过在第二方向上延伸的连接线耦接。在一些实施例中,当阵列中的第一记忆体阵列中的开关导通时,阵列中的其他记忆体阵列中的开关关断。

[0127]

亦揭示包括以下操作的方法:响应于第一控制信号,导通并联地耦接的多个记忆体阵列中的第一记忆体阵列中的一系列开关,以将第一数据线与第二数据线耦接且将第三数据线与第四数据线耦接;以及响应于第一字元线信号,对第一记忆体阵列中的多个记忆体单元中的记忆体单元执行操作,以通过第一至第四数据线传输第一数据信号。第一记忆

体阵列中的记忆体单元具有通过第一数据线耦接在一起的第一端子及通过第三数据线耦接在一起的第二端子。在一些实施例中,方法进一步包括以下操作:当记忆体阵列中的第一记忆体阵列中的该系列开关关断时,响应于第二控制信号,导通记忆体阵列中的第二记忆体阵列中的一系列开关,以将第五数据线与第二数据线耦接且将第六数据线与第四数据线耦接。在一些实施例中,方法进一步包括以下操作:响应于第一字元线信号,对第二记忆体阵列中的多个记忆体单元中的记忆体单元执行操作,其中第二记忆体阵列中的记忆体单元中的记忆体单元耦接至第五数据线及第六数据线。在一些实施例中,方法进一步包括以下操作:响应于第二字元线信号,通过第一数据线、第二数据线、第五数据线及第六数据线传输来自第二记忆体阵列中的多个记忆体单元中的记忆体单元的第二数据信号。

[0128]

先前内容概括若干实施例的特征,使得熟悉此项技术者可更好地理解本案的态样。熟悉此项技术者应了解,这些熟悉此项技术者可容易地使用本案作为基础,以用于设计或修改用于执行相同目的及/或达成本文引入的实施例的相同优点的其他制程及结构。熟悉此项技术者亦应意识到这些等效构造不脱离本案的精神及范畴,且这些熟悉此项技术者可在不脱离本案的精神及范畴的情况下在本文中做出各种变化、置换,及变更。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1