用于执行存储器内处理的存储器装置的制作方法

用于执行存储器内处理的存储器装置

1.本技术基于并要求于2020年10月5日在韩国知识产权局提交的第10-2020-0128274号韩国专利申请的优先权,该韩国专利申请的全部公开出于所有目的通过引用包含在此。

技术领域

2.以下描述涉及一种通过使用存储器内算术单元来执行存储器内处理的存储器装置。

背景技术:

3.诸如图形算法的处理、神经网络的处理等的应用是计算密集型算术运算,并且需要具有大容量算术运算和存储器容量的计算系统。已经开发了能够执行计算系统的一些算术运算(计算操作)作为存储器装置的内部处理(或存储器内处理)的存储器装置。因此,可以通过存储器装置的内部处理来减少计算系统的算术运算的负担。然而,当将用于内部处理的单独处理硬件添加到存储器装置时,可能需要高效地执行存储器装置的算术运算处理的方法。

技术实现要素:

4.提供本发明内容来以简化的形式介绍下面在具体实施方式中进一步描述的构思的选择。本发明内容不意在确定要求保护的主题的关键特征或必要特征,也不意图用于帮助确定要求保护的主题的范围。

5.一种执行存储器内处理的存储器装置。

6.在一个总体方面,一种被配置为执行存储器内处理的存储器装置包括:多个存储器内算术单元,均被配置为执行流水线化的算术运算的存储器内处理;以及多个存储器存储体,被分配给所述多个存储器内算术单元,使得由n个存储器存储体形成的集合被分配给所述多个存储器内操作单元中的每个,每个存储器存储体被配置为在流水线化的算术运算被执行时执行从存储器内算术单元请求的数据的访问操作。所述多个存储器内算术单元中的每个存储器内算术单元被配置为:以小于或等于n与所述多个存储器存储体中的每个存储器存储体的第二操作频率的乘积的第一操作频率下操作。

7.算术运算可以被流水线化成能够在与第一操作频率对应的第一操作周期内被处理的多流水线级的子算术单元。

8.所述多个存储器内算术单元中的每个存储器内算术单元可以被配置为:在与所述多个存储器存储体中的每个存储器存储体的第二操作频率对应的第二操作周期内访问分配的n个存储器存储体中的任意数量的存储器存储体。

9.所述存储器装置可以包括:流水线寄存器,被配置为缓冲流水线化的算术运算的流水线级的子算术运算结果。

10.所述存储器装置可以包括:时钟分频器,被配置为基于外部提供的时钟信号来生

成用于所述多个存储器内算术单元以第一操作频率操作的第一时钟信号,并将第一时钟信号分配给所述多个存储器内算术单元。

11.所述存储器装置可以包括:存储体选择器,被配置为顺序地使能分配给包括在所述多个存储器内算术单元中的第一存储器内算术单元的所述n个存储器存储体中的一个或多个存储器存储体;多路复用器,被配置为向第一存储器内算术单元提供从由存储体选择器使能的所述一个或多个存储器存储体访问的数据;以及存储体仲裁器,被配置为控制要从多路复用器输出的数据。

12.存储体选择器可以被配置为基于第二操作频率而操作,并且存储体仲裁器被配置为基于第一操作频率而操作。

13.分配给包括在所述多个存储器内算术单元中的第一存储器内算术单元的所述n个存储器存储体可以包括存储有第一操作数的第一存储器存储体和存储有第二操作数的第二存储器存储体,所述存储器装置可以包括用于对第一操作数进行多路复用的第一多路复用器和用于对第二操作数进行多路复用的第二多路复用器,第一多路复用器和第二多路复用器可以设置在分配给第一存储器内算术单元的所述n个存储器存储体与第一存储器内算术单元之间。

14.第一多路复用器和第二多路复用器可以被配置为:在与第一操作频率对应的第一操作周期内向第一存储器内算术单元提供第一操作数和第二操作数。

15.在另一总体方面,一种被配置为执行存储器内处理的存储器装置包括:多个存储器内算术单元,被配置为执行流水线化的算术运算的存储器内处理;多个存储器存储体,被分配给所述多个存储器内算术单元中的每个存储器内算术单元,使得由n个存储器存储体形成的集合被分配给所述多个存储器内操作单元中的每个存储器内操作单元,每个存储器存储体被配置为在流水线化的算术运算被执行时执行从所述多个存储器内算术单元请求的数据的访问操作;以及至少一个多路复用器,被配置为向所述多个存储器内算术单元中的每个提供从分配给所述多个存储器内算术单元中的每个存储器内算术单元的所述n个存储器存储体之中的使能的至少一个存储器存储体访问的数据,其中,所述多个存储器内算术单元中的每个存储器内算术单元被配置为:以小于或等于n与所述多个存储器存储体中的每个存储器存储体的第二操作频率的乘积的第一操作频率操作。

16.根据以下具体实施方式、附图和权利要求,其他特征和方面将是清楚的。

附图说明

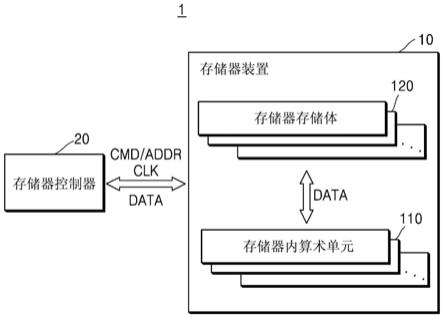

17.图1是示出根据示例的存储器系统的框图。

18.图2a和图2b是示出根据示例的存储器存储体与存储器内算术单元之间的分配比率的示图。

19.图3和图4是根据示例的用于比较和解释由于存储器内算术单元的操作频率的差异而导致的存储器存储体的操作之间的差异的示图。

20.图5是示出根据示例的四个存储器存储体被分配给以四倍操作频率操作的一个存储器内算术单元的示图。

21.图6a和图6b是根据示例的用于基于分配有四个存储器存储体的一个存储器内算术单元的操作频率来比较和解释存储器内算术单元的算术运算性能的示图。

22.图7是示出根据示例的算术运算的流水线的示图。

23.图8是示出根据示例的在存储器裸片上的存储器内算术单元与存储器存储体之间的硬件连接的示图。

24.图9示出当通过使用图8中示出的存储器装置的硬件来执行算术运算时的时序图。

25.图10是示出根据示例的当执行图7的流水线化的算术运算的存储器内处理时分配给相应存储器存储体的流水线级的示图。

26.图11是示出根据示例的在存储器内算术单元中执行的向量运算的示图。

27.图12是示出根据另一示例的在存储器裸片上的存储器内算术单元与存储器存储体之间的硬件连接的示图。

28.图13示出当通过使用图12中示出的存储器装置的硬件来执行算术运算时的时序图。

29.图14是示出通过使用图12中描述的硬件实施方式来执行对存储在不同存储器存储体中的不同操作数的存储器内处理的示图。

30.图15是示出根据示例的包括存储器装置的计算系统的框图。

31.在整个附图和具体实施方式中,除非另有描述或提供,否则相同的附图参考标号将被理解为指代相同的元件、特征和结构。附图可以不按比例,并且为了清楚、说明和方便,附图中的元件的相对尺寸、比例和描绘可以被夸大。

具体实施方式

32.提供以下具体实施方式以帮助读者获得对在此描述的方法、设备和/或系统的全面理解。然而,在理解本技术的公开之后,在此描述的方法、设备和/或系统的各种改变、修改和等同物将是清楚的。例如,在此描述的操作的顺序仅是示例,并且不限于在此阐述的操作的顺序,而是除了必须以特定的顺序发生的操作之外,操作的顺序可如在理解本技术的公开之后将是清楚的那样被改变。此外,为了更清楚和简明,可以省略在理解本技术的公开之后已知的特征的描述。

33.在此描述的特征可以以不同的形式实现,并且将不被解释为限于在此描述的示例。相反,提供在此描述的示例仅仅是为了示出在理解本技术的公开之后将是清楚的实现在此描述的方法、设备和/或系统的许多可行方式中的一些可行方式。

34.在整个说明书中,当组件被描述为“连接到”或“结合到”另一组件时,该组件可以直接“连接到”或“结合到”所述另一组件,或者可以存在介于它们之间的一个或多个其他组件。相反,当元件被描述为“直接连接到”或“直接结合到”另一元件时,它们之间可以不存在其他元件。同样地,类似的表述(例如,“在

……

之间”和“直接在

……

之间”以及“邻近”和“紧邻”)也将以相同的方式解释。如在此所使用的,术语“和/或”包括相关所列项中的任何一个和任何两个或更多个的任何组合。

35.尽管在此可以使用诸如“第一”、“第二”和“第三”的术语来描述各种构件、组件、区域、层或部分,但是这些构件、组件、区域、层或部分不应受这些术语的限制。相反,这些术语仅用于将一个构件、组件、区域、层或部分与另一构件、组件、区域、层或部分区分开。因此,在不脱离示例的教导的情况下,在此描述的示例中提及的第一构件、组件、区域、层或部分也可以被称为第二构件、组件、区域、层或部分。

36.在此使用的术语仅用于描述各种示例,而将不用于限制公开。除非上下文另有清楚地指示,否则单数形式也旨在包括复数形式。术语“包括”、“包含”和“具有”说明存在所陈述的特征、数量、操作、构件、元件和/或它们的组合,但不排除存在或添加一个或多个其他特征、数量、操作、构件、元件和/或它们的组合。

37.除非另有定义,否则在此使用的所有术语(包括技术术语和科学术语)具有与本公开所属领域的普通技术人员基于对本技术的公开的理解通常理解的含义相同的含义。术语(诸如,在通用词典中定义的术语)将被解释为具有与其在相关领域和本技术的公开的上下文中的含义一致的含义,并且将不以理想化或过于形式化的含义来解释,除非在此明确地如此定义。在此关于示例或实施例的术语“可以”的使用(例如,关于示例或实施例可以包括或实现什么)意味着存在包括或实现这样的特征的至少一个示例或实施例,而所有示例不限于此。

38.图1是示出根据示例的存储器系统的框图。

39.参照图1,存储器系统1可以包括存储器装置10和存储器控制器20。存储器装置10可以包括执行存储器内处理的多个存储器内算术单元110和包括多个存储器单元的多个存储器存储体120。

40.存储器装置10可以实现为存储器芯片或存储器模块。存储器控制器20可以实现为主机的部分,或存储器装置10和存储器控制器20也可以布置在一个存储器模块中。也就是说,实现形式可以是不同的,并且不限于一种配置。同时,尽管图1中未示出,但主机可以是控制存储器系统1以执行计算操作的功能块,并且可以充当中央处理器(cpu)、数字信号处理器(dsp)、图形处理器(gpu)或应用处理器(ap)。

41.存储器控制器20可以通过将各种信号提供给存储器装置10而控制存储器装置10的整体操作。例如,存储器控制器20可以控制存储器装置10的存储器存取操作(诸如,读取或写入)。具体地,存储器控制器20可以将命令cmd和地址addr提供给存储器装置10,以将数据data写入到存储器装置10或从存储器装置10读取数据data。另外,存储器控制器20还可以将时钟信号clk提供给存储器装置10。

42.命令cmd可以包括用于将存储器存储体120设置成激活状态以读取数据或写入数据的激活命令。存储器装置10可以响应于激活命令而激活包括在存储器存储体120中的行(即,字线)。另外,命令cmd可以包括用于在完成数据读取或数据写入之后将存储器存储体120从激活状态切换到待机状态的预充电命令。另外,命令cmd可以包括用于控制存储器存储体120的刷新操作的刷新命令。然而,在此描述的命令cmd的类型仅为示例性的,并且存在不同类型的命令cmd。

43.另外,存储器控制器20可以通过将各种信号提供给存储器装置10来控制存储器内算术单元110的存储器内处理操作。例如,存储器控制器20可以向存储器装置10提供通过使命令cmd、地址addr和/或时钟信号clk组合而生成用于指示存储器内算术单元110的存储器内处理操作的信号。

44.存储器内算术单元110可以实现为用于在存储器装置10中执行算术处理的处理元件(pe)。也就是说,存储器内算术单元110可以在存储器装置10中执行存储器内处理(或内部处理)。

45.具体地,存储器内算术单元110可以对存储在存储器存储体120中的数据data和/

或从存储器控制器20接收的数据data执行数据运算,并且可以将算术运算结果的数据data存储在存储器存储体120中或将数据提供给存储器控制器20。因此,存储器内算术单元110也可以被称为存储器内功能(function in memory,fim)或存储器内处理器(processor in memory,pim)。

46.存储器内算术单元110可以是算术逻辑单元(alu)或乘法累加(mac)。例如,存储器内算术单元110可以执行数据反转、数据移位、数据交换、数据比较、逻辑运算(诸如,与(and)和异或(xor))、数学运算(诸如,加法和减法)和数据运算。

47.包括在存储器装置10中的存储器内算术单元110的数量和包括存储器装置10中的存储器存储体120的数量可以被改变。另外,n个(其中,n是大于零的自然数)存储器存储体可以被分配给一个存储器内算术单元。

48.例如,当存储器装置10是双倍数据速率4动态随机存取存储器(ddr4dram)模块时,存储器存储体120的数量为16,并且存储器内算术单元110的数量为8。在此情况下,存储器内算术单元110和存储器存储体120可以以1:2(n=2且n是大于零的自然数)的比率映射。可选择地,存储器存储体120的数量可以为16,并且存储器内算术单元110的数量可以为4,在此情况下,存储器内算术单元110和存储器存储体120可以以1:4(n=4)的比率映射。也就是说,根据各种示例,存储器内算术单元110与存储器存储体120之间的映射比率可以变化。

49.每个存储器存储体120可以包括多个存储器单元。具体地,存储器存储体120的存储器单元可以位于多条字线和多条位线彼此交叉的点处。存储器存储体120可以存储存储器内处理数据。这里,存储器内处理数据可以包括将由存储器内算术单元110对其执行算术运算的数据和/或作为存储器内算术单元110的算术运算的结果而生成的数据。

50.存储器装置10可以包括各种类型的存储器(例如,动态随机存取存储器(dram)(诸如,双倍数据速率同步动态随机存取存储器(ddr sdram)、低功率双倍数据速率(lpddr)sdram、图形双倍数据速率(gddr)sdram或兰巴斯(rambus)动态随机存取存储器(rdram)))。然而,在此的各种示例不限于此,并且存储器装置10可以包括非易失性存储器(诸如,闪存、磁性随机存取存储器(mram)、铁电ram(feram)、相变ram(pram)或电阻式ram(reram))。

51.图2a和图2b是示出根据示例的存储器存储体与存储器内算术单元之间的分配比率的示图。

52.图1中示出的存储器装置10可以包括存储器裸片100,图1中示出的存储器内算术单元110和图1中示出的存储器存储体120布置在存储器裸片100中,并且图2a和图2b示出了包括在存储器裸片100中的一些存储器内算术单元110和包括在存储器裸片100中的一些存储器存储体120。

53.如图2a中所示,两个存储器存储体(第一存储器存储体121和第二存储器存储体122)可以被分配给一个存储器内算术单元(第一算术单元111),并且两个存储器存储体(第三存储器存储体123和第四存储器存储体124)可以被分配给一个存储器内算术单元(第二算术单元112)。

54.可选择地,如图2b中所示,四个存储器存储体(第一存储器存储体121、第二存储器存储体122、第三存储器存储体123和第四存储器存储体124)可以被分配给一个存储器内算术单元(第一算术单元111)。

55.也就是说,包括在存储器装置10中的存储器存储体120可以以n个存储器存储体为

单位共享一个存储器内算术单元,并且每个存储器内算术单元可以访问与其对应的n个存储器存储体以执行数据操作。这里,当存储器装置10对应于ddr4 dram模块时,n可以为2、4和8中的任何一个,但不限于此。

56.图3和图4是根据示例的用于比较和解释由于存储器内算术单元的操作频率的差异而导致的存储器存储体的操作之间的差异的示图。

57.参照图3和图4,两个存储器存储体(第一存储器存储体321或421和第二存储器存储体322或422)共享一个存储器内算术单元(第一算术单元311或411)。假设在第一存储器存储体321和421、第二存储器存储体322和422与第一算术单元311和411之间以x gb/s的速度执行数据发送和数据接收,并且假设存储器存储体321和421以及第二存储器存储体322和422以250mhz的操作频率(第二操作频率)操作。这里,250mhz的操作频率是为了便于描述的目的例示的随机值。

58.根据图3,当第一算术单元311的操作频率(第一操作频率)为与存储器存储体321和322中的每个的操作频率的两倍(n=2)对应的500mhz(2

×

250mhz)时,第一算术单元311可以在存储器存储体321和322中的每个的操作周期(1/(250

×

106)s=4ns)内基本同时访问第一存储器存储体321和第二存储器存储体322。

59.与此相比,根据图4,当第一算术单元411的操作频率(第一操作频率)为250mhz(其与存储器存储体421和422中的每个的操作频率相同)时,第一算术单元411可以在存储器存储体421和422中的每个的操作周期(4ns)内仅访问存储器存储体421和422中的一个。

60.因此,如果存储器内算术单元的操作频率(第一操作频率)增大到超过存储器存储体的操作频率(第二操作频率),则可以提高存储器内处理的性能。这里,图3示出了第一操作频率是第二操作频率的n倍的示例,但是操作频率不限于此,并且第一操作频率可以是第二操作频率的小于或等于n倍的特定倍数。也就是说,第一操作频率与第二操作频率之间的关系由以下等式1表示。

61.[等式1]

[0062]

第二操作频率

×

1《第一操作频率≤第二操作频率

×n[0063]

(n是映射到一个存储器内算术单元的存储器存储体的数量)

[0064]

也就是说,如作为图3中的第一算术单元311的算术运算性能的2y每秒千兆次运算(gops),存储器内计算单元的算术运算性能可以增大作为图4中的第一算术单元411的算术运算性能的y gops的两倍。在一个示例中,存储器内算术单元可在与第二操作频率对应的操作周期内访问分配的n个存储器存储体中的任意数量的存储器存储体。

[0065]

图5是示出根据示例的四个存储器存储体被分配给以四倍操作频率操作的一个存储器内算术单元的示图。

[0066]

参照图5,四个存储器存储体(第一存储器存储体521、第二存储器存储体522、第三存储器存储体523和第四存储器存储体524)共享一个存储器内算术单元(第一算术单元511)。假设在存储器存储体521、522、523和524与算术单元511之间以x gb/s的速度执行数据发送和数据接收,并且假设存储器存储体521、522、523和524以250mhz的操作频率(第二操作频率)操作。这里,250mhz的操作频率是为了便于描述的目的例示的随机值。

[0067]

根据图5,当第一算术单元511的操作频率(第一操作频率)是与存储器存储体521、522、523和524中的每个的操作频率(第二操作频率)的四倍(n=4)对应的1000mhz(4

×

250mhz)时,第一算术单元511可以在存储器存储体521、522、523和524中的每个的操作周期(1/(250

×

106)s=4ns)内基本同时访问存储器存储体521、522、523和524。

[0068]

也就是说,如果存储器内算术单元的操作频率(第一操作频率)与映射到一个存储器内算术单元的存储器存储体的数量成比例地增大,则可以在存储器存储体的操作周期内执行更高效的存储器内算术单元的算术处理(例如,4y gops)。

[0069]

图6a和图6b是根据示例的用于基于分配有四个存储器存储体的一个存储器内算术单元的操作频率来比较和解释存储器内算术单元的算术运算性能的示图。

[0070]

参照图6a,四个存储器存储体(第一存储器存储体621、第二存储器存储体622、第三存储器存储体623和第四存储器存储体624)被映射到一个存储器内算术单元(第一算术单元611)(n=4)。

[0071]

图6a的第一算术单元611的操作频率(第一操作频率)可以被设置为与存储器存储体621、622、623和624中的每个的操作频率(第二操作频率)的两倍(n=2)对应的500mhz(2

×

250mhz)。也就是说,如等式1所示,第一算术单元611的操作频率(第一操作频率)可以是存储器存储体621、622、623和624中的每个的操作频率(第二操作频率)的小于或等于n(n=4)倍的特定倍数(即,两倍)。因此,第一算术单元611可以在存储器存储体的操作周期(4ns)内基本同时访问任何两个存储器存储体(例如,一对存储器存储体621和622或一对存储器存储体623和624)。

[0072]

如图5中那样,当存储器内算术单元的操作频率(第一操作频率)基于映射到一个存储器内算术单元的存储器存储体的数量而增大时,可以在存储器存储体的操作周期内执行更高效的存储器内算术单元的算术处理(例如,2y gops)。

[0073]

图6b示出了一个存储器内算术单元(第一算术单元631)的操作频率(第一操作频率,250mhz)与存储器存储体(第一存储器存储体641、第二存储器存储体642、第三存储器存储体643和第四存储器存储体644)的操作频率(第二操作频率,250mhz)相同的情况。也就是说,“第一操作频率=第二操作频率=250mhz”。类似于参照图4进行的描述,图6b的第一算术单元631可以在存储器存储体641、642、643和644中的每个的操作周期(4 ns)内仅访问存储器存储体641、642、643和644中的一个(y gops)。

[0074]

图7是示出根据示例的算术运算的流水线的示图。

[0075]

流水线是通过将执行算术运算的处理划分为一些级并且并行(同时)处理各个级来提高算术处理速度的技术。

[0076]

参照图7,给定的算术运算被流水线化成多流水线级的一些子算术运算,从而流水线化的算术运算700可以被生成。这里,给定的算术运算可以为例如神经网络的mac算术运算,并且每个子算术运算可以对应于一系列单独的算术运算(诸如,数据获取、乘法运算、加法运算和数据输出)。

[0077]

将结合图6a和图6b描述以图7中示出的示例性操作频率(250mhz和500mhz)操作的存储器内算术单元的流水线处理。

[0078]

当以与图6b中示出的存储器内算术单元(第一算术单元631)的操作频率(即,250mhz)对应的4ns的操作周期为单位将给定的算术运算流水线化时,图6b的存储器内算术单元(第一算术单元631)可以在三个周期内处理流水线化的算术运算700(划分为三个流水线级stage 1、stage 2和stage 3的算术运算700),并且可以每个周期(操作周期:4 ns)执

行流水线。在这种情况下,如参照图6b所述的那样,存储器存储体(图6b中的641至644)中的每个的250mhz的操作频率(操作周期:4ns)与存储器内算术单元(第一算术单元631)的250mhz的操作频率(操作周期:4ns)相同,因此,存储器内算术单元(第一算术单元631)可以在存储器存储体(641至644)的操作周期(4ns)内仅访问存储器存储体641至644中的一个。

[0079]

然而,当以与图6a中示出的存储器内算术单元(第一算术单元611)的500mhz(2

×

250mhz)的操作频率对应的2ns的操作周期为单位将给定的算术运算流水线化时,图6a的存储器内算术单元(第一算术单元611)可以在六个周期内处理流水线化的算术运算700(划分为六个流水线级(或六个子算术运算)stage 1-1、stage 1-2、stage 2-1、stage 2-2、stage 3-1和stage 3-2的算术运算700),并且可以每个周期(2ns)执行流水线。在此情况下,如参照图6a所描述的那样,图6a中的存储器存储体621到624中的每个的250mhz的操作频率(操作周期:4ns)是存储器内算术单元(第一算术单元611)的500mhz的操作频率(操作周期:2ns)的一半,因此,存储器内算术单元(第一算术单元611)可以在存储器存储体621到624的操作周期(4ns)内,基本同时访问两个存储器存储体(例如,621和622),以一次处理与两个周期对应的子算术运算。

[0080]

也就是说,给定的算术运算被流水线化成多流水线级的子算术单元(或子算术运算)(多流水线级的子算术单元(或子算术运算)可以在与存储器内算术单元的第一操作频率对应的第一操作周期内被处理),并且当存储器内算术单元的第一操作频率比存储器存储体的第二操作频率高时,存储器内算术单元可以在相同时间内执行更多流水线算术运算的存储器内处理。这里,第一操作频率与第二操作频率之间的关系与由上述等式1表示的关系相同。在图7中,mul、add、acc reg.、demux分别表示乘法器、加法器、累加寄存器和解复用器。

[0081]

图8是示出根据示例的在存储器裸片上的存储器内算术单元与存储器存储体之间的硬件连接的示图。

[0082]

参照图8,示出了在存储器裸片100上四个存储器存储体bank1、bank2、bank3和bank4被分配给一个存储器内算术单元(第一算术单元111)的实现示例。这可以对应于设置在存储器裸片100中的图1中的所有存储器内算术单元110和图1中的所有存储器存储体120的实现示例中的一些。因此,存储器裸片100上的存储器内算术单元110和存储器存储体120中的其余的存储器内算术单元110和存储器存储体120可以与图8中示出的存储器内算术单元110和存储器存储体120类似地实现和操作。

[0083]

存储器内算术单元(第一算术单元111)在存储器裸片100上连接到各个存储器存储体。在这种情况下,存储器裸片100可以包括存储体选择器140和存储体仲裁器(bank arbiter)160,存储体选择器140选择分配给第一算术单元111的四个存储器存储体bank1、bank2、bank3和bank4中的任何一个,存储体仲裁器160用于控制多路复用器(mux)150(例如,控制要从多路复用器(mux)150输出的数据),多路复用器(mux)150向第一算术单元111提供从由存储体选择器140选择的存储器存储体访问的数据。在存储器裸片100上实现的硬件配置元件可以通过数据总线170彼此连接。在一个示例中,存储体选择器可顺序地使能分配给第一算术单元的四个存储器存储体bank1、bank2、bank3和bank4中的一个或多个存储器存储体。

[0084]

第一算术单元111可以以第一操作频率操作,以执行流水线化的算术运算810的存

储器内处理。这里,算术运算810可以被流水线化成多流水线级的子算术单元(或子算术运算),多流水线级的子算术单元(或子算术运算)可以在与第一算术单元111的第一操作频率对应的第一操作周期内被处理。第一算术单元111可以包括至少一个流水线寄存器1111,至少一个流水线寄存器1111用于缓冲流水线化的算术运算810的每个流水线级中的子算术运算结果。

[0085]

存储器存储体bank1、bank2、bank3和bank4中的每个可以以第二操作频率操作,以在流水线化的算术运算被执行时执行从第一算术单元111请求的数据的访问操作。

[0086]

时钟分频器130可以将从外部装置(图1的存储器控制器20、主机等)提供的时钟信号bank clk分配给存储器内算术单元(第一算术单元111)以及存储器存储体bank1、bank2、bank3和bank4。这里,时钟分频器130可以将时钟信号bank clk按原样提供给存储器存储体bank1、bank2、bank3和bank4,并向存储器内算术单元(第一算术单元111)提供第一时钟信号clk1,以使存储器内算术单元(第一算术单元111)以第一操作频率操作。

[0087]

也就是说,时钟分频器130可以基于第一操作频率与第二操作频率之间的关系从时钟信号bank clk生成第一时钟信号clk1,并且可以分配第一时钟信号clk1。例如,如参照图6a所描述的那样,当第一操作频率是第二操作频率的两倍时,第一时钟信号clk1的频率可以是时钟信号bank clk的频率的两倍。然而,第一时钟信号clk1可以根据分配给一个存储器内算术单元的存储器存储体的数量n或第一操作频率与第二操作频率之间的关系(等式1)而改变。

[0088]

第一算术单元111以作为存储器存储体bank1、bank2、bank3和bank4中的每个的第二操作频率的两倍的第一操作频率操作。换句话说,第一操作频率是第二操作频率的两倍。先前描述的是,n对应于分配给一个存储器内算术单元的存储器存储体的数量,并且第一操作频率与第二操作频率之间的关系由等式1表示。

[0089]

同时,存储体选择器140可以以与存储器存储体bank1、bank2、bank3和bank4相同的方式响应于时钟信号bank clk而以第二操作频率操作,并且存储体仲裁器160可以以与第一算术单元111相同的方式响应于第一时钟信号clk1而以第一操作频率操作。

[0090]

存储体选择器140可以通过第一端子1st在特定操作周期内向存储器存储体bank1和bank2的使能端子en提供用于使能存储器存储体bank1和bank2的控制信号,并且可以通过第二端子2nd在下一操作周期内向存储器存储体bank3和bank4的使能端子en提供用于使能存储器存储体bank3和bank4的控制信号。存储体仲裁器160可以控制多路复用器(mux)150,使得第一算术单元111可以在特定操作周期内顺序地访问使能的两个存储器存储体。

[0091]

图9示出通过使用图8中示出的存储器装置的硬件执行算术运算时的时序图。

[0092]

参照图9,时钟信号bank clk的频率是第一时钟信号clk divider_output(图8中的clk1)的频率的一半。

[0093]

在时钟信号bank clk的一个周期期间,存储器存储体bank1和bank2由通过存储体选择器140的第一端子1st输出的控制信号bank selector_1st使能。此时,存储器存储体bank3和bank4处于禁用状态。

[0094]

因为第一时钟信号clk divider_output的频率是时钟信号bank clk的频率的两倍,所以在第一时钟信号clk divider_output的两个周期期间,存储器存储体bank1的数据data1 911和存储器存储体bank2的数据data1 912可以被顺序地访问到第一算术单元111。

根据图8,在图9中,mux_input_bank1、mux_input_bank2、mux_input_bank3和mux_input_bank4分别表示从存储器存储体bank1、bank2、bank3和bank4输入到多路复用器(mux)150的信号,bank arbiter_output表示从存储体仲裁器160输出的信号,alu_input表示输入到第一算术单元111的信号。

[0095]

在时钟信号bank clk的下一个周期期间,其他存储器存储体bank3的数据data1 913和存储器存储体bank4的数据data1 914可以被顺序地访问到第一算术单元111。

[0096]

以此顺序,在时钟信号bank clk的四个周期期间,存储器存储体bank1、bank2、bank3和bank4的data1 911、data1 912、data1 913、data1 914、data2 921、data2 922、data2 923和data2 924可以作为第一算术单元111的输入被顺序地访问。

[0097]

图10是示出根据实施例的当执行图7的流水线化的算术运算的存储器内处理时将分配给每个存储器存储体的流水线级的示图。

[0098]

参照图10,将当存储器内算术单元的操作频率是存储器存储体的操作频率的两倍时的流水线级分配1020与当存储器内算术单元的操作频率与存储器存储体的操作频率相同时的流水线级分配1010进行比较。

[0099]

流水线化的算术运算700包括多流水线级的六个子算术运算stage 1-1至stage 3-2。由图8中示出的第一算术单元111执行的每个算术运算op#(例如,op1、op2或op3)可以对应于流水线化的算术运算700的六个子算术运算stage 1-1至stage 3-2中的一个。

[0100]

每个时间线(周期)中的流水线级分配1020对应于根据图6a中描述的第一算术单元611(操作频率:500mhz和操作周期:2ns)和存储器存储体621至624(操作频率:250mhz和操作周期:4ns)的存储器内处理的流水线。

[0101]

具体地,在第n周期期间,第一算术单元611访问第一存储器存储体621以执行子算术运算stage 1-1的第一算术运算op1,并且访问第二存储器存储体622以执行子算术运算stage 1-1的第一算术运算op1。同时,第一算术单元611可以从第一存储器存储体621访问第一算术运算op1的数据,并且同时执行下一子算术运算stage 1-2的第一算术运算op1的流水线。以这种方式,即使在图10中示出的第(n+5)周期和后续周期中,第一算术单元611也可以交替地访问存储器存储体621至624,从而执行流水线化的算术运算700。

[0102]

同时,流水线级分配1010对应于根据参照图6b描述的第一算术单元631(操作频率:250mhz和操作周期:4ns)和存储器存储体641至644(操作频率:250mhz和操作周期:4ns)的存储器内处理的流水线,并且当与上述流水线级分配1020相比时,第一算术单元131的算术运算吞吐量更低。也就是说,通过将存储器内算术单元的操作频率(第一操作频率)增大为超过存储器存储体的操作频率(第二操作频率),可以更快地处理更多算术运算吞吐量,因此可以提高存储器内算术单元的算术运算性能。

[0103]

图11是示出根据示例的由存储器内算术单元执行向量运算的示图。

[0104]

参照图11,为了存储器内算术单元1101执行存储在存储器存储体bank1和bank2中的操作数a和存储在存储器存储体bank3和bank4中的操作数b的向量运算,需要两个处理步骤。具体地,首先,存储器内算术单元1101访问第一存储器存储体bank1以读取操作数a,并将读取的操作数a存储在寄存器reg.a中(周期

①

)。然后,存储器内算术单元1101访问第三存储器存储体bank3以读取操作数b,并在读取的操作数b与存储在寄存器reg.a中的操作数a之间执行向量操作(乘法)(周期

②

)。也就是说,为了执行矩阵运算(或向量运算)(诸如,

mac算术运算),存储器内算术单元1101可以在两个周期期间在操作数之间执行算术运算。算术处理对应于在存储器内算术单元1101与存储器存储体1至存储器存储体4(例如,第一存储器存储体bank1至第四存储器存储体bank4)之间仅设置一个多路复用器(mux)的情况。然而,当在存储器内算术单元1101与存储器存储体1至存储器存储体4之间设置更多的多路复用器(mux)时,可以通过同时从不同的存储器存储体读取两个操作数来执行更高效的算术运算。在图11中,ina和inb表示乘法器(mul)和加法器(add)的分别输入操作数a和操作数b的端子,out表示乘法器(mul)的输出端子。

[0105]

图12是示出根据另一示例的在存储器裸片上的存储器内算术单元与存储器存储体之间的硬件连接的示图,并且图13示出了当通过使用图12中示出的存储器装置的硬件来执行算术运算时的时序图。

[0106]

参照图12,与先前参照图8所作的描述不同,两个多路复用器(mux)1241和1242被设置在存储器内算术单元1250与存储器存储体bank1到bank4之间。另外,存储体仲裁器1230包括独立地控制相应的多路复用器(mux)1241和1242的操作数a仲裁器1231和操作数b仲裁器1232。

[0107]

根据图13的时序图,在时钟信号bank clk的一个周期期间,存储体选择器1220通过第一端子1st和第二端子2nd向存储器存储体bank1至bank4提供用于使能所有存储器存储体bank1至bank4的控制信号bank selector_1st和bank selector_2nd。

[0108]

因为第一时钟信号clk divider_output的频率是时钟信号bank clk的频率的两倍,所以第一存储器存储体bank1的操作数a数据opd_a1、第二存储器存储体bank2的操作数a数据opd_a1、第三存储器存储体bank3的操作数b数据opd_b1和第四存储器存储体bank4的操作数b数据opd_b1都可以在第一时钟信号clk divider_output的两个周期期间被访问。这里,因为多路复用器(mux)1241和1242可以通过操作数a仲裁器1231和操作数b仲裁器1232基本同时访问存储器存储体bank1和bank2或者存储器存储体bank3和bank4,所以存储器内算术单元1250可以基本同时访问操作数a数据opd_a1、opd_a2、opd_a3或opd_a4以及操作数b数据opd_b1、opd_b2、opd_b3或opd_b4。因此,存储器内算术单元1250可以在存储器内算术单元1250的一个操作周期内执行操作数a与操作数b之间的算术运算。在图13中,operand a arbiter_output和operand b arbiter_output表示分别从操作数a仲裁器1231和操作数b仲裁器1232输出的信号。

[0109]

图14是示出通过使用参照图12描述的硬件实施方式对存储在不同存储器存储体中的不同操作数进行存储器内处理的示图。

[0110]

参照图14,当存储器内算术单元(alu1至alu4)中的每个的操作频率(2

×

250mhz)比存储器存储体(bank1至bank16)中的每个的操作频率(250mhz)大时,通过使用参照图12描述的并且其中提供了能够独立地访问存储器存储体bank1至bank16的多个多路复用器(mux)的硬件实施方式,可以在一个操作周期(即,存储器内算术单元alu1至alu4中的每个的1/(2

×

250mhz)=2ns)内执行存储在不同存储器存储体bank1至bank16中的不同操作数(操作数a和操作数b)之间的算术运算。

[0111]

图15是示出根据示例的包括存储器装置的计算系统的框图。执行上述存储器内处理的存储器装置可以作为ram 1520安装在计算系统1500(诸如,移动装置或台式计算机)中。根据上述示例的存储器装置中的任何一个可以应用于安装为ram 1520的存储器装置。

[0112]

具体地,执行存储器内处理并且被安装为ram 1520的存储器装置可以包括多个存储器内算术单元和多个存储器存储体,多个存储器内算术单元执行流水线化的算术运算的存储器内处理,多个存储器存储体以n个存储器存储体为单位被分配给每个存储器内算术单元,并且在流水线化的算术运算被执行时执行从每个存储器内算术单元请求的数据的访问操作。这里,每个存储器内算术单元可以以小于或等于存储器存储体中的每个的第二操作频率的n倍的第一操作频率操作。

[0113]

计算系统1500包括电连接到总线1550的中央处理器(cpu)1510、ram1520、用户接口1530和非易失性存储器1540。非易失性存储器1540可以包括大容量存储装置(诸如,固态驱动器(ssd)或硬盘驱动器(hdd))。

[0114]

当上述存储器装置(或存储器系统)应用于计算系统1500时,包括在ram 1520中的存储器装置可以执行存储器内处理。

[0115]

虽然本公开包括具体示例,但是在理解本技术的公开之后将清楚的是,在不脱离权利要求及其等同物的精神和范围的情况下,可以在这些示例中进行形式和细节上的各种改变。在此描述的示例将仅被认为是描述性的,而不是为了限制的目的。每个示例中的特征或方面的描述将被认为适用于其他示例中的类似特征或方面。如果描述的技术以不同的顺序执行,和/或如果描述的系统、架构、装置或电路中的组件以不同的方式组合,和/或由其他组件或其等同物替换或补充,则可以实现合适的结果。因此,公开的范围不是由具体实施方式限定,而是由权利要求及其等同物限定,并且在权利要求及其等同物的范围内的所有变化将被解释为包括在公开中。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1