一种闪存测试板及测试装置的制作方法

1.本技术涉及闪存测试技术领域,具体涉及一种闪存测试板及测试装置。

背景技术:

2.闪存的开发过程中,需要对闪存进行电流电压测试、老化测试、通断电测试等,以验证闪存的耐用性以及存储数据的持久性等。

3.相关技术中,对闪存的测试中,外部主机是通过一个接口与测试板进行连接,通过该接口,外部主机与测试板进行通信,以及数据的双向传输,对闪存进行数据的写入和读取的存储性能测试,外部主机根据写入和读取的数据判断闪存存储性能的好坏。整个测试过程,连接外部主机的接口需要进行通信指令和数据的双向传输,由于接口带宽的限制,导致能够同时测试的闪存数量较少,测试效率不高。

技术实现要素:

4.本技术实施例提供一种闪存测试板及测试装置,可以提高闪存测试的效率。

5.第一方面,本技术实施例提供一种闪存测试板,包括:

6.测试板本体;

7.第一接口,设置于所述测试板本体上,并与所述测试板本体电连接,用于连接外部主机,以使所述外部主机向所述测试板本体发送数据;

8.第二接口,设置于所述测试板本体上,并与所述测试板本体电连接,用于连接所述外部主机,以使所述外部主机与所述测试板本体之间进行通信指令传输;

9.多个测试接口,设置于所述测试板本体上,并与所述测试板本体电连接,用于与多个待测试闪存一一对应连接,以使所述测试板本体将接收的数据写入所述多个待测试闪存,并进行读取,以及所述测试板本体根据写入的数据和读取的数据向所述外部主机发送测试结果。

10.可选的,所述测试板本体包括:

11.hub芯片,与所述第一接口连接,用于接收所述外部主机发送的第一数据;

12.多个控制芯片,与所述hub芯片连接以及分别与所述多个测试接口一一对应连接,用于接收所述hub芯片发送的所述第一数据,并将所述第一数据一一写入所述多个待测试闪存。

13.可选的,所述第一接口还用于所述外部主机向所述hub芯片供电,以及用于所述外部主机通过所述hub芯片向所述多个控制芯片供电。

14.可选的,所述测试板本体还包括:

15.存储模块,用于存储所述第一数据;

16.处理芯片,分别与所述存储模块、所述第二接口以及与所述多个控制芯片连接,用于从所述存储模块获取所述第一数据,以及通过所述多个控制芯片从所述多个待测试闪存读取多个第二数据,并根据所述第一数据和所述第二数据向所述外部主机发送测试结果。

17.可选的,所述第二接口还用于所述外部主机向所述处理芯片供电,以及用于所述外部主机通过所述处理芯片向所述存储模块供电。

18.可选的,所述控制芯片还用于在向对应的待测试闪存写入所述第一数据后,向所述处理芯片发送第一读取指令;

19.所述处理芯片用于根据所述第一读取指令,通过相应的控制芯片从所述对应的待测试闪存读取所述第二数据。

20.可选的,所述处理芯片用于接收所述外部主机发送的第二读取指令,并根据所述第二读取指令通过所述多个控制芯片从所述多个待测试闪存读取多个所述第二数据。

21.可选的,所述控制芯片还用于当向对应的待测试闪存写入所述第一数据未完成,并且接收到所述处理芯片发送的第二读取指令时,向所述处理芯片发送延迟读取指令或者拒绝读取指令。

22.可选的,所述第一接口为usb type-c接口,和/或所述第二接口为usb type-a接口。

23.第二方面,本技术实施例提供一种测试装置,包括如上实施例所述的闪存测试板。

24.本技术实施例中,闪存测试板包括测试板本体、设置于测试板本体上并与测试板本体电连接的第一接口、第二接口和多个测试接口,外部主机通过第一接口向测试板本体发送数据,以及通过第二接口与测试板本体之间进行通信指令传输,每个测试接口均可以连接一个待测试闪存,测试板本体可以通过测试接口将接收的数据写入对应的待测试闪存,并从对应的待测试闪存中读取数据,以及根据写入的数据以及读取的数据向外部主机发送测试结果。整个测试过程中,外部主机与测试板本体之间,数据和通信指令是通过不同的接口进行传输的,并且外部主机通过第一接口只是单向向测试板本体发送数据,测试板从每一个待测试闪存中读取数据,并对读取的数据和写入的数据进行比较,将测试结果通过第二接口发送给外部主机,不用再将读取的数据通过第一接口发送回外部主机,大大减小了第一接口的数据传输量,从而外部主机通过本实施例的闪存测试板可以同时测试更多的待测试闪存,因此本技术实施例可以提高闪存测试的效率。

附图说明

25.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其有益效果显而易见。

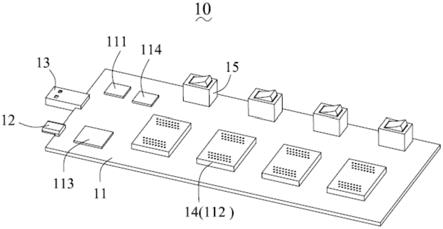

26.图1是本技术实施例提供的一种闪存测试板的结构示意图。

27.图2是本技术实施例提供的一种闪存测试板的应用场景示意图。

28.图3为本技术实施例提供的一种闪存测试板的工作原理图。

29.图4为本技术实施例提供的另一种闪存测试板的工作原理图。

具体实施方式

30.请参照图示,其中相同的组件符号代表相同的组件,本技术的原理是以实施在一适当的运算环境中来举例说明。以下的说明是基于所例示的本技术具体实施例,其不应被视为限制本技术未在此详述的其它具体实施例。

31.请参阅图1,图1是本技术实施例提供的一种闪存测试板的结构示意图,闪存测试

板10包括测试板本体11、第一接口12、第二接口13和多个测试接口14。其中,第一接口12设置在测试板本体11上,并与测试板本体11电连接,第二接口13设置在测试板本体11上,并与测试板本体11电连接,多个测试接口14设置在测试板本体11上,并与测试板本体11电连接。测试板本体11可以是pcb电路板。相关技术中,对闪存的测试中,外部主机是通过一个接口与测试板进行连接,通过该接口,外部主机与测试板进行通信,以及数据的双向传输,对闪存进行数据的写入和读取的存储性能测试,外部主机根据写入和读取的数据判断闪存存储性能的好坏。整个测试过程,连接主机的接口需要进行通信指令和数据的双向传输,由于接口带宽的限制,导致能够同时测试的闪存数量较少,测试效率不高。

32.本实施例中,请参阅图2,图2是本技术实施例提供的一种闪存测试板的应用场景示意图,第一接口12和第二接口13用于连接外部主机20,外部主机20通过第一接口12向测试板本体11发送数据,外部主机20还可以通过第二接口13与测试板本体11之间进行通信指令传输。测试接口14可以设置两个或者两个以上,每个测试接口14均可以连接一个待测试闪存30,测试板本体11可以通过测试接口14将接收的数据写入对应的待测试闪存30,测试板本体11还可以通过测试接口14从对应的待测试闪存30中读取数据;测试板本体11还可以根据向待测试闪存30写入的数据以及从待测试闪存30中读取的数据向外部主机20发送测试结果。

33.本实施例的闪存测试板10的工作原理为:外部主机20通过第一接口12向测试板本体11发送数据,测试板本体11将接收的数据通过每一个测试接口14分别写入对应的待测试闪存30,写入完成后并进行读取,然后将写入的数据与读取的数据进行比较。对于每一个待测试闪存30,测试板本体11将读取的数据与写入的数据进行比较,当读取的数据与写入的数据一致时,则通过第二接口13向外部主机20发送该待测试闪存30的存储性能正常的通信指令,当读取的数据与写入的数据不一致时,则通过第二接口13向外部主机20发送该待测试闪存30的存储性能异常的通信指令。

34.整个测试过程中,外部主机20与测试板本体11之间,数据和通信指令是通过不同的接口进行传输的,并且外部主机20通过第一接口12只是单向向测试板本体11发送数据,测试板本体11从每一个待测试闪存30中读取数据,并对读取的数据和写入的数据进行比较,将测试结果通过第二接口13发送给外部主机20,不用再将读取的数据通过第一接口12发送回外部主机20,大大减小了第一接口12的数据传输量,从而外部主机20通过本实施例的闪存测试板10可以同时测试更多的待测试闪存30,可以提高待测试闪存的测试效率。

35.在一实施例中,请参阅图1以及图3,图3为本技术实施例提供的一种闪存测试板的工作原理图,该闪存测试板10的测试板本体11包括:hub芯片111、多个控制芯片112、处理芯片113和存储模块114。hub芯片111与第一接口12连接,用于接收外部主机20发送的第一数据(data0),可以理解的是,第一数据为测试待测试闪存所用的原始数据。每一个控制芯片112与hub芯片111连接,还与测试接口14一一对应连接,hub芯片111将接收的第一数据分别发送给每一个控制芯片112,每一个控制芯片112将第一数据写入对应的待测试闪存30中。存储模块114可以是一存储卡,例如sd卡,测试板本体11上设置相应的卡槽即可。存储模块114中存储有第一数据,可以预先将第一数据拷贝至存储模块114中。处理芯片113分别与存储模块114、第二接口13以及与所有控制芯片112连接,处理芯片113可以从存储模块114获取第一数据,无需从外部主机20获取,效率更高。处理芯片113还可以通过控制芯片112从对

应的待测试闪存30读取第二数据(如图中的data1/data2/data3/data4),然后根据第一数据和第二数据向外部主机20发送测试结果(result)。

36.作为一种实现方式,如图3所示,外部主机20通过第一接口12向hub芯片111发送第一数据,hub芯片111将第一数据分发给每个控制芯片112,每个控制芯片112再将第一数据写入对应的待测试闪存30。对于任一控制芯片112,当该控制芯片112在向对应的待测试闪存30写入第一数据后,可以主动向处理芯片113发送第一读取指令(cmd1)。处理芯片113根据第一读取指令,通过该控制芯片112从对应的待测试闪存30读取第二数据,同时处理芯片113还从存储模块114中获取第一数据,将第二数据与第一数据进行比较,若第二数据与第一数据一致,则判断该待测试闪存30存储性能正常,若第二数据与第一数据不一致,则判断该待测试闪存30存储性能异常,最后处理芯片113将测试结果通过第二接口13发送给外部主机20。

37.本实施方式中,对于任一控制芯片112,当该控制芯片112在向对应的待测试闪存30写入第一数据后,可以主动向处理芯片113发送第一读取指令,从而可以避免在待测试闪存30中未写完第一数据时处理芯片113发送数据读取请求,进而读取失败,避免浪费有限的处理资源。

38.作为另一种实现方式,请参阅图4,图4为本技术实施例提供的另一种闪存测试板的工作原理图,外部主机20通过第一接口12向hub芯片111发送第一数据,hub芯片111将第一数据分发给每个控制芯片112,每个控制芯片112再将第一数据写入对应的待测试闪存30。外部主机20还通过第二接口13向处理芯片113发送第二读取指令(cmd2),处理芯片113接收到第二读取指令后,通过控制芯片112从相应的待测试闪存30读取第二数据(data1/data2/data3/data4)。同时处理芯片113还从存储模块114中获取第一数据,将第二数据与第一数据进行比较,若第二数据与第一数据一致,则判断该待测试闪存30存储性能正常,若第二数据与第一数据不一致,则判断该待测试闪存30存储性能异常,最后处理芯片113将测试结果(result)通过第二接口13发送给外部主机20。可以理解的是,若处理芯片113向某个控制芯片112发送第二读取指令,且该控制芯片112向对应的待测试闪存30写入第一数据未完成时,则该控制芯片112向处理芯片113发送延迟读取指令或者拒绝读取指令。

39.本实施方式中,第二数据的读取指令可以由外部主机20进行发送。这样,外部主机20可以根据每个测试接口14的测试情况进行第二读取指令的发送。例如,外部主机20最新接收到的是图4中左边的两个测试接口14的测试结果,则可以发送对右边的测试接口14的待测试闪存进行数据读取的第二读取指令,从而避免频繁对某个测试接口14发起第二数据读取请求,从而避免该测试接口14对应的待测试闪存由于未写完第一数据,造成第二读取指令排队或者读取第二数据失败。

40.在一个实施例中,第一接口12还用于外部主机20向hub芯片111供电(power1),以及用于外部主机20通过hub芯片111向所有控制芯片112供电(power2)。作为一个示例,测试接口14可以是usb接口、pci-e接口或sata接口,由于上述接口的工作功耗基本都高于2w,因此,第一接口12可以是usb type-c接口,不仅可以为hub芯片111供电,还可以为多个控制芯片112和待测试闪存30的芯片组合提供足够的功耗,同时可以兼容usb3.2gen2或usb3.2 gen2*2的传输协议,实现数据在外部主机20与闪存测试板10之间进行快速传输。

41.在一个实施例中,第二接口13还用于外部主机20向处理芯片113供电(power3),以

及用于外部主机20通过处理芯片113向存储模块114供电(power4)。由于第二接口13仅为处理芯片113和存储模块114供电,以及仅传输控制命令和测试结果,只需要较低的功耗和传输速度,作为一个示例,第二接口13可以是usb type-a接口。

42.在一个实施例中,请参阅图1,闪存测试板10还包括多个开关15。开关15的数量与控制芯片112的数量相同,并一一对应连接,用于控制hub芯片111给控制芯片112供电,即每个测试开关15单独控制给对应的一个控制芯片112供电,从而可以对每个测试接口14是否开启测试功能进行单独控制。

43.本技术实施例还提供一种测试装置,该测试装置包括至少一个闪存测试板,该闪存测试板为上述任一实施例中的闪存测试板,用于连接待测试闪存,本测试装置通过控制闪存测试板对待测试闪存的存储性能进行测试。该测试装置的测试原理与上文实施例中的闪存测试板属于同一构思,此处不再赘述。

44.以上对本技术实施例所提供的一种测试板及测试装置进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的方法及其核心思想;同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1