一种应用于内存模组的内存芯片补位方法与流程

1.本发明涉及内存模组,更确切地说是一种应用于内存模组的内存芯片补位方法。

背景技术:

2.内存条通常包括有电路板和设置于电路板上的若干个内存芯片,电路板的底端设置有内存芯片电连接的金手指,使用时将金手指插于电脑主板的内存插槽中。内存芯片在生产或使用的过程中,会产生一些不良品,对于不良的内存芯片很难通过维修的方法进行修复,因此,通常只能丢弃或作为废物回收,造成了资源的浪费。

技术实现要素:

3.本发明为了解决现有技术对不良的内存芯片只能丢弃或作为废物回收,造成资源的浪费的技术问题,提供了一种应用于内存模组的内存芯片补位方法。

4.为解决上述技术问题,本发明采用的技术方案为设计一种应用于内存模组的内存芯片补位方法,包括:

5.根据16位不良单晶内存芯片的不良区域和正常区域,将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组;

6.根据8位不良单晶内存芯片的不良区域和正常区域,将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组;

7.依据jedec定义的规则,选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线,利用所述16位不良单晶内存芯片和所述8位不良单晶内存芯片组合实现一个16位正常单晶内存芯片的功能。

8.所述将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组包括:

9.将所述地址线的0-7位分为a组,8-15位分为b组;若所述不良区域位于a组,则选择a组作为所述第一不良组,b组作为所述第一正常组;若所述不良区域位于b组,则选择a组作为所述第一正常组,b组作为所述第一不良组。

10.所述a组和b组至少有一个不包含所述不良区域。

11.所述将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组包括:

12.将所述8位不良单晶内存芯片的位址线按照bg1=0分为d组,bg1=1分为e组;若所述不良区域位于d组,则选择d组作为第二不良组,e组作为第二正常组;所述不良区域位于e组,则选择d组作为第二正常组,e组作为第二不良组。

13.所述d组和e组至少有一个不包含所述不良区域。

14.所述应用于内存模组的内存芯片补位方法还包括:

15.对所述16位不良单晶内存芯片和8位不良单晶内存芯片进行检测,获取所述不良区域和所述正常区域。

16.所述选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线包括:

17.将所述8位不良单晶内存芯片的各功能球位依序连接到所述16位不良单晶内存芯片的相同功能球位,再连接到内存条的功能针脚。

18.所述选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线还包括:

19.将所述8位不良单晶内存芯片的bg1球位串联后,做跳线回路,当所述e组为第二正常组时,将所述bg1球位与电源连接;当所述d组为第二正常组时,将所述bg1球位与地连接。

20.所述bg1球位与电源通过零欧姆电阻连接;所述bg1球位与地通过零欧姆电阻连接。

21.本发明通过根据16位不良单晶内存芯片的不良区域和正常区域,将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组;根据8位不良单晶内存芯片的不良区域和正常区域,将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组;然后再依据jedec定义的规则,选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线,利用所述16位不良单晶内存芯片和所述8位不良单晶内存芯片组合实现一个16位正常单晶内存芯片的功能,从而可用1个16位不良单晶内存芯片和1个8位不良单晶内存芯片实现一个16位正常单晶内存芯片的功能,很好的利用了不良内存芯片,实现了废物利用,避免了浪费。

附图说明

22.下面结合实施例和附图对本发明进行详细说明,其中:

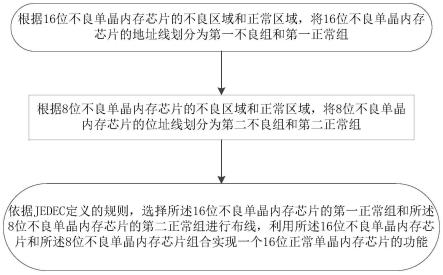

23.图1是本发明应用于内存模组的内存芯片补位方法的原理图。

具体实施方式

24.下面结合附图进一步阐述本发明的具体实施方式:

25.请一并参见图1。本发明应用于内存模组的内存芯片补位方法包括:

26.第一步:根据16位不良单晶内存芯片的不良区域和正常区域,将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组;

27.根据8位不良单晶内存芯片的不良区域和正常区域,将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组。

28.在本具体实施例中,所述将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组包括:将所述地址线的0-7位分为a组,8-15位分为b组;若所述不良区域位于a组,则选择a组作为所述第一不良组,b组作为所述第一正常组;若所述不良区域位于b组,则选择a组作为所述第一正常组,b组作为所述第一不良组。

29.比如,当地址线的4、5、6位损坏,为不良区域,8-15位未损坏,为正常区域时,则取第8-15位作为第一正常组加以利用。当地址线的第8、10、11、13位损坏,为不良区域时,0-7位未损坏,为正常区域时,则取第0-7位作为第一正常组加以利用。

30.为便于分组及布线,所述a组和b组至少有一个不包含所述不良区域。当a组和b组都包含不良区域时,该16位不良单晶内存芯片只能废弃。例如,当地址线的4、7、9位损坏时,该内存芯片则只能废弃,不能再利用。

31.所述将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组包括:将

所述8位不良单晶内存芯片的位址线按照bg1=0分为d组,bg1=1分为e组;若所述不良区域位于d组,则选择d组作为第二不良组,e组作为第二正常组;所述不良区域位于e组,则选择d组作为第二正常组,e组作为第二不良组。

32.所述d组和e组至少有一个不包含所述不良区域。

33.在对所述16位不良单晶内存芯片和8位单晶内存芯片进行分组之前,所述应用于内存模组的内存芯片补位方法还包括:

34.对所述16位不良单晶内存芯片和8位不良单晶内存芯片进行检测,获取所述不良区域和所述正常区域。

35.测试可采用内存测试工具rst、mem test来实现,当然,也可以自动开发测试软件来实现。测试完后,可将相同不良区域的内存芯片进行归类分开放置,以便于后续的分组及组合。

36.第二步:依据jedec定义的规则,选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线,利用所述16位不良单晶内存芯片和所述8位不良单晶内存芯片组合实现一个16位正常单晶内存芯片的功能。

37.jedec(joint electron device engineering council,联合电子器件工程委员会)对内存芯片的布线制定了详细的标准规则,因此,本发明将述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线时,只需要依据jedec定义的规则进行布线即可。

38.在本具体实施例中,所述选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线包括:

39.将所述8位不良单晶内存芯片的各功能球位依序连接到所述16位不良单晶内存芯片的相同功能球位,再连接到内存条的功能针脚。

40.功能球位即封装好的芯片的管脚,用来连接芯片与电路板,与内存条背面位于内存芯片处的各焊接点对应。功能针脚对应内存条的金手指。

41.所述选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线还包括:

42.将所述8位不良单晶内存芯片的bg1球位串联后,做跳线回路,当所述e组为第二正常组时,将所述bg1球位与电源连接;当所述d组为第二正常组时,将所述bg1球位与地连接。

43.在本具体实施例中,所述bg1球位与电源通过零欧姆电阻连接;所述bg1球位与地通过零欧姆电阻连接。

44.本发明通过根据16位不良单晶内存芯片的不良区域和正常区域,将16位不良单晶内存芯片的地址线划分为第一不良组和第一正常组;根据8位不良单晶内存芯片的不良区域和正常区域,将8位不良单晶内存芯片的位址线划分为第二不良组和第二正常组;然后再依据jedec定义的规则,选择所述16位不良单晶内存芯片的第一正常组和所述8位不良单晶内存芯片的第二正常组进行布线,利用所述16位不良单晶内存芯片和所述8位不良单晶内存芯片组合实现一个16位正常单晶内存芯片的功能,从而可用1个16位不良单晶内存芯片和1个8位不良单晶内存芯片实现一个16位正常单晶内存芯片的功能,很好的利用了不良内存芯片,实现了废物利用,避免了浪费。

45.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精

神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1