窄台面绝缘栅双极型晶体管器件及形成方法与流程

1.本发明涉及半导体集成电路制造领域,特别是涉及一种窄台面绝缘栅双极型晶体管器件及形成方法。

背景技术:

2.在绝缘栅双极型晶体管(igbt)构成的功率器件中,导通电阻(r

on

)以及击穿电压(bv)是衡量功率器件开关性能的重要参数。如何在维持器件具有较高击穿电压的同时,获得较低的导通电阻是业界所关注的研究重点。

3.目前,为了有效地降低igbt的导通电阻,在沟槽栅型igbt器件中已引入了一种窄台面(narrow mesa)器件结构。在上述窄台面igbt器件中,沟槽栅之间的台面(mesa)宽度一般约为器件反型层(inversion layer)厚度的两倍,例如20~40nm。通过在窄台面区域增强电子密度和注入效率(injection efficiency),以降低器件的导通电阻。

4.然而,在现有的窄台面igbt器件中,由于电子和空穴在基区的电导调制作用,导致产生集电极致势垒降低(cibl,collector induced barrier lowering)效应的问题。cibl效应将会导致器件饱和电流增大,进而导致igbt器件抗短路能力弱化,这将严重影响igbt的器件性能。针对上述缺陷,业界已提出了多种igbt器件结构的改进方案,以试图抑制窄台面igbt器件中的cibl效应,但上述改进方案所提供的igbt器件结构还都无法彻底消除cibl效应。这将大幅限制窄台面igbt器件的应用。

5.因此,有必要提出一种新的窄台面绝缘栅双极型晶体管器件及形成方法,解决上述问题。

技术实现要素:

6.鉴于以上所述现有技术的缺点,本发明的目的在于提供一种窄台面绝缘栅双极型晶体管器件及形成方法,用于解决现有技术中窄台面(narrow mesa)绝缘栅双极型晶体管(igbt)器件中存在的集电极致势垒降低(cibl)的问题。

7.为实现上述目的及其它相关目的,本发明提供了一种窄台面绝缘栅双极型晶体管器件,其特征在于,包括:

8.半导体衬底;

9.形成于所述半导体衬底正面并沿水平方向间隔排列的栅极沟槽结构和发射极沟槽结构;所述栅极沟槽结构和所述发射极沟槽结构在排列方向上各自成对设置,且成对的所述栅极沟槽结构与成对的所述发射极沟槽结构在排列方向上相互交叠设置;

10.形成于成对的所述发射极沟槽结构之间的阱区;

11.形成于成对的所述栅极沟槽结构之间以及成对的所述发射极沟槽结构之间的发射极注入区;在成对的所述发射极沟槽结构之间的区域中,所述发射极注入区位于所述阱区上方。

12.作为本发明的一种可选方案,所述窄台面绝缘栅双极型晶体管器件还包括形成于

相邻的栅极沟槽结构和发射极沟槽结构之间的所述半导体衬底中的虚设掺杂区。

13.作为本发明的一种可选方案,所述窄台面绝缘栅双极型晶体管器件还包括形成于相邻的栅极沟槽结构和发射极沟槽结构之间的所述半导体衬底上方的隔离层。

14.作为本发明的一种可选方案,所述窄台面绝缘栅双极型晶体管器件还包括形成于所述半导体衬底上方的发射极金属层,以及形成于所述半导体衬底背面的背面注入层和集电极金属层。

15.作为本发明的一种可选方案,所述栅极沟槽结构和所述发射极沟槽结构包括多晶硅层和形成于所述多晶硅层和所述半导体衬底之间的栅极氧化层。

16.作为本发明的一种可选方案,形成所述多晶硅层的材料包括掺杂多晶硅。

17.作为本发明的一种可选方案,所述栅极沟槽结构和所述发射极沟槽结构包括栅极金属层和形成于所述栅极金属层和所述半导体衬底之间的栅极氧化层。

18.作为本发明的一种可选方案,所述栅极金属层包括导电金属层和形成于所述导电金属层和所述栅极氧化层之间的功函数金属层。

19.作为本发明的一种可选方案,成对的所述发射极沟槽结构之间的间距大于成对的所述栅极沟槽结构之间的间距。

20.本发明还提供了一种窄台面绝缘栅双极型晶体管器件的形成方法,其特征在于,包括如下步骤:

21.1)提供半导体衬底;

22.2)在所述半导体衬底正面形成沿水平方向间隔排列的栅极沟槽结构和发射极沟槽结构;所述栅极沟槽结构和所述发射极沟槽结构在排列方向上各自成对设置,且成对的所述栅极沟槽结构与成对的所述发射极沟槽结构在排列方向上相互交叠设置;

23.3)在成对的所述发射极沟槽结构之间形成阱区;

24.4)在成对的所述栅极沟槽结构之间以及成对的所述发射极沟槽结构之间形成发射极注入区;在成对的所述发射极沟槽结构之间的区域中,所述发射极注入区位于所述阱区上方。

25.作为本发明的一种可选方案,在步骤2)中,还包括在相邻的栅极沟槽结构和发射极沟槽结构之间的所述半导体衬底中形成虚设掺杂区的步骤。

26.作为本发明的一种可选方案,在步骤2)中,还包括在相邻的栅极沟槽结构和发射极沟槽结构之间的所述半导体衬底上方形成隔离层的步骤。

27.作为本发明的一种可选方案,在步骤4)后,还包括在所述半导体衬底上方形成发射极金属层,以及在所述半导体衬底背面形成背面注入层和集电极金属层的步骤。

28.如上所述,本发明提供一种窄台面绝缘栅双极型晶体管器件及形成方法,具有以下有益效果:

29.本发明引入了一种新的窄台面绝缘栅双极型晶体管器件及形成方法,在主动台面区不设置p型掺杂区,而在非主动台面区中形成p型掺杂区以及位于p型掺杂区上方的n+型掺杂区,不但通过引入窄台面区增强电子注入,获得了较低的器件导通电阻,也通过减少窄台面区的空穴浓度,增强了器件抗短路能力,消除了cibl效应。

附图说明

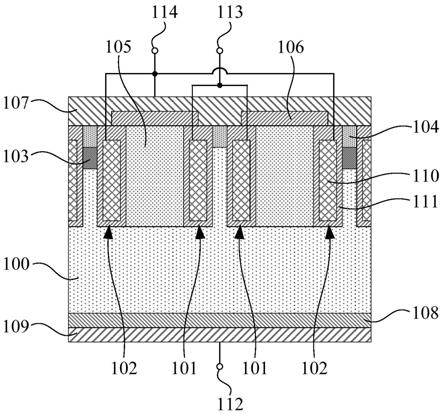

30.图1显示为本发明实施例一中提供的窄台面绝缘栅双极型晶体管器件的截面示意图。

31.图2显示为本发明实施例一中提供的窄台面绝缘栅双极型晶体管器件的一个单元结构的截面示意图。

32.图3显示为本发明实施例一中提供的窄台面绝缘栅双极型晶体管器件的一个单元结构的截面示意图。

33.图4显示为本发明实施例二中在半导体衬底上形成硬掩膜层后的截面示意图。

34.图5显示为本发明实施例二中沟槽刻蚀后的截面示意图。

35.图6显示为本发明实施例二中形成栅极沟槽结构和发射极沟槽后的截面示意图。

36.图7显示为本发明实施例二中通过离子注入形成阱区的截面示意图。

37.图8显示为本发明实施例二中通过离子注入形成发射极注入区的截面示意图。

38.图9显示为本发明实施例二中形成发射极金属层、背面注入层和集电极金属层后的截面示意图。

39.元件标号说明

40.100

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

半导体衬底

41.100a

ꢀꢀꢀꢀꢀꢀꢀꢀ

硬掩膜层

42.101

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极沟槽结构

43.101a

ꢀꢀꢀꢀꢀꢀꢀꢀ

栅极沟槽

44.102

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发射极沟槽结构

45.102a

ꢀꢀꢀꢀꢀꢀꢀꢀ

发射极沟槽

46.103

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

阱区

47.103a

ꢀꢀꢀꢀꢀꢀꢀꢀ

第一光刻胶层

48.104

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发射极注入区

49.104a

ꢀꢀꢀꢀꢀꢀꢀꢀ

第二光刻胶层

50.105

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

虚设掺杂区

51.106

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

隔离层

52.107

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发射极金属层

53.108

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

背面注入层

54.109

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

集电极金属层

55.110

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极材料层

56.111

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极氧化层

57.112

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

集电极

58.113

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

栅极

59.114

ꢀꢀꢀꢀꢀꢀꢀꢀꢀ

发射极

具体实施方式

60.以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其它优点与功效。本发明还可以通过另外不同的具体实

施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

61.请参阅图1至图9。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

62.实施例一

63.请参阅图1至图3,本实施例提供了一种窄台面绝缘栅双极型晶体管器件,其特征在于,包括:

64.半导体衬底100;

65.形成于所述半导体衬底100正面并沿水平方向间隔排列的栅极沟槽结构101和发射极沟槽结构102;所述栅极沟槽结构101和所述发射极沟槽结构102在排列方向上各自成对设置,且成对的所述栅极沟槽结构101与成对的所述发射极沟槽结构102在排列方向上相互交叠设置;

66.形成于成对的所述发射极沟槽结构102之间的阱区103;

67.形成于成对的所述栅极沟槽结构101之间以及成对的所述发射极沟槽结构102之间的发射极注入区104;在成对的所述发射极沟槽结构102之间的区域中,所述发射极注入区104位于所述阱区103上方。

68.作为示例,如图1所示,所述半导体衬底100可以是n-型掺杂半导体材料层,所述半导体材料层可以由硅(si)、锗硅(sige)、氮化镓(gan)或碳化硅(sic)等半导体材料构成。可选地,对于穿通型igbt器件,在n-型掺杂半导体材料层下方还形成有图1中未展示的n+型掺杂缓冲层。

69.作为示例,如图1所示,在所述半导体衬底100的正面形成有沿水平方向间隔排列的栅极沟槽结构101和发射极沟槽结构102。所述栅极沟槽结构101和所述发射极沟槽结构102在排列方向上各自成对设置,且成对的所述栅极沟槽结构101与成对的所述发射极沟槽结构102在排列方向上相互交叠设置。在图1中,位于中央区域的是一对所述栅极沟槽结构101,而其左右两侧分别设有一对所述发射极沟槽结构102,在平行于图1中截面的水平方向上,成对的所述栅极沟槽结构101与所述发射极沟槽结构102相互交叠设置,即在左右两侧的成对所述发射极沟槽结构102的左右外侧,还设有图1中未展示的成对的所述栅极沟槽结构101。即是说,本发明所提供的窄台面绝缘栅双极型晶体管器件具有由两个栅极(gate)与两个发射极(emitter)重复排列构成的ggee型器件结构。

70.作为示例,如图1所示,所述窄台面绝缘栅双极型晶体管器件还包括形成于相邻的栅极沟槽结构101和发射极沟槽结构102之间的所述半导体衬底100中的虚设掺杂区105。可选地,所述虚设掺杂区105为浮置p型掺杂区(floating p-dummy),通过在所述半导体衬底100表面进行离子注入形成。所述虚设掺杂区105所占区域的跨度可以根据器件设计需要进行调整,使器件区域中窄台面区的密度处于最佳水平。

71.作为示例,如图2所示,是本发明所提供的窄台面绝缘栅双极型晶体管器件的一个单元结构。在一个单元结构中,其单元节距(cell pitch)从左右两侧的完整的发射极沟槽结构102附近起算,包括栅极沟槽结构101两侧的虚设掺杂区105、成对的所述栅极沟槽结构

101之间的一个主动台面区(active mesa),以及成对的所述发射极沟槽结构102之间的一个非主动台面区(inactive mesa)。其中,单元结构的非主动台面区是与左右相邻单元结构各共有一个,从左右各划入半个,并合并计算为一个。

72.作为示例,如图3所示,在本发明的另一个实施案例中,在成对的所述发射极沟槽结构102之间的非主动台面区的间距宽度d1可以设置为大于在成对的所述栅极沟槽结构101之间的主动台面区的间距宽度d2。这是由于非主动台面区在器件中的功能仅在于在器件导通时收集空穴,并在器件关断时处于耗尽状态,而无需如同主动台面区那样设为窄台面结构。在图3中所指的窄台面(narrow mesa)是基于主动台面区的宽度d2,所述宽度d2的宽度约为器件反型层(inversion layer)厚度的两倍,例如设为20~40nm。本发明通过引入窄台面区能够增强电子注入,从而获得较低的器件导通电阻。

73.作为示例,在本实施例中,所述栅极沟槽结构101和所述发射极沟槽结构102具有相同的工艺结构并由相同的材料构成。如图1所示,所述栅极沟槽结构101和所述发射极沟槽结构102包括栅极材料层110以及形成于所述栅极材料层110和所述半导体衬底100之间的栅极氧化层111。形成所述栅极材料层110的材料可以根据器件设计进行选择。

74.例如,在本发明的一个实施案例中,所述栅极材料层110包括多晶硅层。可选地,形成所述多晶硅层的材料包括掺杂多晶硅,以改善多晶硅材料的导电性能。具体地,所述掺杂多晶硅包括硼掺杂多晶硅。而在本发明的其他实施案例中,所述栅极材料层110还可以包括由金属或金属化合物等材料构成的栅极金属层。可选地,所述栅极金属层包括导电金属层和形成于所述导电金属层和所述栅极氧化层111之间的功函数金属层。具体地,所述导电金属层包括钨金属层;所述功函数金属层由p型功函数金属构成,可以包括氮化钛层或氮化钨层。所述功函数金属层也可以根据器件设计所需的功函数选择其他功函数金属材料。所述栅极结构的设置需要使主动台面区在栅极接地或接负偏压时使器件关断,并在接正偏压时积蓄电子。

75.在本发明的其他实施案例中,所述栅极沟槽结构101和所述发射极沟槽结构102也可以具有不同结构,并由不同材料在不同的工艺步骤中分别形成。可选地,本发明中形成的栅极结构还可以包括分离栅结构,以降低源漏密勒电容。所述分离栅结构位于栅极材料层的下方,连接源极或浮置,并通过隔离介质层与栅极材料层进行隔离。

76.作为示例,如图1所示,所述窄台面绝缘栅双极型晶体管器件还包括形成于成对的所述发射极沟槽结构102之间的阱区103,以及形成于成对的所述栅极沟槽结构101之间以及成对的所述发射极沟槽结构102之间的发射极注入区104。可选地,所述阱区103是由p型注入在所述半导体衬底100中形成的掺杂区,例如,通过硼注入形成。所述发射极注入区104是由n+型注入在所述半导体衬底100中形成的掺杂区,例如,通过砷注入形成。如图1所示,在成对的所述发射极沟槽结构102之间的区域中,所述发射极注入区104位于所述阱区103上方。

77.作为示例,如图1所示,所述窄台面绝缘栅双极型晶体管器件还包括形成于相邻的栅极沟槽结构101和发射极沟槽结构102之间的所述半导体衬底100上方的隔离层106。所述隔离层106可以由二氧化硅化学气相沉积工艺形成。通过所述隔离层106可以隔离所述发射极金属层107与所述虚设掺杂区105。

78.作为示例,如图1所示,所述窄台面绝缘栅双极型晶体管器件还包括形成于所述半

导体衬底100上方的发射极金属层107,以及形成于所述半导体衬底100背面的背面注入层108和集电极金属层109。可选地,igbt器件的背面工艺流程包括背面减薄、注入和金属化等工艺,以形成所述背面注入层108和所述集电极金属层109,所述背面注入层108为p型注入层。

79.作为示例,如图2所示,在本发明提供的窄台面绝缘栅双极型晶体管器件的一个单元结构中,所述集电极金属层109引出为器件的集电极112;所述栅极沟槽结构101引出为器件的栅极113;所述发射极沟槽结构102连接所述发射极金属层107,并引出为器件对的发射极114。上述器件结构由两个栅极(gate)与两个发射极(emitter)重复排列形成,并构成了ggee型器件结构。在本发明的其他实施案例中,所述发射极沟槽结构102也可以不连接所述发射极金属层107,而在器件工作时施加负偏压。

80.在本实施例中,所述半导体衬底100上方直接形成了所述发射极金属层107,以引出器件的发射极。而在本发明的其他实施案例中,还可以根据器件设计需要,在所述半导体衬底100上方先形成层间介质层和位于所述层间介质层中的接触孔结构,并由所述接触孔结构进一步电性连接上层的金属互连结构,以引出发射极。所述金属互连结构可以通过光刻和刻蚀定义图形化结构,并在其上覆盖钝化保护层。可选地,所述金属互连结构还可以是多层,通过通孔结构连接,并通过层间金属层隔离,以满足复杂器件的布线设计需求。

81.在本实施例所提供的窄台面绝缘栅双极型晶体管器件中,成对的所述栅极沟槽结构101之间的主动台面区(active mesa)中不设置p型掺杂区,即阱区103,而成对的所述发射极沟槽结构102之间的非主动台面区(inactive mesa)中则形成有p型掺杂区以及位于p型掺杂区上方的n+型掺杂区。在器件导通时,电子积聚在主动台面区,降低了器件的导通电阻r

on

,主动台面区具有的空穴数量占极少数,这消除了cibl效应,增强了器件的抗短路能力;而在器件关断时,主动台面区和非主动台面区都处于耗尽状态,呈现闭锁电压。本发明所提供的新型的窄台面绝缘栅双极型晶体管结构能够通过引入窄台面区增强电子注入,获得了较低的器件导通电阻r

on

;也通过减少窄台面区的空穴浓度,增强了抗短路能力,消除了cibl效应。

82.实施例二

83.请参阅图4至图9,本实施例提供了一种窄台面绝缘栅双极型晶体管器件的形成方法,其特征在于,包括如下步骤:

84.1)提供半导体衬底100;

85.2)在所述半导体衬底100正面形成沿水平方向间隔排列的栅极沟槽结构101和发射极沟槽结构102;所述栅极沟槽结构101和所述发射极沟槽结构102在排列方向上各自成对设置,且成对的所述栅极沟槽结构101与成对的所述发射极沟槽结构102在排列方向上相互交叠设置;

86.3)在成对的所述发射极沟槽结构102之间形成阱区103;

87.4)在成对的所述栅极沟槽结构101之间以及成对的所述发射极沟槽结构102之间形成发射极注入区104;在成对的所述发射极沟槽结构102之间的区域中,所述发射极注入区104位于所述阱区103上方。

88.在步骤1)中,请参阅图4,提供半导体衬底100。

89.作为示例,如图4所示,所述半导体衬底100可以是n-型掺杂半导体材料层,所述半

导体材料层可以由硅(si)、锗硅(sige)、氮化镓(gan)或碳化硅(sic)等半导体材料构成。可选地,n-型掺杂半导体材料层也可以是通过在衬底上外延生长得到的外延材料层。对于穿通型igbt器件,在n-型掺杂半导体材料层下方还形成有n+型掺杂缓冲层。

90.在步骤2)中,请参阅图4至图6,在所述半导体衬底100正面形成沿水平方向间隔排列的栅极沟槽结构101和发射极沟槽结构102;所述栅极沟槽结构101和所述发射极沟槽结构102在排列方向上各自成对设置,且成对的所述栅极沟槽结构101与成对的所述发射极沟槽结构102在排列方向上相互交叠设置。

91.如图4所示,通过硬掩膜材料沉积、光刻和刻蚀工艺在所述半导体衬底100正面形成图形化的硬掩膜层100a,作为后续刻蚀工艺的刻蚀掩膜,通过硬掩膜层的图形定义沟槽结构的图形。

92.如图5所示,以所述硬掩膜层100a作为刻蚀掩膜,通过沟槽干法刻蚀形成栅极沟槽101a和发射极沟槽102a。在本实施例中,所述栅极沟槽101a和所述发射极沟槽102a的特征尺寸(cd)和刻蚀深度相同。在图5中,一对所述栅极沟槽101a位于中央区域,而所述发射极沟槽102a则位于左右两侧区域。在本发明的其他实施案例中,所述栅极沟槽101a和所述发射极沟槽102a也可以具有不同的特征尺寸(cd)和刻蚀深度。可选地,对于含硅的所述半导体衬底100,可以采用sf6或hbr等作为刻蚀气体源进行各向异性的干法刻蚀。在刻蚀完成后可以通过湿法刻蚀等方法去除所述硬掩膜层100a。

93.在本实施例中,所述干法刻蚀以所述硬掩膜层100a作为刻蚀掩膜,这是由于硬掩膜的刻蚀选择比高且保形性好。而在本发明的其他实施案例中,所述干法刻蚀也可以直接以光刻胶层作为刻蚀掩膜。

94.如图6所示,在所述栅极沟槽101a和所述发射极沟槽102a中形成栅极氧化层111和栅极材料层110,以分别形成栅极沟槽结构101和发射极沟槽结构102。

95.例如,在本发明的一个实施案例中,所述栅极材料层110包括多晶硅层。可选地,形成所述多晶硅层的材料包括掺杂多晶硅,以改善多晶硅材料的导电性能。具体地,所述掺杂多晶硅包括硼掺杂多晶硅。而在本发明的其他实施案例中,所述栅极材料层110还可以包括由金属或金属化合物等材料构成的栅极金属层。可选地,所述栅极金属层包括导电金属层和形成于所述导电金属层和所述栅极氧化层111之间的功函数金属层。具体地,所述导电金属层包括钨金属层;所述功函数金属层由p型功函数金属构成,可以包括氮化钛层或氮化钨层。所述功函数金属层也可以根据器件设计所需的功函数选择其他功函数金属材料。所述栅极氧化层111可以在所述半导体衬底100通过热氧化生长热氧化层得到。在形成所述栅极材料层110后,还在其顶部覆盖二氧化硅层,并与所述栅极氧化层111一体地包裹所述栅极材料层110。

96.作为示例,如图6所示,在相邻的栅极沟槽结构101和发射极沟槽结构102之间的所述半导体衬底100中还形成虚设掺杂区105。可选地,所述虚设掺杂区105为p型掺杂,通过在所述半导体衬底100表面进行离子注入形成。所述虚设掺杂区105所占区域的跨度可以根据器件设计需要进行调整,使器件区域中窄台面区的密度处于最佳水平。

97.作为示例,如图6所示,在形成虚设掺杂区105后,还在相邻的栅极沟槽结构101和发射极沟槽结构102之间的所述半导体衬底100上方形成隔离层106。所述隔离层106可以由二氧化硅化学气相沉积工艺形成。通过所述隔离层106可以隔离所述发射极金属层107与所

述虚设掺杂区105。

98.在步骤3)中,请参阅图7,在成对的所述发射极沟槽结构102之间形成阱区103。在图7中,通过第一光刻胶层103a覆盖器件上其他不需要进行离子注入的区域,对成对的所述发射极沟槽结构102之间的区域进行离子注入,以形成所述阱区103。图中箭头标示了离子注入的施加区域。可选地,所述阱区103是由p型注入在所述半导体衬底100中形成的掺杂区,例如,通过硼注入形成。需要指出的是,所述第一光刻胶层103a通过涂覆光刻胶后经过光刻曝光形成,主要保护其他非注入区域不受注入影响,如果其他区域上已有氧化层等覆盖保护,则这些区域上也可不额外覆盖光刻胶层。在离子注入完成后,去除残留的光刻胶层,并对注入离子进行退火激活等工艺。

99.在步骤4)中,请参阅图8,在成对的所述栅极沟槽结构101之间以及成对的所述发射极沟槽结构102之间形成发射极注入区104;在成对的所述发射极沟槽结构102之间的区域中,所述发射极注入区104位于所述阱区103上方。在图8中,通过第二光刻胶层104a覆盖器件上其他不需要进行离子注入的区域,在成对的所述栅极沟槽结构101之间以及成对的所述发射极沟槽结构102之间的区域进行离子注入,以形成发射极注入区104。所述发射极注入区104是由n+型注入在所述半导体衬底100中形成的掺杂区,例如,通过砷注入形成。与步骤3)相同,如果其他区域上已有氧化层等覆盖保护,则这些区域上也可不额外覆盖光刻胶层;在离子注入完成后,去除残留的光刻胶层,并对注入离子进行退火激活等工艺。

100.作为示例,如图9所示,在步骤4)后,还包括在所述半导体衬底100上方形成发射极金属层107,以及在所述半导体衬底100背面形成背面注入层108和集电极金属层109的步骤。可选地,igbt器件的背面工艺流程包括背面减薄、注入和金属化等工艺,以形成所述背面注入层108和所述集电极金属层109,所述背面注入层108为p型注入层。

101.本实施例提供了一种窄台面绝缘栅双极型晶体管器件的形成方法,在成对的所述栅极沟槽结构101之间的主动台面区(active mesa)中不设置p型掺杂区,即阱区103,而成对的所述发射极沟槽结构102之间的非主动台面区(inactive mesa)中则形成有p型掺杂区以及位于p型掺杂区上方的n+型掺杂区。通过本实施例的形成方法得到的窄台面绝缘栅双极型晶体管器件不但通过引入窄台面区增强电子注入,获得了较低的器件导通电阻r

on

,也通过减少窄台面区的空穴浓度,增强了抗短路能力,消除了cibl效应。

102.综上所述,本发明提供了一种窄台面绝缘栅双极型晶体管器件及形成方法,所述窄台面绝缘栅双极型晶体管器件包括:半导体衬底;形成于所述半导体衬底正面并沿水平方向间隔排列的栅极沟槽结构和发射极沟槽结构;所述栅极沟槽结构和所述发射极沟槽结构在排列方向上各自成对设置,且成对的所述栅极沟槽结构与成对的所述发射极沟槽结构在排列方向上相互交叠设置;形成于成对的所述发射极沟槽结构之间的阱区;形成于成对的所述栅极沟槽结构之间以及成对的所述发射极沟槽结构之间的发射极注入区;在成对的所述发射极沟槽结构之间的区域中,所述发射极注入区位于所述阱区上方。本发明引入了一种新的窄台面绝缘栅双极型晶体管器件及形成方法,在主动台面区不设置p型掺杂区,而在非主动台面区中形成p型掺杂区以及位于p型掺杂区上方的n+型掺杂区,不但通过引入窄台面区增强电子注入,获得了较低的器件导通电阻,也通过减少窄台面区的空穴浓度,增强了器件抗短路能力,消除了cibl效应。

103.上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟

悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1