3D存储器件的制造方法及其3D存储器件与流程

3d存储器件的制造方法及其3d存储器件

技术领域

[0001]

本发明涉及存储器件技术领域,特别涉及一种3d存储器件的制造 方法及其3d存储器件。

背景技术:

[0002]

存储器件的存储密度的提高与半导体制造工艺的进步密切相关。随 着半导体制造工艺的特征尺寸(cd)越来越小,存储器件的存储密度越 来越高。为了进一步提高存储密度,已经开发出三维结构的存储器件(即, 3d存储器件)。3d存储器件包括沿着垂直方向堆叠的多个存储单元,在 单位面积的晶片上可以成倍地提高集成度,并且可以降低成本。

[0003]

现有的3d存储器件主要用作非易失性的闪存。两种主要的非易失 性闪存技术分别采用nand和nor结构。与nor存储器件相比,nand 存储器件中的读取速度稍慢,但写入速度快,擦除操作简单,并且可以 实现更小的存储单元,从而达到更高的存储密度。因此,采用nand结 构的3d存储器件获得了广泛的应用。

[0004]

在3d nand的产品结构中,在绝缘叠层中形成栅线缝隙,通过栅 线缝隙将绝缘叠层置换为栅叠层结构,但是在实际的制造过程中,存在 栅线缝隙的宽度cd小于去除牺牲层后的空腔space高度的情况,如图1 所示,这种情况下,在空腔中填充金属材料时容易出现空腔还未填充好, 而栅线缝隙已经闭合的情况,降低了3d存储器件的良率和可靠性。

技术实现要素:

[0005]

鉴于上述问题,本发明的目的在于提供一种3d存储器件的制造方 法,在将第一牺牲层置换为栅极导体的过程中,通过多次填充以及回蚀 刻的步骤,避免了第一空腔未填满而栅线缝隙已经闭合的情况,从而提 高了3d存储器件的良率和可靠性。

[0006]

根据本发明的一方面,提供一种3d存储器件的制造方法,包括: 在衬底上依次形成第一牺牲层,绝缘叠层结构和贯穿所述绝缘叠层结构 的多个沟道柱,所述绝缘叠层结构包括交替堆叠的绝缘层和牺牲层;形 成贯穿所述绝缘叠层结构的栅线缝隙;通过栅线缝隙去除所述第一牺牲 层,形成与栅线缝隙连通的第一空腔;经过多次在栅线缝隙和第一空腔 中填充金属层和对所述金属层进行蚀刻,从而形成栅极导体层。

[0007]

优选地,经过多次在栅线缝隙和第一空腔中填充金属层和对所述金 属层进行蚀刻,从而形成栅极导体层的步骤包括:经由所述栅线缝隙在 所述第一空腔中填充金属层;对所述栅线缝隙中的金属层进行回蚀刻, 暴露所述金属层中的第一空腔;经由所述栅线缝隙再次填充金属层。

[0008]

优选地,还包括:对所述栅线缝隙中的金属层进行回蚀刻以及再次 填充金属层,直到所述金属层中没有空腔。

[0009]

优选地,对所述栅线缝隙中的金属层进行回蚀刻的步骤包括:经由 所述栅线缝隙在所述第一空腔中填充氧化物;对栅线缝隙中的氧化物进 行回蚀刻,保留所述第一空腔中的氧化物;对所述栅线缝隙中侧壁的金 属层进行回蚀刻,保留所述第一空腔中的金属层;

去除所述第一空腔中 的氧化物。

[0010]

优选地,经由所述栅线缝隙在所述第一空腔中填充金属层的步骤之 前,还包括:在所述栅线缝隙的侧壁形成蚀刻停止层。

[0011]

优选地,在所述栅线缝隙的侧壁形成蚀刻停止层和经由所述栅线缝 隙在所述第一空腔中填充金属层的步骤之间,还包括:经由所述栅线缝 隙和所述第一空腔去除所述沟道柱的部分氧化物-氮化物-氧化物结构; 在所述第一空腔中沿所述沟道柱的侧壁与所述衬底表面形成外延层。

[0012]

优选地,在所述空腔中沿所述沟道柱的侧壁与衬底表面形成外延层 与经由所述栅线缝隙在所述第一空腔中填充金属层的步骤之间,还包括: 去除所述栅线缝隙侧壁的蚀刻停止层;去除所述绝缘叠层结构中的第二 牺牲层,形成第二空腔,在所述第二空腔中填充金属层。

[0013]

优选地,去除所述绝缘叠层结构中的第二牺牲层的步骤之后,还包 括:对所述外延层进行氧化,形成第二绝缘层。

[0014]

优选地,在衬底上形成第一牺牲层的步骤之前,还包括:对所述衬 底进行离子注入,形成掺杂层,所述第一牺牲层位于所述掺杂层的表面 上。

[0015]

优选地,所述沟道柱依次包括:第三绝缘层,沟道层,隧穿介质层, 电荷存储层和阻挡介质层,所述阻挡介质层与所述绝缘叠层结构接触。

[0016]

优选地,经由所述栅线缝隙和所述第一空腔去除所述沟道柱的隧穿 介质层,电荷存储层和阻挡介质层,暴露所述沟道层。

[0017]

优选地,去除所述绝缘叠层结构中的第二牺牲层以及在所述第二空 腔中填充金属层的步骤之间,还包括:经由所述栅线缝隙在所述第一空 腔和所述第二空腔中形成核层,所述核层位于所述金属层与第一绝缘层 之间。

[0018]

优选地,在经过多次在栅线缝隙和第一空腔中填充金属层和对所述 金属层进行蚀刻,从而形成栅极导体层的步骤之后,还包括:在所述栅 线缝隙中形成源极导电通道。

[0019]

优选地,在所述栅线缝隙中形成源极导电通道的步骤包括:在所述 栅线缝隙的侧壁上形成隔离层,在所述栅线缝隙中沉积导电材料,形成 源极导电通道,所述隔离层隔离所述源极导电通道与所述栅极导体。

[0020]

根据本发明的另一方面,提供一种3d存储器件,根据如前述所述 的3d存储器件的制造方法形成的3d存储器件。

[0021]

本发明提供的3d存储器件的制造方法,在将第一牺牲层置换为栅 极导体的过程中,通过多次填充以及回蚀刻的步骤,避免了第一空腔未 填满而栅线缝隙已经闭合的情况,从而提高了3d存储器件的良率和可 靠性。。

附图说明

[0022]

通过以下参照附图对本发明实施例的描述,本发明的上述以及其他 目的、特征和优点将更为清楚,在附图中:

[0023]

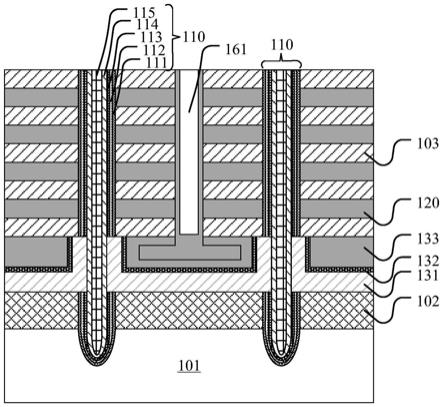

图1示出了现有技术中3d存储器件置换栅极导体的截面图;

[0024]

图2a和图2b分别示出了3d存储器结构的存储单元串的电路图和 结构示意图;

[0025]

图3a至图3l示出了根据本发明实施例的3d存储器件的的制造方法 的各阶段截面

图。

具体实施方式

[0026]

以下将参照附图更详细地描述本发明的各种实施例。在各个附图中, 相同的元件采用相同或类似的附图标记来表示。为了清楚起见,附图中 的各个部分没有按比例绘制。

[0027]

以下将参照附图更详细地描述本发明。在各个附图中,相同的元件 采用类似的附图标记来表示。为了清楚起见,附图中的各个部分没有按 比例绘制。此外,可能未示出某些公知的部分。为了简明起见,可以在 一幅图中描述经过数个步骤后获得的半导体结构。

[0028]

应当理解,在描述器件的结构时,当将一层、一个区域称为位于另 一层、另一个区域“上面”或“上方”时,可以指直接位于另一层、另 一个区域上面,或者在其与另一层、另一个区域之间还包含其它的层或 区域。并且,如果将器件翻转,该一层、一个区域将位于另一层、另一 区域“下面”或“下方”。

[0029]

如果为了描述直接位于另一层、另一区域上面的情形,本文将采用

ꢀ“

直接在

……

上面”或“在

……

上面并与之邻接”的表述方式。

[0030]

在3d nand的产品结构中,需要在栅叠层中形成贯穿栅叠层的沟 道柱,但由于栅叠层中栅极导体采用导电性较高的材料例如钨,而刻蚀 金属的工艺较难,因此先形成绝缘叠层,在绝缘叠层中形成沟道柱后再 形成栅线缝隙(gate line slit,gls),通过栅线缝隙将绝缘叠层置换为 栅叠层结构,但是在实际的制造过程中,存在栅线缝隙的宽度cd小于 去除牺牲层后的空腔space高度的情况,如图1所示,这种情况下,在 空腔中填充金属材料时容易出现空腔还未填充好,而栅线缝隙已经闭合 的情况,降低了3d存储器件的良率和可靠性。

[0031]

本申请的发明人注意到上述问题,提出了一种3d存储器件的制造 方法。

[0032]

下面结合附图和实施例,对本发明的具体实施方式作进一步详细描 述。

[0033]

图2a和2b分别示出三维存储器结构的存储单元串的电路图和结构 示意图。在该实施例中示出的存储单元串包括4个存储单元的情形。可 以理解,本发明不限于此,存储单元串中的存储单元数量可以为任意多 个,例如,32个或64个。

[0034]

如图2a所示,存储单元串100的第一端连接至位线bl,第二端连 接至源极线sl。存储单元串100包括在第一端和第二端之间串联连接的 多个晶体管,包括:第一选择晶体管q1、存储单元m1至m4、以及第 二选择晶体管q2。第一选择晶体管q1的栅极连接至串选择线ssl,第 二选择晶体管q2的栅极连接至地选择线gsl。存储单元m1至m4的 栅极分别连接至字线wl1至wl4的相应字线。

[0035]

如图2b所示,存储单元串100的选择晶体管q1和q2分别包括第 二导体层122和第三导体层123,存储单元m1至m4分别包括第一导体 层121。第一导体层121、第二导体层122和第三导体层123与存储单元 串100中的晶体管的堆叠顺序一致,相邻的导体层之间彼此采用绝缘层 隔开,从而形成栅叠层结构。

[0036]

进一步地,存储单元串100包括存储串110。存储串110与栅叠层 结构相邻或者贯穿栅叠层结构。在存储串110的中间部分,第一导体层 121与沟道层111之间夹有隧穿介质层112、电荷存储层113和阻挡介质 层114,从而形成存储单元m1至m4。在存储串110的两端,第二导体 层122和123与沟道层111之间夹有阻挡介质层114,从而形成第一选 择晶体管q1

和第二选择晶体管q2。

[0037]

沟道层111例如由掺杂多晶硅组成,隧穿介质层112和阻挡介质层 114分别由氧化物组成,例如氧化硅,电荷存储层113由包含量子点或 者纳米晶体的绝缘层组成,例如包含金属或者半导体的微粒的氮化硅, 第一导体层121、第二导体层122和第三导体层123由金属组成,例如 钨。沟道层111用于提供选择晶体管和控制晶体管的沟道区,沟道层111 的掺杂类型与选择晶体管和控制晶体管的类型相同。例如,对于n型的 选择晶体管和控制晶体管,沟道层111可以是n型掺杂的多晶硅。

[0038]

在该实施例中,存储串110的芯部为沟道层111,隧穿介质层112、 电荷存储层113和阻挡介质层114形成围绕芯部侧壁的叠层结构。在替 代的实施例中,存储串110的芯部为附加的第三绝缘层,沟道层111、 隧穿介质层112、电荷存储层113和阻挡介质层114形成围绕半导体层 的叠层结构。

[0039]

在该实施例中,第一选择晶体管q1和第二选择晶体管q2、存储单 元m1至m4使用公共的沟道层111和阻挡介质层114。在存储串110中, 沟道层111提供多个晶体管的源漏区和沟道层。在替代的实施例中,可 以采用彼此独立的步骤,分别形成第一选择晶体管q1和第二选择晶体 管q2的半导体层和阻挡介质层以及存储单元m1至m4的半导体层和阻 挡介质层。在存储串110中,第一选择晶体管q1和第二选择晶体管q2 的半导体层与存储单元m1至m4的半导体层彼此电连接。

[0040]

在写入操作中,存储单元串100利用fn隧穿效率将数据写入存储 单元m1至m4中的选定存储单元。以存储单元m2为例,在源极线sl 接地的同时,地选择线gsl偏置到大约零伏电压,使得对应于地选择线 gsl的第二选择晶体管q2断开,串选择线ssl偏置到高电压vdd,使 得对应于串选择线ssl的选择晶体管q1导通。进一步地,位线bit2 接地,字线wl2偏置于编程电压vpg,例如20v左右,其余字线偏置 于低电压vps1。由于只有选定存储单元m2的字线电压高于隧穿电压, 因此,该存储单元m2的沟道区的电子,经由隧穿介质层112到达电荷 存储层113,从而将数据转变成电荷存储于存储单元m2的电荷存储层 113中。

[0041]

在读取操作中,存储单元串100根据存储单元m1至m4中的选定 存储单元的导通状态判断电荷存储层中的电荷量,从而获得该电荷量表 征的数据。以存储单元m2为例,字线wl2偏置于读取电压vrd,其 余字线偏置于高电压vps2。存储单元m2的导通状态与其阈值电压相关, 即与电荷存储层中的电荷量相关,从而根据存储单元m2的导通状态可 以判断数据值。存储单元m1、m3和m4始终处于导通状态,因此,存 储单元串100的导通状态取决于存储单元m2的导通状态。控制电路根 据位线bl和源极线sl上检测的电信号判断存储单元m2的导通状态, 从而获得存储单元m2中存储的数据。

[0042]

图3a至图3l示出了根据本发明实施例的3d存储器件的的制造方法 的各阶段截面图。

[0043]

参考图3a,对衬底101进行离子注入,以及在衬底101离子注入的 表面上方形成第一牺牲层1041和绝缘叠层结构。

[0044]

在该实施例中,衬底101的材料可以包括硅(例如单晶硅)、硅锗 (sige)、砷化镓(gaas)、锗(ge)、绝缘体上硅(soi)、绝缘体上锗 (goi)或者任何其他适当材料。

[0045]

对衬底101进行离子注入,形成掺杂层102,提高导电性。在该实 施例中,掺杂层102例如为n型(使用n型掺杂剂,例如p、as等) 或p型(使用p型掺杂剂,例如b等)。掺杂层102

作为后续形成的源 极导电通道的接触区,用于降低源极导电通道与衬底101之间的接触电 阻,提高源极导电通道与沟道柱之间的导电性。

[0046]

进一步地,在掺杂层102的表面形成第一牺牲层1041和绝缘叠层结 构。在该实施例中,绝缘叠层结构包括堆叠的多个第二牺牲层104,相 邻第二牺牲层104之间由第一绝缘层103彼此隔开,第一牺牲层1041 与第二牺牲层104之间由第一绝缘层103彼此隔开。其中,第一绝缘层 103例如由氧化硅组成,第一牺牲层1041与第二牺牲层104例如由氮化 硅组成。参考图3a,靠近掺杂层102的第一牺牲层1041在后续步骤中 将被置换为底部选择栅极(bsg),且第一牺牲层1041的厚度高于其他 的第二牺牲层104。

[0047]

如下文所述,第一牺牲层1041与第二牺牲层104将置换成栅极导体 121至123(参考图2b),栅极导体121一步连接至串选择线,栅极导体 123一步连接至地选择线,栅极导体122一步连接至字线。为了形成从 栅极导体121至123到达字线的导电通道,多个第二牺牲层104例如图 案化为台阶状,即,每个第二牺牲层104的边缘部分相对于上方的第二 牺牲层104暴露以提供电连接区。在多个第二牺牲层104的图案化步骤 之后,可以采用绝缘层覆盖绝缘叠层结构。

[0048]

在其他实施例中,第一牺牲层1041例如由三层组成,从而使得第一 牺牲层1041的高度较高。

[0049]

进一步地,在绝缘叠层结构中形成沟道柱110,如图3b所示。

[0050]

在该步骤中,需要先在绝缘叠层结构中形成沟道孔(图中未示出)。 在该实施例中,例如在半导体结构的表面上形成光致抗蚀剂掩模,然后 进行各向异性蚀刻,在绝缘叠层结构中形成沟道孔。各向异性蚀刻可以 采用干法蚀刻,如离子铣蚀刻、等离子蚀刻、反应离子蚀刻、激光烧蚀。 例如,通过控制蚀刻时间,使得蚀刻在衬底101的下方附近停止,或者 蚀刻在掺杂层102的下方附近停止。在蚀刻之后通过在溶剂中溶解或灰 化去除光致抗蚀剂掩模。

[0051]

进一步地,在沟道孔中形成沟道柱110。沟道柱110包括从其上部 延伸至下部的沟道层111。参见图3b,在沟道柱110的中间部分,沟道 柱110包括依次堆叠在沟道层111上的隧穿介质层112、电荷存储层113 和阻挡介质层114,在沟道柱110的两端,沟道柱110包括堆叠在沟道 层111或半导体层上的阻挡介质层114。沟道柱110的下端与衬底101 中的公共源区相接触。在最终的3d存储器结构中,沟道柱110的上端 将与布线层相连接,从而形成有效的存储单元。所述沟道柱110的结构 例如为onop(氧化物-氮化物-氧化物-多晶硅),其中,沟道层111的材 料为多晶硅。

[0052]

在该实施例中,还包括在沟道层111内侧壁填充的第三绝缘层115, 第三绝缘层115填充沟道层111内侧壁的剩余空间,以提高沟道柱110 的支撑作用。

[0053]

进一步地,在绝缘叠层结构中形成栅线缝隙161,在栅线缝隙161 的侧壁形成蚀刻停止层106,以及通过栅线缝隙161去除第一牺牲层1041, 如图3c所示。

[0054]

在该实施例中,在形成栅线缝隙161时,可以采用各向异性蚀刻, 例如采用干法蚀刻,如离子铣蚀刻、等离子蚀刻、反应离子蚀刻、激光 烧蚀。例如,通过控制蚀刻时间,使得蚀刻在第一牺牲层1041的表面附 近停止。在该实施例中,栅线缝隙161将栅极导体分割成多条栅线。

[0055]

进一步地,在栅线缝隙161的侧壁上形成蚀刻停止层106,蚀刻停 止层106例如包

括两层,用于保护绝缘叠层结构在后续蚀刻步骤中不被 蚀刻。在该实施例中,例如采用原子层沉积(ald)形成蚀刻停止层106, 以及蚀刻去除栅线缝隙161底部的蚀刻停止层106,从而暴露第一牺牲 层1041。蚀刻停止层106例如由氧化硅和氮化硅组成,其中,氧化硅材 料暴露在栅线缝隙161的通道中。

[0056]

进一步地,经由栅线缝隙161去除第一牺牲层1041,形成第一空腔105。在该实施例中,利用栅线缝隙161作为蚀刻剂通道,采用各向同性 蚀刻去除绝缘叠层结构中的第一牺牲层1041从而形成第一空腔105。由 于栅线缝隙161的侧壁形成有蚀刻停止层106,因此蚀刻过程中只能去 除栅线缝隙161底部暴露的第一牺牲层1041。各向同性蚀刻可以采用选 择性的湿法蚀刻或气相蚀刻。在湿法蚀刻中使用蚀刻溶液作为蚀刻剂, 其中,将半导体结构浸没在蚀刻溶液中。在气相蚀刻中使用蚀刻气体作 为蚀刻剂,其中,将半导体结构暴露于蚀刻气体中。

[0057]

在该实施例中,去除第一牺牲层1041后暴露沟道柱110的下部。

[0058]

进一步地,经由第一空腔105去除沟道柱110暴露部分的ono结 构,如图3d所示。

[0059]

在该实施例中,ono结构由阻挡介质层114,电荷存储层113以及 隧穿介质层112组成,它们的材料依次为氧化物,氮化物,氧化物,在 经由第一空腔105去除时,可以采用湿法蚀刻去除。湿法蚀刻的蚀刻溶 液例如为氢氟酸、磷酸等酸性腐蚀液。

[0060]

在该实施例中,经由第一空腔105去除沟道柱110暴露部分的ono 结构时,由于栅线缝隙161的侧壁具有蚀刻停止层106,因此不会对绝 缘叠层结构中的第二牺牲层104造成影响。

[0061]

进一步地,经由栅线缝隙161在第一空腔105中形成外延层131, 如图3e所示。

[0062]

在该步骤中,采用外延生长工艺形成“l”结构的选择性外延生长 (selective epitaxy growth,seg)的外延层131。在该实施例中,外延 层131的材料为单晶硅,外延层131沿空腔中掺杂层102的表面以及沟 道柱110暴露的沟道层111的表面外延生长。

[0063]

在该实施例中,外延生长工艺是指在单晶基底上生长一层跟单晶基 底具有相同晶格排列的单晶材料。外延层可以是同质外延层(si/si),也 可以是异质外延层(sige/si或sic/si等)。实现外延生长包括分子束外 延(mbe)、超高真空化学气相沉积(uhv/cvd)、常压及减压外延 (atm&rp epi)等。

[0064]

进一步地,去除栅线缝隙161侧壁的蚀刻停止层106以及绝缘叠层 结构中的第二牺牲层104,形成第一空腔105,以及在外延层131的表面 形成第二绝缘层132,如图3f所示。

[0065]

在该步骤中,利用栅线缝隙作为蚀刻剂通道,采用各向同性蚀刻去 除绝缘叠层结构中的第二牺牲层104从而形成第二空腔107。各向同性 蚀刻可以采用选择性的湿法蚀刻或气相蚀刻。在湿法蚀刻中使用蚀刻溶 液作为蚀刻剂,其中,将半导体结构浸没在蚀刻溶液中。在气相蚀刻中 使用蚀刻气体作为蚀刻剂,其中,将半导体结构暴露于蚀刻气体中。进 一步地,将外延层131暴露的表面进行氧化,形成第二绝缘层132。

[0066]

在该步骤中,第一空腔105的高度space大于栅线缝隙161的宽度 cd。

[0067]

进一步地,经由栅线缝隙161在第一空腔105和空腔106中填充金 属层,形成底部选择栅极133和栅极导体120,如图3g所示。

[0068]

在该步骤中,利用栅线缝隙161作为沉积物通道,采用原子层沉积 (ald),在栅线缝隙161和第一空腔105,第二空腔107中填充金属层。 在该实施例中,金属层例如由钨组

成。

[0069]

在该实施例中,由于待填充的第一空腔105的高度space大于栅线 缝隙161的宽度cd,因此,容易出现栅线缝隙161已填充满,但第一 空腔105未填充满的情况,因此,在该步骤中,当绝缘叠层结构中的第 二空腔107填充满,而栅线缝隙未填充满时,停止填充步骤。

[0070]

在该实施例中,在填充金属层的步骤之前,还包括,经由栅线缝隙 161,采用原子层沉积(ald),在半导体结构的表面形成核层(图中未 示出)。核层作为栅极导体与第一绝缘层103之间的缓冲层,材料例如为 钨的硅化物或氮化物。

[0071]

进一步地,经由栅线缝隙161继续往第一空腔105中填充氧化物108, 如图3h所示。

[0072]

在该步骤中,利用栅线缝隙161作为沉积物通道,采用原子层沉积 (ald),在栅线缝隙161和第一空腔105中填充氧化物108,当栅线缝 隙161出现被氧化物108填充满的情况时,停止填充。

[0073]

在该实施例中,由于填充氧化物前栅线缝隙161的宽度不大于第一 空腔105的高度,因此任会出现栅线缝隙161已填充满,但第一空腔105 还存在的情况。

[0074]

进一步地,去除栅线缝隙161中的金属材料,恢复栅线缝隙161的 宽度,如图3i所示。

[0075]

在该步骤中,首先需要去除栅线缝隙161中的一部分氧化物108, 只保留第一空腔105中的部分氧化物108。然后对栅线缝隙161中的金 属材料进行回蚀刻,恢复栅线缝隙161的宽度。

[0076]

在该实施例中,回蚀刻例如使用氟化硫、氮化氯作为蚀刻剂,以移 除栅线缝隙161中的钨材料。

[0077]

进一步地,去除第一空腔105中的氧化物108,以及继续向第一空 腔105中填充金属材料,如图3j和3k所示。

[0078]

在该实施例中,去除第一空腔105中的氧化物108后,由于栅线缝 隙161的宽度恢复而第一空腔105的高度小于之前的高度,因此再次填 充钨材料时第一空腔105被填充满,不再留有空隙。

[0079]

若该步骤仍不能消除空腔,则可以重复图3h至图3k所示的步骤, 直至第一空腔105消失。

[0080]

该实施例中,通过多次填充和回蚀刻,使底部选择栅极生长更均匀, 从而提高了3d存储器件的电性能测试(wafer accept test,wat)性能。

[0081]

进一步地,去除栅线缝隙161中的金属材料,在栅线缝隙161中形 成源极导电通道140,如图3l所示。

[0082]

在该步骤中,对栅线缝隙161中的金属材料进行回蚀刻,以暴露栅 叠层结构中的第一绝缘层103,以及在栅线缝隙161中形成源极导电通 道140。

[0083]

在该实施例中,源极导电通道140与栅叠层结构之间还包括隔离层 (图3l中未示出),用于隔离源极导电通道140与栅极导体120和底部 选择栅极133。隔离层的材料例如与第一绝缘层103的材料相同,由氧 化硅组成。在其他实施例中,隔离层的材料也可以与第一绝缘层103的 材料不相同。

[0084]

在该实施例中,源极导电通道140贯穿栅叠层结构,第一端经由第 二绝缘层132,外延层131与掺杂层102与衬底101接触,第二端延伸 至栅叠层结构的上方从而方便后续布

线层的形成。

[0085]

在该实施例中,源极导电通道140的第一端经由第二绝缘层132和 外延层131实现与沟道柱110中的沟道层111之间的电连接,从而构成 nand存储器件的切换选择器件。

[0086]

本申请的3d存储器件的制造方法中,通过多次填充以及回蚀刻的 步骤形成底部选择栅极,由于经过回蚀刻以及再次的填充,极大地降低 了底部选择栅极中的空腔问题,使得底部选择栅极生长更均匀,从而提 高了3d存储器件的良率和可靠性。

[0087]

依照本发明的实施例如上文所述,这些实施例并没有详尽叙述所有 的细节,也不限制该发明仅为所述的具体实施例。显然,根据以上描述, 可作很多的修改和变化。本说明书选取并具体描述这些实施例,是为了 更好地解释本发明的原理和实际应用,从而使所属技术领域技术人员能 很好地利用本发明以及在本发明基础上的修改使用。本发明仅受权利要 求书及其全部范围和等效物的限制。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1