半导体图像传感器的制作方法

1.本发明涉及一种半导体图像传感器,尤其涉及一种对近红外光高灵敏度且实现小面积下的集成化的半导体图像传感器。

背景技术:

2.作为周知的半导体图像传感器(以下称为光传感器),已知有光接收元件使用形成于硅基板的pn接合二极管的半导体图像传感器。为了使所述光传感器运行,首先需要对pn接合二极管施加反向偏压,即需要对p型半导体层施加负偏压,对n型半导体层施加正偏压。由此,在pn接合部形成无载流子的空乏层。若对所述空乏层照射光,则其光能导致产生电子空穴对(载流子)(称为光电效应),通过空乏层中的电场,电子被拉向施加了正电压的n型半导体层中,空穴被拉向施加了负电压的p型半导体层。由此,pn接合二极管的端子间的电荷量会根据光信号而变化,因此可将光信号转换为电信号(称为光电转换)。

3.在利用使用硅基板的pn接合二极管进行的光电转换中,可检测的光的长波长侧(光能低的一侧)的极限由硅内的带隙宽度所决定。

4.硅的带隙宽度约为1.1ev,因此使用硅的pn接合二极管的光传感器仅能够检测波长约为1,100nm以下的光。

5.所述波长(约1,100nm)处于近红外区域。

6.图1表示以硅作为介质的光的吸收系数,波长为1,100nm附近的近红外光的光吸收系数小,检测灵敏度低。因此,之前通过对硅的光传感器采取某种措施来提高对近红外光的灵敏度。

7.作为所述措施之一,专利文献1或非专利文献1中记载有通过使入射至光传感器的近红外光在光传感器内分散,而延长近红外光通过光传感器内的光程,提高灵敏度。具体而言,通过在形成光接收元件的硅的表面形成棱锥状的凹凸来将其实现。

8.进而,通过在光接收元件表面形成被称为扩散板的特殊的层,而使近红外光分散,提高灵敏度。然而,这些现有方法会导致制造工艺增加,伴随着成本上升。又,仅使近红外光分散不能充分改善灵敏度,效果有限。

9.与此相对,加厚成为光电转换区域的空乏层的方法对于提高灵敏度而言有效。

10.图2表示相对于各光波长的、空乏层宽度与光吸收率的关系。根据所述图可知,若能够将空乏层宽度控制为300μm以上,则对于处于近红外区域的光,可获得充分的光吸收。

11.图3表示相对于形成pn接合的硅基板的杂质浓度的反向偏压与空乏层宽度的关系。

12.可知通常使用的硅基板的浓度为1

×

10

15

/cm3左右,若使用低浓度基板(~1

×

10

12

/cm3),则空乏层宽度在同一偏压下约厚一个数量级。

13.图4以光波长为参数,表示用以保持与可见光相同程度的灵敏度的反向偏压与基板的杂质浓度的关系。

14.可知为了使用基板浓度为2

×

10

12

/cm3左右的浮区(floating zone,fz)基板来针

对波长940nm的近红外光实现保持与可见光相同程度的灵敏度的光传感器,必须施加50v左右的偏压。

15.因此,光传感器包括高电压产生电路,所述高电压产生电路产生高电压来对pn接合二极管施加反向偏压。高电压产生电路通常是用来将电源电压(vcc)升压而获得特定的高电压的电路,已知有电荷泵电路。

16.电荷泵电路是通过使用电容器(condenser)(c1~c9)与二极管(d1~d9)将输入信号(电源电压:vcc)切换为接通/断开而实现的电路,已知有各种电路结构,图5表示其一例。

17.若在硅基板形成所述电荷泵电路,则存在其占有面积增大、光传感器大型化的缺陷。

18.因此,如专利文献2所示,也已知在绝缘层上硅(silicon on insulator,soi)基板的半导体层中形成电荷泵电路,所述soi基板包括硅基板、形成于所述硅基板上的绝缘膜及形成于所述绝缘膜上的所述半导体层。在所述文献所公开的电荷泵电路中,将在所述半导体层中形成的p型区域与n型区域接合,形成互相独立的多个二极管,并将所述二极管串联。

19.[现有技术文献]

[0020]

[专利文献]

[0021]

专利文献1:日本专利特开2017

‑

108062

[0022]

专利文献2:日本专利特开平7

‑

177729

[0023]

[非专利文献]

[0024]

非专利文献1:oshiyama等人(oshiyama et al.),《用于衍射结构的具有金字塔表面的背照互补金属氧化物半导体图像传感器的近红外灵敏度增强(near

‑

infrared sensitivity enhancement of a back

‑

illuminated complementary metal oxide semiconductor image sensor with a pyramid surface for diffraction structure)》,ieee tech.digst.of iedm 2017,第397

‑

400页,2017.

技术实现要素:

[0025]

[发明所要解决的问题]

[0026]

本发明的目的在于实现一种半导体图像传感器,所述半导体图像传感器在对形成于硅基板的成为光接收元件的pn接合二极管施加高电压的反向偏压时,可获得充分厚的(宽的)空乏层,且不会导致高电压产生电路的占有面积增大。

[0027]

[解决问题的技术手段]

[0028]

本发明的半导体图像传感器的特征在于包括:光接收元件,形成于soi基板的绝缘膜下的硅基板,并且沿着与所述硅基板的主面垂直的方向形成,且包括对近红外光具有灵敏度的pn接合二极管,所述soi基板包括所述硅基板、形成于所述硅基板上的所述绝缘膜及形成于所述绝缘膜上的半导体层;高电压产生电路,产生用来对所述pn接合二极管施加反向偏压的施加电压,所述硅基板的杂质浓度处于1

×

10

12

/cm3至1

×

10

14

/cm3的范围内,膜厚处于300μm至700μm的范围内,所述施加电压处于10v至60v的范围内。

[0029]

又,本发明的半导体图像传感器的特征在于:包括埋入氧化物(buried oxide,box)电容器(capacitor),隔着所述绝缘膜,以所述半导体层作为第一电极,以形成于所述硅基板的扩散层作为第二电极,所述第一电极连接于所述高电压产生电路的输出端。

[0030]

又,本发明的半导体图像传感器的特征在于:所述box电容器(capacitor)的所述绝缘膜的膜厚处于100nm至300nm的范围内。

[0031]

本发明的半导体图像传感器的特征在于:包括第一区域、第二区域及栅极电极,所述第一区域与第二区域形成于所述绝缘膜上的所述半导体层,隔着通道区域且互相相接,所述栅极电极形成于所述通道区域上,所述第一区域与所述通道区域具有互相相同的导电型,所述第二区域与所述通道区域具有互不相同的导电型,将所述栅极电极与所述第二区域连接,使用隔着所述通道区域的所述第一区域与所述第二区域作为二极管,且以电荷泵电路作为所述高电压产生电路,所述电荷泵电路将多个所述二极管串联,向各二极管提供信号,输出高电压。

[0032]

进而,本发明的半导体图像传感器的特征在于:所述半导体层的杂质浓度处于1

×

10

15

/cm3至3

×

10

18

/cm3的范围内,所述半导体层的膜厚处于10nm至100nm的范围内。

[0033]

[发明的效果]

[0034]

使用低杂质浓度的soi基板,在soi基板的半导体层形成包括电荷泵电路的高电压产生电路,在基板内形成包括对近红外光具有灵敏度的pn接合二极管的光接收元件,由此可实现在单一电源下工艺或面积的增加也得以抑制的高灵敏度的近红外传感器。

附图说明

[0035]

图1是表示以硅作为介质的光的波长与光吸收系数的关系的图。

[0036]

图2是表示相对于各光波长的空乏层宽度与光吸收率的关系的图。

[0037]

图3是以形成pn接合的硅基板的杂质浓度作为参数,表示反向偏压与空乏层宽度的关系的图。

[0038]

图4是以光波长作为参数,表示用以保持与可见光相同程度的灵敏度的反向偏压与基板的杂质浓度的关系的图。

[0039]

图5是表示通过使用电容器(condenser)与二极管将输入信号切换为接通/断开而实现的电荷泵电路的一例的图。

[0040]

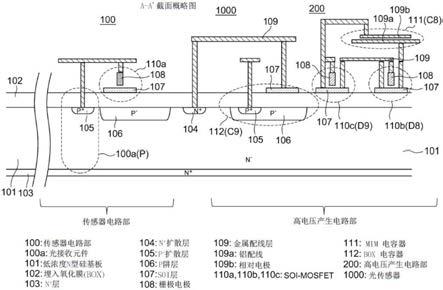

图6是表示本发明的第一实施形态的光传感器的结构的概略平面图。

[0041]

图7是示意性表示图6的a

‑

a'截面的a

‑

a'截面概略图。

[0042]

图8是周知的轻掺杂漏极(lightly doped drain,ldd)构造的金属氧化物半导体场效应晶体管(metal

‑

oxide

‑

semiconductor field effect transistor,mosfet)的截面构造图。

[0043]

图9是在块体(硅基板)形成mosfet的情形时的截面构造图。

[0044]

图10是将埋入氧化膜(box)上的半导体层互相分离来形成mosfet的情形时的截面构造图。

[0045]

图11是本发明的第一实施形态的高电压产生电路部的制造步骤图(其一)。

[0046]

图12是本发明的第一实施形态的高电压产生电路部的制造步骤图(其二)。

[0047]

图13是本发明的第一实施形态的高电压产生电路部的制造步骤图(其三)。

[0048]

图14是本发明的第一实施形态的高电压产生电路部的制造步骤图(其四)。

[0049]

图15是本发明的第一实施形态的高电压产生电路部的制造步骤图(其五)。

[0050]

图16是本发明的第一实施形态的高电压产生电路部的制造步骤图(其六)。

[0051]

图17是本发明的第一实施形态的高电压产生电路部的制造步骤图(其七)。

[0052]

图18是本发明的第二实施形态的高电压产生电路部所使用的二极管的截面结构图。

[0053]

图19是图18所示的二极管的制造步骤图。

[0054]

图20是表示对从背面向光接收元件照射光时的相对于光波长的量子效率进行测定所获得的结果的图。

[0055]

图21是将三种二极管的构造加以比较而表示的图。

[0056]

图22是表示图21所示的三个二极管构造中的反向偏压与漏电流的关系的图。

具体实施方式

[0057]

以下,参照附图对本发明的实施形态的一例进行详细说明。

[0058]

(第一实施形态)

[0059]

图6是表示本发明的第一实施形态的光传感器的结构的概略平面图,图7是示意性表示图6的a

‑

a'截面的a

‑

a'截面概略图。

[0060]

本发明的光传感器1000包括传感器电路部100、高电压产生电路部200及控制电路部300。

[0061]

传感器电路部100包括光接收元件100a及对流入光接收元件100a的光电流进行检测的金属氧化物半导体(metal

‑

oxide

‑

semiconductor,mos)晶体管110a。光接收元件100a将包括pn接合二极管的多个单传感器像素p排列成阵列状而构成传感器电路部100。如图7所示,光接收元件100a以形成于低浓度n型硅基板101的背面的n

+

扩散层103[104]作为阴极电极,以形成于所述低浓度n型硅基板101主面附近的p

+

扩散层105作为阳极电极。

[0062]

如上所述,光接收元件100a沿着与soi基板的box 102下的硅基板101的主面垂直的方向形成,以对波长800nm至1000nm左右的近红外光具有充分的灵敏度的方式选择硅基板101的杂质浓度与其膜厚,所述soi基板包括硅基板101、形成于所述硅基板上的box 102及形成于所述埋入氧化膜(box)102上的半导体层(soi层)107。检测光电流的mos晶体管110a形成于soi层107,为如图8所示的周知的ldd构造的mosfet。

[0063]

作为硅基板101的杂质浓度,为1

×

10

12

/cm3至1

×

10

14

/cm3的范围,优选为选择为2

×

10

12

/cm3。关于硅基板101的厚度,以成为光接收元件100a可完全空乏化的硅厚度、例如最终晶片厚度为300μm至700μm、优选为500μm的方式进行选择。将背面的硅蚀刻去除,其后,对背面离子布植磷(p),为了活化而从背面进行激光照射(激光退火),由此在背面形成n

+

层103。

[0064]

形成所述n

+

层103是为了避免空乏层从主面延伸而到达背面最下部,且为了在像素阵列整体充分降低背面电阻。

[0065]

控制电路部300对传感器电路部100进行控制,包括垂直移位暂存器310、噪声消除器320、列模拟数字转换器(column analog

‑

to

‑

digital converter,column adc)330、水平移位暂存器340,配置于传感器电路部的周边。

[0066]

再者,控制电路部300与本发明并无直接关联,因此省略对其结构或构造的说明。

[0067]

作为高电压产生电路部200的一例,以图5所示的使用电容器(capacitor)(c1~c9)与二极管(d1~d9)的电荷泵电路的形式构成。再者,图7表示图5所示的电荷泵电路的一

部分,形成于soi层107,经二极管连接的两个mos晶体管110b、mos晶体管110c分别对应于图5所示的二极管d8、二极管d9。

[0068]

又,金属

‑

绝缘体

‑

金属(metal

‑

insulator

‑

metal,mim)电容器(capacitor)111对应于电容器(capacitor)c8,box电容器(capacitor)112对应于电容器(capacitor)c9。省略图5所示的其他二极管(d1~d7)或电容器(capacitor)(c1~c7)的图示。经二极管连接而构成的两个mos晶体管110b、mos晶体管110c的构造与mos晶体管110a同样地为图8所示的周知的ldd构造的mosfet。

[0069]

图5所示的高电压产生电路部200所产生的高电压vo(5)经由未图示的金属配线层而供给至设置于传感器电路部100的周边的硅基板101的下层的n

+

层103,将硅基板101整体保持为高电压,从光接收元件部100a内的p

+

扩散层105向硅基板101的背面,在硅基板101内形成充分厚度的空乏层。

[0070]

电容器(capacitor)111(c8)是以mim电容器(capacitor)的形式形成,所述mim电容器(capacitor)是通过化学气相沉积(chemical vapor deposition,cvd)法将成为绝缘层的sion膜沉积于下层的铝配线109a上,其后,使tin沉积于其上,进行图案化而制成相对电极109b。电容器(capacitor)112(c9)连接于高电压产生电路200的输出端(output),为了使耐受电压大,而使用埋入氧化膜(box)102作为绝缘层,制成将一电极形成于soi层107、将另一电极形成于硅基板101内的p阱层106而成的p

+

扩散层105,若预先选择box的膜厚为100nm至300nm,则具有50v以上的足够高的耐受电压。

[0071]

图5中示出5阶的电荷泵电路作为一例,输出输入时钟的高(high)电平(vcc)的5倍的dc电压。

[0072]

若输入为电源电压vcc的时钟信号,则n阶的电荷泵电路中,其输出电压成为

[0073]

vout(n)=vcc

×

n

‑

vf

×

2(n

‑

1)

···

(1)。

[0074]

此处,vf为经二极管连接的mosfet的阈值电压。

[0075]

如上所述,通过准备适当阶数的电荷泵电路,可使电源电压vcc产生所需的高电压(例如10v至60v)。

[0076]

在图5所示的电路中,各阶的电位差vdiff成为

[0077]

vdiff=vcc

‑

2vf

···

(2),

[0078]

因此仅可对各二极管d1~二极管d9的两端子间施加vcc以下的电压。

[0079]

然而,在如通常的大型集成电路(large scale integration,lsi)那样在块体(硅基板)形成mosfet的情形时,由于如图9所示那样对后阶的经二极管连接的场效应晶体管(field effect transistor,fet)的漏极接合部直接施加高电压(例如30v)(再者,对栅极(g)与源极(s)间施加阈值电压(1.8v)),因此为了使pn接合部能够耐受所述高电压,必须采取使接合倾斜而松弛电场等措施,需要追加工艺而变得复杂,并且导致mosfet的面积增大。

[0080]

与此相对,在本发明中,成为二极管的mosfet如图10所示那样互相分离为埋入氧化膜(box)上的半导体层而形成,因此各阶的二极管被完全分离,有可耐受电源电压vcc的耐受电压即可,即便为高电压产生电路,也可使用可在通常的电源电压vcc下运行的mosfet。

[0081]

又,对电容器(capacitor)c1~电容器(capacitor)c8也仅可施加vcc以下的电压,因此可使用如图7所示的mim电容器(capacitor)111。

[0082]

但由于对输出电压稳定用的电容器(capacitor)c9直接施加高电压,因此必须确保电容器(capacitor)的耐受电压。在本发明中,使用100nm~300nm厚度的box 102来确保充分的耐受电压。

[0083]

再者,在图7所示的高电压产生电路部200中,所输出的高电压被连接于光接收元件100a的pn接合电容器(capacitor)单侧的端子(n

+

层103),因此也可省略电容器(capacitor)c9。

[0084]

如上所述,通过将低杂质浓度的soi基板与在soi基板的半导体层中构成电荷泵电路的高电压产生电路加以组合,而可制作在单一电源下工艺或面积的增加也得以抑制的高灵敏度的近红外传感器。

[0085]

继而,参照图11~图17对本发明的光传感器1000的第一实施形态的高电压产生电路部200的制造步骤进行说明。

[0086]

首先,如图11的(a)所示,作为引发材料(starting material),准备如下硅基板,所述硅基板在杂质浓度处于1

×

10

12

/cm3至1

×

10

14

/cm3的范围内的n型磷掺杂的低浓度硅基板501上包括100nm至300nm的埋入氧化膜(box)502,且在其上包括膜厚处于10nm至100nm的范围内的杂质浓度约为1

×

10

15

/cm3的硼掺杂的薄的硅层(soi层)503。

[0087]

此种规格的硅基板是通过公知的智能切离(smart cut)法或贴合法所制造,由晶片供应商所供给。

[0088]

继而,如图11的(b)所示,通过使用光阻的光刻术及以所述光阻作为光掩模的硅(si)的干式蚀刻将soi层503图案化,形成活性区域。

[0089]

再者,图中左侧形成n通道mosfet,右侧形成p通道mosfet。

[0090]

继而,如图11的(c)所示,进行元件分离。使用作为周知的元件分离技术的浅沟槽隔离(shallow trench isolation,sti),以元件分离氧化膜504填埋活性的soi层503间。

[0091]

继而,如图11的(d)所示,使用光刻术及以光阻作为光掩模的离子布植技术,在n通道mosfet侧的soi层503a的上层掺杂硼(bf

2+

),在p通道mosfet侧的soi层503b的上层掺杂磷(p

+

),以分别成为所需阈值的方式,在所需的掺杂量、能量下进行离子布植。

[0092]

继而,如图12的(e)所示,以通过光刻术制成的光阻图案505作为光掩模,将硼(b

+

)布植于下层的硅基板501,形成低浓度的p阱(well)层506。此时,由于仅对处于上层的soi层503a、soi层503b布植少许硼,因此其杂质浓度几乎不变。离子布植后去除光阻图案505。

[0093]

继而,如图12的(f)所示,通过热氧化,在soi层503a、soi层503b的上层形成栅极氧化膜(硅氧化膜)507。

[0094]

继而,如图12的(g)所示,通过cvd(chemical vapor deposition)使成为栅极电极的多晶硅沉积于表面整个面,通过光刻术及以光阻作为光掩模的干式蚀刻,形成包含多晶硅的栅极电极508。

[0095]

继而,如图12的(h)所示,为了形成与下层的硅基板501的触点,而通过光刻术及以光阻作为光掩模的干式蚀刻去除处于触点部的元件分离氧化膜504及埋入氧化膜502,形成box窗。

[0096]

继而,如图13的(i)所示,通过通常的光刻术及以光阻作为光掩模的硼(b

+

)的离子布植,形成成为传感节点的p

+

层509。离子布植后去除光阻。

[0097]

继而,如图13的(j)所示,通过光刻术及以栅极电极508作为光掩模的离子布植,在

n通道mosfet侧形成布植有砷(as)的源极/漏极n

+

层510,在p通道mosfet侧形成布植有硼(bf2)的源极/漏极p

+

层511。再者,通过利用周知的方法在栅极电极508形成侧壁(sw),而在源极/漏极n

+

层的内侧形成n

‑

层,在源极/漏极p+[p

+

]层的内侧形成p

‑

[p

‑

]层,而可制成ldd类型的mosfet。

[0098]

为了包括传感节点p

+

层509在内的这些扩散层(源极/漏极n

+

层510及源极/漏极p

+

层511)中的杂质的活化,而在高温(1,000℃左右)下在氮气(n2)氛围中进行10秒左右的热处理(退火)。

[0099]

继而,如图13的(k)所示,通过cvd整面地沉积层间绝缘(硅氧化膜)512,为了使表面平坦而进行化学机械研磨(chemical

‑

mechanical polish,cmp)。

[0100]

其后,如图13的(l)所示,通过光刻术及以光阻作为光掩模的干式蚀刻,在层间绝缘膜形成元件间的电性连接用的触点孔。

[0101]

继而,如图14的(m)所示,为了以导电物将触点内填埋,而通过cvd积埋未图示的位障金属(ti/tin)、钨(w),其后,通过cmp去除层间绝缘膜512上部的w及ti/tin,形成金属绝缘体(metal

‑

insulator,mi)钨插栓513。

[0102]

继而,如图14的(n)所示,依序溅射ti/tin/al

‑

cu/ti/tin,通过光刻术及以光阻作为光掩模的干式蚀刻,形成m1配线514。此后,重复进行未图示的绝缘膜的沉积、平坦化(cmp)、导孔形成、插栓埋入、配线层的形成图案化,由此可在层间绝缘膜512的上层形成多个m1配线514。

[0103]

继而,如图15的(o)所示,于在连接于m2钨插栓516的第二层m2配线517上形成mim电容器(capacitor)的情形时,在m2配线517的图案化后,通过cvd在m2配线517上沉积成为电容器(capacitor)的绝缘膜的sion膜,其后,溅射成为电容器(capacitor)的相对电极的包含tin的mim电极519,并进行图案化,由此形成mim电容器(capacitor)。

[0104]

继而,如图16的(p)所示,在整个面沉积m2

‑

m3层绝缘膜520,在触点孔内溅射m3钨插栓,重复与图14的(n)、图15的(o)所说明者同样的工艺,形成m3配线522,在钝化膜523设置所需的开口,形成接合垫,由此结束表面处理。

[0105]

最后,为了使传感器可完全空乏化,而以最终晶片厚度成为300μm至700μm的方式,研磨硅基板501的背面,通过湿式蚀刻去除损伤层。其后,将磷离子布植于背面,为了活化,从背面以激光退火进行,其后,在硅基板501的背面形成n

+

层524。

[0106]

再者,在第一实施形态中,高电压产生电路200所使用的二极管(d1~d9)是对于图13的(j)中所形成的n通道mosfet,如图10所示那样将漏极(d)与栅极(g)连接而使用。

[0107]

在本发明的第二实施形态中,如图18所示,在埋入氧化膜(box)502上的半导体层即soi层603形成隔着通道区域603a互相相接的第一区域603b与第二区域603c,在通道区域603a上包括隔着栅极氧化膜607形成的栅极电极608,第一区域603b与通道区域603a具有互相相同的导电型,第二区域603c与通道区域603a具有互不相同的导电型,将栅极电极608与第二区域603c连接,使用隔着通道区域603a的第一区域603b与第二区域603c作为二极管(d1~d9)。

[0108]

如图18所示的二极管与图10所示的soi

‑

mosfet的构造大致等同,图11至图17所说明的流程本身几乎不变。

[0109]

即,仅为图11的(d)中在soi层503a、soi层503b这两层中掺杂磷(p

+

),图13的(j)中

将右侧的p通道mosfet的源极(s)从p

+

/p

‑

层变更为n

+

/n

‑

层,在向源极及漏极进行离子布植时,在栅极508的正中央以光阻作为光掩模,如图19所示那样将砷(as

+

)与硼(bf

2+

)分开,即可制作如图18所示的二极管。

[0110]

图20是表示对从背面向如图7所示的光接收元件100a照射光时的相对于光波长的量子效率进行测定所获得的结果的图。再者,对pn接合施加的反向偏压为30v。

[0111]

与非专利文献1所示的传感器相比,可知本发明的传感器对于900nm~1,000nm的光波长的近红外光可获得非常高的量子效率。

[0112]

继而,关于电荷泵内的soi构造所使用的三种二极管,对反向偏压时的漏电流进行考察。

[0113]

其原因在于:若漏电流增加,则电荷泵电路的升压效果变差,为了升压至所需的电压,必须增加二极管与电容器(capacitor)的组的阶数,会导致面积变大的异常。

[0114]

图21是将三种二极管的构造加以比较而表示者,(a)是专利文献2所记载的二极管,(b)是将mosfet进行二极管连接所构成者,在本发明的第一实施形态中使用(参照图10),(c)是在本发明的第二实施形态中所使用者(参照图18)。

[0115]

(a)所示构造的二极管在构造及工艺方面,箭头所示的面容易受到工艺损伤,并且也无法进行氧化以降低表面能级。因此,界面能级多,在反向偏压时空乏层与所述界面接触,因此存在介由界面能级的表面复合电流流动而漏电流增加的缺陷。

[0116]

(b)所示构造的二极管在通道区域上形成了栅极氧化膜,因此表面能级与(a)相比较少。然而,存在所谓栅极引发漏极漏电流(gate induced drain leakage,gidl)导致反向偏压时的漏电流增加的缺陷。

[0117]

(c)所示构造的二极管中soi的硅表面与氧化膜的界面中形成空乏层的部位为栅极氧化膜的部位,因此为良好的界面,界面能级少,因此介由能级的漏电流被抑制。

[0118]

在施加反向偏压时,n

+

/n

‑

/n部分虽然存在发生gidl的可能性,但由于成为n

+

/n

‑

/n的构造,因此空乏层容易横向扩展,可充分松弛横向电场。因此,gidl的产生量被充分抑制。

[0119]

图22是表示图21所示的三个二极管构造中的反向偏压与漏电流的关系的图。

[0120]

将反向偏压设为

‑

1.8v,使用图21的(c)所示的二极管,由此漏电流成为测定极限以下,与图21的(a)所示的二极管相比,可将漏电流减少约两个数量级以上。

[0121]

[符号的说明]

[0122]

501:低浓度硅基板

[0123]

502:埋入氧化膜

[0124]

503:soi层

[0125]

504:元件分离氧化膜

[0126]

505:光阻图案

[0127]

506:p阱层

[0128]

507:栅极氧化膜

[0129]

508:闸极电极

[0130]

509:传感节点p

+

层

[0131]

510:源极/漏极n

+

层

[0132]

511:源极/漏极p

+

层

[0133]

512:层间绝缘膜

[0134]

513:m1钨插栓

[0135]

514:m1配线

[0136]

515:m1

‑

m2层间绝缘膜

[0137]

516:m2钨插栓

[0138]

517:m2配线

[0139]

518:mim绝缘膜

[0140]

519:mim电极

[0141]

520:m2

‑

m3层间绝缘膜

[0142]

521:m3钨插栓

[0143]

522:m3配线

[0144]

523:钝化膜

[0145]

524:背面n

+

层

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1