显示面板及其制备方法与流程

1.本发明涉及显示技术领域,特别是一种显示面板及其制备方法。

背景技术:

2.如图1所示,oled(organic light

‑

emitting diode,有机电发光显示)/microled作为电流驱动器件,其需要较大的电流通过能力、较好的器件稳定性、面内 vth均匀性及低漏电流等特性。顶栅自对准氧化物半导体薄膜晶体管(top gateigzo tft)具有较高的迁移率、较小寄生电容和低漏电流的特性,比较适合作为电流驱动显示电路。对于底发射类显示基板而言,驱动薄膜晶体管的底部最好带有光阻挡层,光阻挡层可以阻挡环境光对薄膜晶体管的特性影响,金属类的遮光层连接到源极之后对驱动薄膜晶体管的输出特性曲线有稳定作用。如图1以及图2所示,现有的技术中,带有遮光层的tg igzo tft最少需要8道mask,制程顺序依次是遮光层(line shied layer,ls)、缓冲层(buffer)、半导体层(indiumgallium zinc oxide,igzo)、栅极绝缘层(gate insulator,gi)以及栅极(gateelectrode,ge)、绝缘层(interlayer dielectric,ild)、源漏极金属电极(se, de)、钝化层(passivation layer,pv1)以及像素电极(pixel electrode,pe)该制程需要8张掩膜板,制程较为复杂,成本较高。同时,随着显示器的发展,越来越多的顶部出光的自发光类显示成为主流,对于tft的遮光也有新的要求。

技术实现要素:

3.本发明提供一种显示面板,通过将第一源漏电极层与第二源漏电极层共用一层金属膜层,去掉传统的栅极顶部ild层,可以优化膜层结构,减少膜层及掩膜板使用数量。

4.本发明提供一种显示面板,包括:基板;第一金属层,设于所述基板上,所述第一金属层包括:第一源漏电极层以及第二源漏电极层,所述第一源漏电极层与所述第二源漏电极层具有一间隙;第一绝缘层,设于所述第一金属层以及所述基板上;半导体层,设于所述第一绝缘层以及所述第一金属层上,所述半导体层包括第一半导体层以及第二半导体层,所述第一半导体层连接所述第一源漏电极层,所述第二半导体层连接所述第二源漏电极层;第二绝缘层,设于所述第一金属层以及所述半导体层上;第二金属层,设于所述第二绝缘层上,所述第二金属层包括第一栅极层以及第二栅极层;钝化层,设于所述第二金属层、所述半导体层以及所述基板上;以及像素电极,设于所述钝化层上,所述像素电极连接所述第一源漏电极层。

5.进一步地,所述第一源漏电极层与所述第二源漏电极层由同一金属层图案化得到。

6.进一步地,所述第一半导体层与所述第二半导体层由同一有源层图案化得到。

7.进一步地,所述第一栅极层与所述第二栅极层由同一金属层图案化得到。

8.进一步地,所述第一源漏电极层包括:第一源极以及第一漏极,所述第一源极与所述第一漏极之间具有第一间隙;所述第二源漏电极层包括第二源极以及第二漏级;所述第

二源极与所述第二漏级之间具有一第二间隙,所述第二源极设于所述第二漏级与所述第一源极之间,所述第二源极与所述第一源极之间具有一第三间隙;所述第一半导体层包括第一沟道区、第一源极连接区以及第一漏级连接区,所述第一源极连接区的一端连接所述第一沟道区的一端,所述第一漏级连接区的一端连接所述第一沟道区的另一端,所述第一源极连接区的另一端连接所述第一源极,所述第一漏级连接区的另一端连接所述第一漏极;所述第二半导体层包括第二沟道区、第二源极连接区以及第二漏级连接区,所述第二源极连接区的一端连接所述第二沟道区的一端,所述第二漏级连接区的一端连接所述第二沟道区的另一端,所述第二源极连接区的另一端连接所述第二源极,所述第二漏级连接区的另一端连接所述第二漏极。

9.进一步地,所述第一绝缘层包括:第一子绝缘层,设于部分所述第一源极上延伸并覆盖所述第一间隙以及部分所述第一漏级;第二子绝缘层,设于所述第二间隙所对应的基板上,所述第二子绝缘层的一端与所述第二源极具有第一间隔,所述第二子绝缘层的另一端与所述第二漏极具有第二间隔;以及第三子绝缘层,设于所述第三间隙中并覆盖部分所述第一源漏电极层以及部分所述第二源极;所述第一沟道区设于所述第一子绝缘层上,所述第一源极连接区通过所述第一子绝缘层的左侧延伸连接至所述第一源极上,所述第一漏级连接区通过所述第一子绝缘层的右侧延伸至所述第一漏极上;所述第二沟道区设于所述第二子绝缘层上,所述第二源极连接区通过所述第二子绝缘层的左侧以及所述第一间隔延伸至所述第二源极上;所述第二漏级连接通过所述第二子绝缘层的右侧以及所述第二间隔延伸至所述第二漏极上。

10.进一步地,所述第二绝缘层包括:第一栅极绝缘层,设于所述第一半导体层上;第二栅极绝缘层,设于所述第二半导体层上;以及第三栅极绝缘层,设于所述第一源极上;所述第二金属层还包括:电极层;所述第一栅极层设于所述第一栅极绝缘层上;所述第二栅极层设于所述第二栅极绝缘层上;以及所述电极层设于所述第三栅极绝缘层上,所述电极层、所述第三栅极绝缘层以及所述第一源极形成一存储电容。

11.进一步地,所述的显示面板还包括:第一金属线;第二金属线,所述第一金属线以及所述第二金属线分别设于所述钝化层上,所述第一金属线、所述第二金属线与所述像素电极同层设置;以及vdd电源走线,设于所述第一金属层中;其中,所述第一金属线的一端贯穿所述钝化层连接所述第一栅极层,所述第一金属线的另一端连接所述第二源漏极层;所述第二金属线的一端贯穿所述钝化层连接所述第一半导体层,所述第二金属线的另一端连接所述vdd电源走线。

12.本发明另一目的提供一种显示面板的制备方法,包括:提供一基板;形成一第一金属层于所述基板上,所述第一金属层包括:第一源漏电极层以及第二源漏电极层,所述第一源漏电极层与所述第二源漏电极层设有一间隙;形成一第一绝缘层于所述第一金属层以及所述基板上;形成一半导体层于所述第一绝缘层以及所述第一金属层上,所述半导体层包括第一半导体层以及第二半导体层,所述第一半导体层的连接所述第一源漏电极层,所述第二半导体层连接所述第二源漏电极层;形成一第二绝缘层于所述第一金属层以及所述半导体层上;形成一第二金属层于所述第二绝缘层上,所述第二金属层包括第一栅极层以及第二栅极层,所述第一栅极层连接所述第二栅极层;形成一钝化层于所述第二金属层、所述半导体层以及所述基板上;以及形成一像素电极于所述钝化层上,所述像素电极连接所述

第一源漏电极层。

13.进一步地,在所述形成一第一金属层于所述基板上的步骤中,具体包括如下步骤:沉积第一金属材料于所述基板上,以及通过同一光罩图案化得到所述第一源漏电极层以及所述第二源漏电极层;在所述形成一半导体层于所述第一绝缘层以及所述第一金属层上的步骤中,具体包括如下步骤:沉积一有源层材料于所述第一绝缘层以及所述第一金属层上;通过同一光罩图案化得到所述第一半导体层与所述第二半导体层。

14.本发明的有益效果是:本发明提出一种显示面板及其制备方法,通过将第一源漏电极层与第二源漏电极层共用一层金属膜层,将第一源极当做遮光层,并去掉传统的栅极顶部ild层,可以减少膜层及掩膜板使用数量。该结构有利于降低掩膜板数量、缩小薄膜晶体管尺寸以及稳定器件特性优点。本发明的制备方法只需要6道光罩掩膜板工序,大大的减小制备成本。

附图说明

15.下面结合附图和实施例对本发明作进一步的描述。

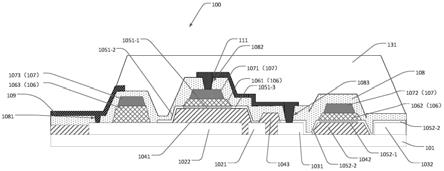

16.图1为现有技术的显示面板的剖面图;

17.图2为本发明提供的显示面板的第一剖面图;

18.图3为本发明提供的显示面板的第二剖面图;

19.图4为本发明提供的显示面板的平面图;

20.图5为本发明提供的显示面板的等效电路图;

21.图6为本发明提供的显示面板的制备方法的步骤s1的示意图;

22.图7为本发明提供的显示面板的制备方法的步骤s2的示意图;

23.图8为本发明提供的显示面板的制备方法的步骤s3的示意图;

24.图9为本发明提供的显示面板的制备方法的步骤s4的示意图;

25.图10为本发明提供的显示面板的制备方法的步骤s5的示意图;

26.图11为本发明提供的显示面板的制备方法的步骤s6的示意图;

27.图12为本发明提供的显示面板的制备方法的步骤s7的示意图;

28.图13为本发明提供的显示面板的制备方法的步骤s8的示意图。

具体实施方式

29.为了更好地理解本发明的内容,下面通过具体的实施例对本发明作进一步说明,但本发明的实施和保护范围不限于此。

30.以下实施例的说明是参考附加的图式,用以例示本发明可用以实施的特定实施例。本发明所提到的方向用语,例如「上」、「下」、「前」、「后」、「左」、「右」、「顶」、「底」等,仅是参考附加图式的方向。因此,使用的方向用语是用以说明及理解本发明,而非用以限制本发明。

31.如图2所示,本发明提供一种显示面板100,包括:基板101、第一金属层110、第一绝缘层104、半导体层105、第二绝缘层106、第二金属层107、钝化层108以及像素电极109。

32.如图2以及图7所示,所述第一金属层110设于所述基板101。所述第一金属层110包括:第一源漏电极层102以及第二源漏电极层103。

33.所述第一源漏电极层102与所述第二源漏电极层103间隔设置。所述第一源漏电极层102包括:第一源极1022以及第一漏极1021,所述第一源极1022 与所述第一漏极1021之间具有第一间隙201。所述第二源漏电极层103包括第二源极1031以及第二漏级1032;所述第二源极1031与所述第二漏级1032 之间具有一第二间隙202,所述第二源极1031设于所述第二漏级1032与所述第一源漏电极层1021之间,所述第二源极1031与所述第一源漏电极层1021 之间具有一第三间隙203。

34.本实施例中的第一源极1022作为遮光层,所述第一源漏电极层102与所述第二源漏电极层103同层设置。所述第二源漏电极层103与所述第一源漏电极层102是通过一道光罩形成。所述第一源漏电极层102、所述第二源漏电极层103所用的材料相同,该材料包括mo(钼)、cunb(铌铜化合物)或tialti (铝钛化合物)。进一步地,该材料也可为叠层结构,所述叠层结构包括: mo/al(铝)、mo/cu(铜)、moti(钼钛化合物)/cu、moti/cu/moti、ti/cu/ti、 mo/cu/izo(铟锌氧化物)、izo/cu/izo或、mo/cu/ito(氧化铟锡)、ni(镍) /cu/ni、motini(钼钛镍化合物)/cu/motini、moni(钼镍化合物)/cu/moni、 nicr(铬镍化合物)/cu/nicr、tini(钛镍化合物)/cu/tini或(钛铬化合物) ticr/cu/ticr。本发明的a/b结构,即是一叠层结构,a表示其中一层结构所用的金属材料,b表示另一层结构所用的金属材料,a与b的上下关系并没有限定。

35.如图2以及图8所示,所述第一绝缘层104设于所述第一金属层110以及所述基板101上。所述第一绝缘层104包括:第一子绝缘层1041、第二子绝缘层1042以及第三子绝缘层1043。

36.所述第一子绝缘层1041设于部分所述第一源极1022上延伸并覆盖所述第一间隙201以及部分所述第一漏级上1021。第二子绝缘层1042设于所述第二间隙302所对应的基板101上,所述第二子绝缘层302的一端与所述第一源极 1031具有第一间隔304,所述第二子绝缘层1042的另一端与所述第一漏极1032 具有第二间隔305;所述第三子绝缘层1043设于所述第三间隙303中并覆盖部分所述第一源漏电极层1021以及部分所述源极1031。所述第一绝缘层104 的膜层材料包括siox,sinx,sinox等。

37.继续参照图2所示,所述半导体层105设于所述第一绝缘层104以及所述第一金属层110上,所述半导体105层包括第一半导体层1051以及第二半导体层1052,所述第一半导体层1051连接所述第一源漏电极层102,所述第二半导体层1052连接所述第二源漏电极层103。所述第一半导体层1051包括第一沟道区1051

‑

1、第一源极连接区1051

‑

2以及第一漏级连接区1051

‑

3,所述第一源极连接区1051

‑

2的一端连接所述第一沟道区1051

‑

1的一端,所述第一漏级连接区1051

‑

3的一端连接所述第一沟道区1051

‑

1的另一端,所述第一源极连接区1051

‑

2的另一端连接所述第一源极1022,所述第一漏级连接区1051

‑

3 的另一端连接所述第一漏极1021;所述第二半导体层1052包括第二沟道区 1052

‑

1、第二源极连接区1052

‑

2以及第二漏级连接区1052

‑

3,所述第二源极连接区1052

‑

2的一端连接所述第二沟道区1052

‑

1的一端,所述第二漏级连接区1052

‑

3的一端连接所述第二沟道区1052

‑

1的另一端,所述第二源极连接区 1052

‑

2的另一端连接所述第二源极1031,所述第二漏级连接区1052

‑

3的另一端连接所述第二漏极1032。

38.所述第一沟道区1051

‑

1设于所述第一子绝缘层1041上,所述第一源极连接区1051

‑

2通过所述第一子绝缘层1041的左侧延伸至所述第一源极1022的上,所述第一漏级连

接区1051

‑

3通过所述第一子绝缘层1041的右侧延伸至所述第一漏极1021的上;所述第二沟道区1052

‑

1设于所述第二子绝缘层1042上,所述第二源极连接区1052

‑

2通过所述第二子绝缘层1042的左侧以及所述第一间隔304延伸至所述源极1031上;所述第二漏级连接区1052

‑

3通过所述第二子绝缘层1042的右侧以及所述第二间隔305延伸至所述第二漏极1032上。

39.所述半导体层105的材料包括为氧化物半导体或其他类型半导体,所述氧化物半导体的材料包括igzo(铟镓锌氧化物)、igto(铟镓钛氧化物)、igzto (铟镓锌钛氧化物)、igo(铟镓氧化物)、izo(铟锌氧化物)或aizo(铝锌氧化物)。

40.所述第二绝缘层106设于所述第一金属层102以及所述半导体层105上。所述第二绝缘层106包括:第一栅极绝缘层1061、第二栅极绝缘层1062以及第三栅极绝缘层1063。

41.所述第一栅极绝缘层1061设于所述第一半导体层1051上;所述第二栅极绝缘层1062设于所述第二半导体层1052上。所述第三栅极绝缘层1063设于所述第一源极1022上。

42.所述第二绝缘层106的膜层材料包括sio

x

(氧化硅)或sin

x

(氮化硅)。所述第二绝缘层106还可为叠层结构,所述叠层结构的材料包括: al2o3/sin

x

/sio

x

或sio

x

/sin

x

/sio

x

。

43.所述第二金属层107设于所述第二绝缘层106上,所述第二金属107层包括第一栅极层1071、第二栅极层1072以及电极层1073。

44.所述第一栅极层1071设于所述第一栅极绝缘层1061上;所述第二栅极层 1072设于所述第二栅极绝缘层1032上;所述电极层1073设于所述第三栅极绝缘层1063上,所述电极层1073、所述第三栅极绝缘层1063以及所述第一源极1022形成一存储电容。所述第一栅极层1071、所述第一半导体层1051 以及所述第一源漏极层1021组成一驱动薄膜晶体管。所述第二栅极层1072、所述第二半导体层1052以及所述第二源漏极层103组成一开关薄膜晶体管。

45.所述第二金属层107的材料包括mo(钼)、cunb(铌铜化合物)或tialti (铝钛化合物)。所述栅极层107可为一叠层结构,所述叠层结构包括:mo/al (铝)、mo/cu(铜)、moti(钼钛化合物)/cu、moti/cu/moti、ti/cu/ti、 mo/cu/izo(铟锌氧化物)、izo/cu/izo或、mo/cu/ito(氧化铟锡)、ni(镍) /cu/ni、motini(钼钛镍化合物)/cu/motini、moni(钼镍化合物)/cu/moni、 nicr(铬镍化合物)/cu/nicr、tini(钛镍化合物)/cu/tini或(钛铬化合物) ticr/cu/ticr。

46.所述钝化层108设于所述第二金属层107、所述半导体层105以及所述基板101上。所述钝化层108设有第一通孔1081、设有第二通孔1082、第三通孔1083、第四通孔1084以及第五通孔1085。

47.所述第一通孔1081向下延伸至所述第一源极1022的上表面。所述第二通孔1082向下延伸至所述第一栅极子层1071的上表面。所述第三通孔1083向下延伸至所述第二源漏电极层103的源极1031的上表面,所述钝化层108。所述第四通孔1084向下延伸至所述第一半导体层1052的上表面,所述第五通孔1085向下延伸至vdd电源走线121的上表面。

48.所述钝化层108的膜层材料包括sio

x

(氧化硅)、sin

x

(氮化硅)或sino

x

(氮氧化硅)。所述钝化层108还可为叠层结构,所述叠层结构的材料包括: sio

x

/sin

x

。

49.所述像素电极109设于所述钝化层108上,所述像素电极109连接所述第一源极1022,并通过所述第一源极1022连接驱动薄膜晶体管的第一半导体层 1051。所述像素电极109通过所述第一通孔1081连接所述第一源极1022。

50.所述像素电极109的材料包括:ito、izo、或金属类的膜层。所述像素电极109还可为叠层结构,所述叠层结构包括:mo/al(铝)、mo/cu(铜)、 moti(钼钛化合物)/cu、moti/cu/moti、ti/cu/ti、mo/cu/izo(铟锌氧化物)、izo/cu/izo或、mo/cu/ito(氧化铟锡)、ni(镍)/cu/ni、motini (钼钛镍化合物)/cu/motini、moni(钼镍化合物)/cu/moni、nicr(铬镍化合物)/cu/nicr、tini(钛镍化合物)/cu/tini或(钛铬化合物)ticr/cu/ticr。

51.同时参照图2以及图3所示,在一实施例中,所述显示面板100还包括:第一金属线111、第二金属线114以及所述vdd电源走线121。

52.所述第一金属线111以及所述第二金属线114分别设于所述钝化层108 上,所述第一金属线111、所述第二金属线114与所述像素电极109同层设置。所述第一金属线111、所述第二金属线114与所述像素电极109由一道光罩工艺制备形成,其材料皆为氧化铟锡。所述vdd电源走线121与所述第一源极1022同层设置于所述基板101上。

53.所述第一金属线111的一端通过所述第二通孔1082连接所述第一栅极层 1071。所述第一金属线111的另一端通过所述第三通孔1083连接所述源极 1031,进而完成驱动薄膜晶体管与开关薄膜晶体管的连接。所述第二金属线 114的一端通过所述第四通孔1084连接所述第一半导体层1052。,所述第二金属线114的另一端通过所述第五通孔1085连接所述vdd电源走线121。

54.本发明提出一种显示面板100,所述显示面板100应用于顶栅自对准结构金属氧化物薄膜晶体管的,只需要6道光罩掩膜板工序,依次流程为第一金属层(第一源漏电极层(第一源极可作为遮光层)以及第二源漏极层)、第一绝缘层、半导体层(第一半导体层及第二半导体层)、第二绝缘层及栅极层(第一栅极绝缘层及第一栅极、第二栅极绝缘层及第二栅极)、钝化层以及像素电极层。

55.本发明通过将第一源漏电极层102及第二源漏电极层103共用一层金属膜层,并去掉传统的栅极顶部ild层,通过这个结构优化可以减少膜层及掩膜板使用数量。该结构有利于降低掩膜板数量、缩小薄膜晶体管尺寸以及稳定器件特性优点。

56.本发明的半导体层105、第一栅极层1071、源漏极层连接方式存在三种,第一种是驱动薄膜晶体管中第一栅极层1071与开关薄膜晶体管中的源极1031 通过第一金属线111形成连接;第二种是驱动薄膜晶体管的第一半导体层1051 与第一源漏电极层1021直接连接,第三种是驱动薄膜晶体管的第一半导体层 1051与vdd走线通过第二金属线114相连。

57.如图4所示,具体地,本发明为了更好的理解像素电极109、第一金属线 111及第二金属线114的平面位置关系,提供了一实施例的平面图。其中,图2的第一剖面图为图4结构中的aa’虚线处的剖面,图3的第二剖面图为图4结构中的bb’虚线处的剖面。

58.如图5所示,为本发明等效电路图,该电路包括开关薄膜晶体管t1、驱动薄膜晶体管t2、感应薄膜晶体管t3以及电容c。

59.所述开关薄膜晶体管t1的栅极连接栅极电压信号vgate,所述开关薄膜晶体管t1的源极连接数据电压信号vdata,所述开关薄膜晶体管t1的漏极连接所述电容的第一端。

60.所述驱动薄膜晶体管t3的栅极连接所述开关薄膜晶体管t1的漏极,所述驱动薄膜晶体管t3的漏极连接高电压源vdd,所述驱动薄膜晶体管t3的源极分别连接所述电容c的第二端以及一发光二极管的第一端,所述发光二极管的第二端接地。

61.所述感应薄膜晶体管t3的源极连接所述电容c,所述感应薄膜晶体管t3 的漏极连

接一感应信号sensing。

62.本发明还提供一种显示面板的制备方法,用以制备形成本发明所述的显示面板100,所述显示面板的制备方法包括如下步骤s1~s8。

63.s1)如图6所示,提供一基板101。

64.s2)如图7所示,形成一第一金属层110设于所述基板101。所述第一金属层102包括:第一源漏电极层102以及第二源漏电极层103。所述步骤s2具体包括:s201)沉积第一金属材料于所述基板101上;s202)通过同一张光罩图案化得到所述第一源漏电极层102以及所述第二源漏电极层103。所述第一源漏电极层102与所述第二源漏电极层103间隔设置。所述第一源漏电极层102 包括:第一源极1022以及第一漏极1021,所述第一源极1022与所述第一漏极 1021之间具有第一间隙201。所述第二源漏电极层103包括第二源极1031以及第二漏级1032;所述第二源极1031与所述第二漏级1032之间具有一第二间隙 202,所述第二源极1031设于所述第二漏级1032与所述第一源漏电极层102之间,所述第二源极1031与所述第一源漏电极层102之间具有一第三间隙203。第一金属材料包括mo(钼)、cunb(铌铜化合物)或tialti(铝钛化合物)。第一金属材料也可为叠层结构,所述叠层结构包括:mo/al(铝)、mo/cu(铜)、 moti(钼钛化合物)/cu、moti/cu/moti、ti/cu/ti、mo/cu/izo(铟锌氧化物)、 izo/cu/izo或、mo/cu/ito(氧化铟锡)、ni(镍)/cu/ni、motini(钼钛镍化合物)/cu/motini、moni(钼镍化合物)/cu/moni、nicr(铬镍化合物)/cu/nicr、 tini(钛镍化合物)/cu/tini或(钛铬化合物)ticr/cu/ticr。

65.s3)如图8所示,形成一第一绝缘层104于所述第一金属层110以及所述基板101上,所述第一绝缘层104包括:第一子绝缘层1041、第二子绝缘层1042 以及第三子绝缘层1043。具体地,步骤s3具体包括:s301)沉积一膜层材料于所述第一金属层110以及所述基板101上;s302)通过同一光罩图案化后形成所述第一子绝缘层1041、所述第二子绝缘层1042以及所述第三子绝缘层1043。所述第一子绝缘层1041设于部分所述第一源极1022上延伸并覆盖所述第一间隙 201以及部分所述第一漏级上。第二子绝缘层1042设于所述第二间隙302所对应的基板上,所述第二子绝缘层302的一端与所述第二源极1031具有第一间隔 304,所述第二子绝缘层1042的另一端与所述第二漏极1032具有第二间隔305;所述第三子绝缘层1043设于所述第三间隙303中并覆盖部分所述第一漏极1021 以及部分所述第二源极1031。所述第一绝缘层104的膜层材料包括siox,sinx, sinox等。

66.s4)如图9所示,形成一半导体层105于所述第一绝缘层104以及所述第一金属层102上,所述半导体105层包括第一半导体层1051以及第二半导体层 1052。具体地,步骤s4包括:s401)沉积有源层材料于所述第一绝缘层104以及所述第一金属层102上;s402)通过同一光罩图案化后形成所述第一半导体层1051以及所述第二半导体层1052。所述第一半导体层1051连接所述第一源漏电极层102,所述第二半导体层1052连接所述第二源漏电极层103。所述第一半导体层1051包括第一沟道区1051

‑

1、第一源极连接区1051

‑

2以及第一漏级连接区1051

‑

3,所述半导体材料包括为氧化物半导体或其他类型半导体,所述氧化物半导体的材料包括igzo(铟镓锌氧化物)、igto(铟镓钛氧化物)、igzto (铟镓锌钛氧化物)、igo(铟镓氧化物)、izo(铟锌氧化物)或aizo(铝锌氧化物)。

67.s5)如图10所示,形成一第二绝缘层106于所述第一金属层102以及所述半导体层105上,所述第二绝缘层106包括:第一栅极绝缘层1061、第二栅极绝缘层1062以及第三栅极

绝缘层1063;形成第二金属层107于所述第二绝缘层106上,所述第二金属107层包括第一栅极层1071、第二栅极层1072以及电极层1073。具体地,步骤s5具体包括:s501)沉积一绝缘材料于所述第一金属层102以及所述半导体层105上;s502)沉积一第二金属材料于所述绝缘材料上;s503)通过同一光罩图案化后形成所述第一栅极层1071、所述第二栅极层 1072以及所述电极层1073;s504)根据所述第二金属层107的金属图案自对准图案化后形成所述第一栅极绝缘层1061、所述第二栅极绝缘层1062以及所述第三栅极绝缘层1063。s505)并根据所述第二金属层107的金属图案自对准对所述半导体层105进行金属化掺杂处理分别得到第一沟道区1051

‑

1、第一源极连接区1051

‑

2、第一漏级连接区1051

‑

3、第二沟道区1052

‑

1、第二源极连接区1052

‑

2 以及第二漏级连接区1052

‑

3,所述第一源极连接区1051

‑

2的一端连接所述第一沟道区1051

‑

1的一端,所述第一漏级连接区1051

‑

3的一端连接所述第一沟道区 1051

‑

1的另一端,所述第一源极连接区1051

‑

2的另一端连接所述第一源极1022,所述第一漏级连接区1051

‑

3的另一端连接所述第一漏极1021;所述第二源极连接区1052

‑

2的一端连接所述第二沟道区1052

‑

1的一端,所述第二漏级连接区 1052

‑

3的一端连接所述第二沟道区1052

‑

1的另一端,所述第二源极连接区 1052

‑

2的另一端连接所述第二源极1031,所述第二漏级连接区1052

‑

3的另一端连接所述第二漏极1032。所述第一沟道区1051

‑

1设于所述第一子绝缘层1041 上,所述第一源极连接区1051

‑

2通过所述第一子绝缘层1041的左侧延伸至所述第一源极1022的上,所述第一漏级连接区1051

‑

3通过所述第一子绝缘层1041 的右侧延伸至所述第一漏极1021的上;所述第二沟道区1052

‑

1设于所述第二子绝缘层1042上,所述第二源极连接区1052

‑

2通过所述第二子绝缘层1042的左侧以及所述第一间隔304延伸至所述源极1031上;所述第二漏级连接区1052

‑

3 通过所述第二子绝缘层1042的右侧以及所述第二间隔305并延伸至所述第二漏极1032上。所述第一栅极绝缘层1061设于所述第一半导体层1051上;所述第二栅极绝缘层1062设于所述第二半导体层1052上。所述第三栅极绝缘层1063 设于所述第一源极1022上。所述第二绝缘层106的绝缘材料包括sio

x

(氧化硅)或sin

x

(氮化硅)。所述第二绝缘层106的绝缘材料还可为叠层结构,所述叠层结构的材料包括:al2o3/sin

x

/sio

x

或sio

x

/sin

x

/sio

x

。所述第一栅极层1071 设于所述第一栅极绝缘层1061上;所述第二栅极层1072设于所述第二栅极绝缘层1032上;所述电极层1073设于所述第三栅极绝缘层1063上,所述电极层1073、所述第三栅极绝缘层1063以及所述第一源极1022形成一存储电容。所述第一栅极层1071、所述第一半导体层1051以及所述第一源漏极层1021组成一驱动薄膜晶体管。所述第二栅极层1072、所述第二半导体层1052以及所述第二源漏极层103组成一开关薄膜晶体管。所述第二金属材料包括mo(钼)、cunb(铌铜化合物)或tialti(铝钛化合物)。所述第二金属材料可为一叠层结构,所述叠层结构包括:mo/al(铝)、mo/cu(铜)、moti(钼钛化合物)/cu、moti/cu/moti、 ti/cu/ti、mo/cu/izo(铟锌氧化物)、izo/cu/izo或、mo/cu/ito(氧化铟锡)、 ni(镍)/cu/ni、motini(钼钛镍化合物)/cu/motini、moni(钼镍化合物) /cu/moni、nicr(铬镍化合物)/cu/nicr、tini(钛镍化合物)/cu/tini或(钛铬化合物)ticr/cu/ticr。

68.s6)如图11所示,形成一钝化层108于所述第二金属层107及所述半导体层105以及所述基板101上。具体地,步骤s7具体包括如下步骤s601~s602。 s601)沉积一膜层材料于所述第二金属层107、所述半导体层105以及所述基板 101上形成所述钝化层108。所述钝化层108的膜层材料包括sio

x

(氧化硅)、 sin

x

(氮化硅)或sino

x

(氮氧化硅)。所述钝化层108还

可为叠层结构,所述叠层结构的材料包括:sio

x

/sin

x

。s602、继续参照图11所示,在所述钝化层108 上开设第一通孔1081、第二通孔1082、第三通孔1083。所述第一通孔1081向下延伸至所述第一源极1022的上表面。所述第二通孔1082向下延伸至所述第一栅极子层1071的上表面。所述第三通孔1083向下延伸至所述源漏电极层103 的上表面。

69.s7)参照图12所示,形成一像素电极109于所述钝化层108上,所述像素电极109连接所述第一源极1022。具体地,步骤s8包括:s701)沉积一电极材料于所述钝化层108上;s702)通过同一光罩图案化形成所述像素电极109以及第一金属线111。所述像素电极109通过所述第一通孔1081连接所述第一源极1022。所述第一金属线111的一端通过所述第二通孔1082连接所述第一栅极子层1071,所述第一金属线111的另一端通过所述第三通孔1083连接所述第二源漏电极层103。所述第二金属线114的一端通过所述第四通孔1084连接所述第一半导体层1052。

70.所述电极材料包括:ito、izo、或金属类的膜层。所述像素电极109还可为叠层结构,所述叠层结构包括:mo/al(铝)、mo/cu(铜)、moti(钼钛化合物)/cu、moti/cu/moti、ti/cu/ti、mo/cu/izo(铟锌氧化物)、izo/cu/izo 或、mo/cu/ito(氧化铟锡)、ni(镍)/cu/ni、motini(钼钛镍化合物)/cu/motini、moni(钼镍化合物)/cu/moni、nicr(铬镍化合物)/cu/nicr、tini(钛镍化合物)/cu/tini或(钛铬化合物)ticr/cu/ticr。

71.s8)参照图13所示,沉积一保护层131于所述基板101的上方。

72.本发明提出一种显示面板制备方法,所述显示面板应用于顶栅自对准结构金属氧化物薄膜晶体管的,只需要7道光罩掩膜板工序,依次流程为第一金属层(第一源漏电极层(第一源极作为遮光层)以及第二源漏极层)、第一绝缘层、半导体层(第一半导体层及第二半导体层)、第二绝缘层及栅极层(第一栅极绝缘层及第一栅极、第二栅极绝缘层及第二栅极)、钝化层以及像素电极层。

73.本发明通过将第一源极当作遮光层,去掉传统的栅极顶部ild层,通过这个结构优化可以减少膜层及掩膜板使用数量。该结构有利于降低掩膜板数量、缩小薄膜晶体管尺寸以及稳定器件特性优点。

74.应当指出,对于经充分说明的本发明来说,还可具有多种变换及改型的实施方案,并不局限于上述实施方式的具体实施例。上述实施例仅仅作为本发明的说明,而不是对本发明的限制。总之,本发明的保护范围应包括那些对于本领域普通技术人员来说显而易见的变换或替代以及改型。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1